Устройство для программного управления

Иллюстрации

Показать всеРеферат

Изобретене относится к системам программного управления. Цель изобретения - повышение надежно-.ти устройства и расширение его / жциональ ных возможностей. Устройство для про граммногр управления содержит блок 1 счетчика этапов, блок 2 дешифратора, блок 3 формирователя команд управления , блок 4 контроля и индикации, блок 5 логики, блок 6 гальванических развязок и связи с оператором, блок 7 датчиков положения исполнительных механизмов,блок 8 исполнительных механизмов, блок 9 таймера, блок 10 запрета, блок 11 генератора и блок 12 задержки. Повышение надежности в устройстве достигается тем. Что BTO.-I рой вход блока 1 счетчика этапов соединен с выходом блока 11 генератора , что препятствует срабатыванию блока 1 от сигналов помехи во время отсутствия импульса генератора. Расширение функциональных возможностей устройства достигается тем, что второй выход блока 9 таймера соединен с третьим входом блока 5 логики, а выход блока 10 запрета через блок 12 задержки - с вторым входом блока 5, на третий вход которого, а также на второй вход блока 1 подключен выход блока 1I, что позволяет примекять устройство для программного управления для реализации алгоритмов, в которых есть временные этапы. 8 ил. (Л с: ел со САЭ

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1456933 А1

15И 4 G 05 В 9/l8

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НСМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГННТ СССР I (21) 4190773/24- 24 (22) 02.02.87 (46) 07.02.89. Бюл. % 5 (71) Украинский государственный проектный институт "Тяжпромавтоматика" (72) Л.Б. Фонарев и Ю.А. Черняк (53) 621.503.55(088.8) (56) Авторское свидетельство СССР

Р 877475, кл. G 05 В 19/18„ 1979.

Авторское свидетельство СССР

Р 1238034, кл. G 05 В 19/18, 1985, (54) УСТРОЙСТВО ДЛЯ РОГ РАММНО ГО УП—

РАВ ЛЕН ИЯ (5?) Изобретене относится к системам программного управления. Цель изобре т ения — по выше ние н ад ежив ". ти ус т— ройства и расширение его,.: кциональных возможностей. Устройство для программного управления содержит блок 1 счетчика этапов, блок 2 дешифратора, блок 3 формирователя команд управления, блок 4 контроля и индикации, блок 5 логики, блок 6 гальванических развязок и связи с оператором, блок

7 датчиков положения исполнительных механизмов, блок S исполнительных механизмов, блок 9 таймера, блок 10 запрета, блок 11 генератора и блок

12 задержки. Повышение надежности в устройстве достигается тем, Что вто. рой вход блока 1 счетчика этапов соединен с выходом блока 11 генератора, что препятствует срабатыванию блока 1 от сигналов помехи во время отсутствия импульса генератора. Расширение функциональных возможностей устройства достигается тем, что второй выход блока 9 таймера соединен с третьим входом блока 5 логики, а выход блока 10 запрета через блок 12 задержки — с вторым входом блока 5, на третий вход которого, а также на второй вход блока 1 подключен выход блока 11, что позволяет применять устройство для программного управления для реализации алгоритмов, в которых есть временные этапы. 8 ил.

1456933

Изобретение относится к системам программного управления.

Цель изобретения — повышение на; дежности устройства и расширение его функциональных возможностей.

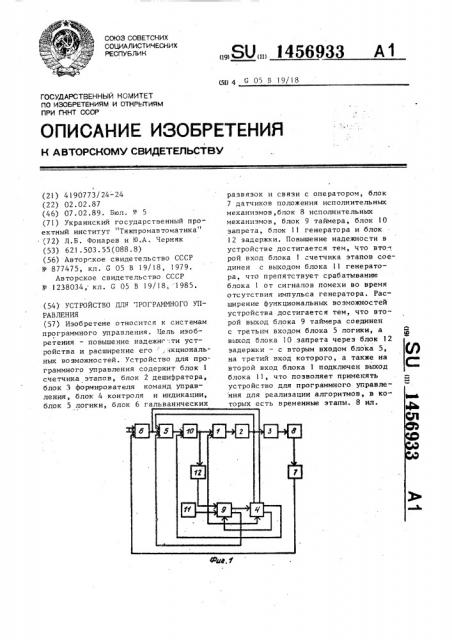

На фиг. I представлена схема устройства для программного управления; на фиг. 2 — вариант выполнения блока контроля и индикации; на фиг.3 - 1О вариант выполнения блока формирователя команд управления; на фиг. 4, вариант выполнения и коммутации бло" ка логики, блока запрета и блока, счетчика этапов; на фиг.5 — диаграм- !5 ма импульсных сигналов на выходах и

1 входах элементов блока счетчика эта- пов и блока логики; на фиг. 6— вариант выполнения блока таймера; . на фиг. 7 — вариант выполнения блока 20 задержки и его временная диаграмма; на фиг.8 — временная диаграмма сигналов на выходе блока дешифратора.

Устройство для программного управления {фиг.1) содержит блок 1 счетчика этапов, блок 2 дешифратора, блок 3 формирователя команд управления, блок 4 контроля и индикации, блок 5 логики, блок 6 гальванических развязок и связи с оператором, блок 30

7 датчиков положения исполнительных механизмов, блок 8 исполнительных механизмов, блок 9 таймера, блок 10 запрета, блок 11 генератора и блок

12 задержки. 35

Блок 4 контроля и индикации содержит (фиг.2) элементы И 13-16, элементы ИЛИ 17-19, инверторы 20-22, элемент ИЛИ 23; светодиоды 24-26, резисторы 27-29 и конденсаторы 30 40 и 3!. Блок 3 формирователя команд управления содержит (фиг.3) элемент

ИЛИ 32, инверторы.33 и 34, одновибратор 35 и элементы И 36 и 37. Блок

5 логики содержит элементы И 38-41 и элемент ИЛИ 42; блок 1 0 запрета— элемент И 43; блок 1 счетчика эта- . пов — элемент И 44, одновибратор 45 и счетчик 46 {фиг.4) ° Блок 9 таймера содержит (фиг.б) счетчики 47-49.

Блок 12 задержки может быть выполнен по схеме (фиг,7) инвертор 50, диод

51, резистор 52, конденсатор 53, резисторы 54 и 55, транзистор 56 и инвертор 57.

Устройство работает следующим образом.

В исходном состоянии на выходе блока 1 счетчика этапов имеется аиг.— нал, соответствующий нулевому (начальному) этапу, дешифрируемому блоком

2 дешифратора (цепи приведения устройства в исходное состояние на схеме не показаны).

По команде оператора {например

"Пуск" ), которая поступает через блок 6 гальванических развязок и

1 связи с оператором, на выходе блока

5 логики формируется сигнал готовности первого этапа, который через блок

10 запрета поступает на первый вход блока 1 счетчика этапов, что приводит к переключению последнего на один шаг (этап) . Это состояние расшифровывается блоком 2 дешифратора как состояние первого шага (этапа) .

Сигнал с выхода блока 5 логики через блок 10 запрета и блок 12 задержки поступает также на второй вход бяока 9 таймера и устанавливает его в исходное состояние, при этом в таймере начинается отсчет времени текущего (первого) этапа. По сигна-: лу этапа с выхода блока 2 дешифратора через блок 3 формирователя команд управления включается исполнительный механизм первого этапа программы в блоке 8 исполнительных механизмов.

После выполнения операций первого этапа на выходе блока 7 датчиков возникает сигнал о выполнении операций первого этапа.

Наличие на втором входе блока 5 логики сигнала о выполнении операции первого этапа (с выхода блока 6) и сигнала этапа (первого) на первом входе, поступающего с выхода блока 2 дешифратора, обеспечивает формирование на выходе блока 5 логики сигнала готовности второго этапа.

Сигнал с выхода блока 5 логики, проходя через блок 10 запрета, переключает блок 1 счетчика этапов на очередной второй) этап. Одновременно по этому сигналу с выхода блока 10 запрета через блок 1 2 задержки происходит обнуление (установка в исход— ное состояние счетчика) блока 9 таймера и начинается отсчет времени очередного этапа (второго), Сигнал с . выхода блока 2 дешифратора включает исполнительный механизм этого этапа в блоке 8 исполнительных механизмов.

Далее процесс повторяется анало.гично. При этом. следует иметь ввиду, что после переключения блока 1 счетчика этапов и блока 2 дешифратора

1456933

35

45 блоке 6 гальванических развязок, ко55 торые должны иметь место на данном этапе, то из-за невозникновения сиг". на очередной этап на выходе блока

5 исчезает сигнал готовности этапа, так как на очередном (вновь возникшем) этапе еще нет подтверждения о выполнении операций этого этапа, т,е. автоматически формируется импульс на переключение блока 1 счетчика. Сигнал готовности формируется в блоке 7 датчиков положения после того, как исполнительные механизмы, управляемые на этом этапе, придут в нужное положение.

Для реализации возможности осуще-, ствления в алгоритме временных этапов, т.е ° этапов,на которых не происходит воздействия на механизмы, а осуществляется выдержка времени, на третий вход блока 5 логики с второго выхода блока 9 таймера вводится сигнал времени соответствующего временного этапа. Готовность следующего этапа в,этом случае формируется при совпадении на соответствующей ячейке И блока 5 логики сигналов этапа и времени, соответствующего длительности этог временного этапа. Но так как этим сигналом готовности (прошедшим через блок 10 запрета) обнуляется блок 9 таймера и при этом исчезает сигнал времени, то длительности сигнала готовности ь .цостаточно для перевода блока 1 счет":ика в следующее состояние. Поскольку блок 9 тай- мера обнулен и готовности нет, то вновь начинается отсчет вп ени — ситуация повторяется и прог1 мма "зави.сает . Для устранения этого явления вводится блок 12 задержки, который задерживает команду (сигнал готовности этапа) на обнуление блока 9 таймера на время, достаточное для перехода блока l счетчика этапов в следующее состояние и не влияющее на время выполнения этапа (время переходных процессов в счетчиках измеряется микросекундами, а время этапов — от нескольких секунд до десятков минут).

Если при выполнении операций какого-либо этапа программы команда на выполнение операции не выполнена за время, установленное для этого этапа, и: не появляется сигнал готовности очередного этапа, который бы обнулил . блок 9 таймера, то достигнуто время этапа, которое не должно быть превышено. При этом под действием сигнала времени этапа, поступающего с блока

9 таймера, на первом выходе блока 4

25 контроля и индикации формируется сигнал превышения времени этапа, который в качестве останова таймера поступает на первый вход блока 9 таймера. Останов таймера необходим для сохранения сигнала, характеризующего время этапа.

Сигнал превышения времени этапа индицируется в блоке 4 светодиодом

24, предупреждая оператора об остановке программы по превышению времени этапа. Программа продолжается только тогда, когда исполнительный механизм принимает нужное положение (устранена причина неисправности и механизм отработал нужную команду от местного или дистанционного управления или установлен в нужное положение вручную) . При этом замыкается нужный конечный выключатель в блоке

7 датчиков положения, и в блоке 5 логики на соответствующем элементе И происходит совпадение сигналов этапа . и положения механизма, в результате чего формируется сигнал готовности очередного этапа, который переводит блок 1 счетчика этапов в следующее состояние и обнуляет блок 9 таймера, вследствие чего исчезают сигнал времени на первом выходе блока 9 тай" мера и, соответственно, сигнал превышения времени этапа в блоке 4 контроля.

Так как время исполнения операций на разных этапах различное, то. каждому сигналу этапа с блока 2 дешифратора соответствует свой сигнал времени от блока 9 таймера. Этим обеспечивается избирательность контроля длительности каждого этапа.

Если операция этапа выполняется за заданное время, не превышающее время этапа, то блок 5 логики через блок 10 запрета воздействует на блок

1 счетчика этапов и блок 2 дешифратора и осуществляется переход к выполнению операций следующего этапа с одновременным обнулением блока 9 таймера.

Если при выполнении операций какого-либо этапа программы исчезают сигналы технологических параметров в нала готовности этапа не наступает очередной этап, в блоке 9 таймера возникает сигнал времени, которое

50

5 14569 не должно быть превышено, в блоке 4 контроля формируется сигнал превышения времени этапа, от которого про-. исходит запрет на продолжение проб граммы. Причина запрета индицируется в блоке 4 контроля светодиодом 25 как несоответствие параметра на данном этапе. Продолжение программы в этом случае возможно только при снятии сигнала запрета, т.е. появлении технологического параметра, при котором формируется сигнал готовности этапа, Если после завершения операции какого-либо этапа устройство переходит в состояние следующего этапа, на котором по технологическим причинам все операции уже выполнены, т.е. на входах блока 5 логики уже есть сигналы С блока 6 гальванических 20 развязок в момент появления сигнала этапа с выхода блока 2 дешифратора, то, если не принять специальных мер,, формируется только один. импульс готоности этапа (имея ввиду и предыду- 2б щий) и программа "зависает". Но в схеме устройства переключение блока 1 счетчика происходит при совпадении сигналов го тов но сти э тапа и импульса блока 11 генератора, поэтому 30 исчезновение импульса блока генератора "разрезает" двойной импульс готовности, на вход блока l счетчика поступают два импульса, и сбоя в работе системы нет.

Зб Из диаграммы импульсных сигналов на выходах элементов блока 1 счетчика этапов и блока 5 логики и счетном входе счетчика 46 блока 1 счетчика этапов (фиг.5) видно, что при наличии 40 сигнала от блока 6 гальванических ! развязок на входе элемента И 41 в момент появления этапа от блока 2

I дешифратора на втором входе элемента

И 41, сигнал на выходе элемента И 41 4б появляется одновременно с исчезновением сигнала предыдущего этапа от блока 2 дешифратора на входе элемента И 40 (и, следовательно, сигнала на выходе элемента И 40);.На выходе элемента ИЛИ 42 блока 5 логики эти два импульса сливаются. Наличие стробирующих импульсов от блока 11 генератора на втором входе блока 1 счетчика этапов устраняет это явление, и на переброс счетчика 46 поступают два последовательных импульса, вследствие чего сбоя системы не происходит.

Кроме того, импульсы блока 11 генератора, подаваемые на второй вход блока 1 счетчика этапов, делают устройство более помеха защищенным, так как счетчик 46 может сработать только при наличии импульса генератора и готовности этапа, т.е. на время отсутствия импульса блока 11 генератора блок I счетчика этапов оказывается защищенным от воздействия помехи.

На временной диаграмме (фиг.7) обозначены: t - момент прихода сигнала готовности этапа; t — момент снятия сигнала готовности (по стробирующему импульсу с 6JIDEB 11); (в

t ) — длительность стробирующего импульса; (-t ) — время задержки в блоке 12, Последовательность появления сигналов этапов на выходе блока 2 дешифратора показаиа на временной диаграмме (фиг.8), где обозначены: Вых. бл.l — стробирующие сигналы на выходе блока 11 генератора; Вых.бл.10— сигнал готовности (n-1)-ro этапа на входе элемента И 44 (фиг,4);"

Вых.бл.2 — сигнала и-го этапа на выходе блока 2 дешифратора; Вых.бл.10— сигнал готовности и-го этапа на входе элемента И 44 (фиг,4); Вых.бл.2— сигнал (6+1)-ro этапа на выходе блока 2 дешифратора; (t>-С, ) и (t< -t>)длительность выполнения операций и-го и (n+1)-ro этапов; (t "t„) и (t+-t4) — длительность сигналов готовности (п-1)-го и и-го этапов.

Таким образом, повышение надежности в устройстве достигается тем, что второй вход блока 1 счетчика этапов соединен с выходом блока 11 генератора, что препятствует срабатыванию блока 1 счетчика этапов от сигналов помехи во время отсутствия импульса генератора.

Расширение функциональных возможностей устройства достигается тем, что второй выход блока таймера 9 соединен с третьим входом блока 5 логики, а выход блока 10 запрета через блок 12 задержки — с вторым входом блока таймера, на третий вход которого, а также на второй вход блока 1 счетчика этапов подключен выход блока 11 генератора, что позволяет применять устройство для программного управления для реализации алгоритмов, в которых есть временные этапы.

7 14

Фо рмула изо6 ре тения

Ус тройс тво для программно го управления, содержащее блок счетчика эта— пов, первым входом соединенный с выходом блока запрета, а выходом — с блоком дешифратора, выход которого соединен с первым входом блока логики, блоком формирователя команд управления и первым входом блока контроля и индикации, выходы блока формирователя команд управления соединены с соответствующими входами блока ис-т полнительных механизмов, выходы которого соединены с соответствующими входами блока датчиков поло....ения, выходы которого соединены с соответствующими входами блока гальванических развязок и связи с оператором, выход которого соединен с вторым входом блока логики и вторым входом блока

56933 контроля и индикации, третий вход блока контроля и индикации соединен

„с первым выходом блока таймера, пер5 вый вход блока таймера соединен с пе ррым выходом блока контроля и индикации„ второй выход которого соединен с первым входом блока запрета, второй вход которого соединен с выходом блока ло-*

10 гики, о тличающее ся тем, что, с целью повышения надежности устройства и расширения его функциональных возможностей, в него введены блок генератора и блок задержки, 15 вход которого соединен с выходом бло" ка запрета, а выход — с вторым входом блока таймера, блок генератора соединен с вторым входом счетчика этапов, четвертым входом блока контроля и

20 индикации и с третьим входом блока таймера, второй выход которого соединен с третьим входом блока логики.

1456933

1456933

1456933 йщ. 91 Ь/х &Ю

Рыкdil

Составитель М. Любисткова

Редактор О. Юрковецкая Техред А.Кравчук Корректор О. Кравцова

Заказ 7552/46 Тираж 788 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д; 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4