Программатор для постоянных запоминающих устройств

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для программирования ПЗУ с совмещенной шиной Адрес/данные. Программатор содержит адаптер 1, регистры адреса 2 и данных 4, блок 3 управления , программируемый источник 5 питания, блок 6 памяти временных диаграмм, блок 7 ключей. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИН (51)4 G 11 С 17/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР.(21) 4192477/24-24 (22) 09.01,87 (46) 07..02.89. Бюл, Ф 5 (72) Н,Н.Алферьев, С,В,Радиевский, А.Г,Щербаков, O,А,Васильева, В.Д,Кочкин и В,А,Шунин (53) 681. 327.6(088. 8) (56) Авторское свидетельство СССР

Р 1134964, кл. G 11 С 7/00, 1982.

Лукьянов Д,А, Схемотехнйка универсальных программаторов ПЗУ, — Микропроцессорные средства и системы, 1985, Н 3, с,84-88, рис,1, „„SU„„1456994 А1 (54) ПРОГРАММАТОР ДЛЯ ПОСТОЯННЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ (57) Изобретение относится к вычислительной технике и может быть использовано для программирования ПЗУ с совмещенной шиной "Адрес/данные", Про гр амматор содержит адаптер 1, регистры адреса 2 и данных 4, блок Э управления, программируемый источник

5 питания, блок 6 памяти временных диаграмм, блок 7 ключей. 2 ил, 1456994

Изобретение относится к вычисли.тельной технике и может быть использовано для записи информации в программируемые постоянные запоминающие устройства (ПЗУ), Цель изобретения — расширение функциональных возможностей устройства эа счет оперативного изменения программирования для новых типов ЭВМ, 10

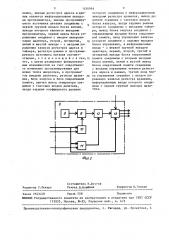

На фиг,1 приведена структурная схема программатора; на фиг,2 "-структурная схема блока памяти временных диагр амм, Программатор ПЗУ содержит адаптер 15

1, регистр 2 адреса, блок 3 управления, регистр 4 данных, програмируемый источник 5 питания, блок 6 памяти временных диаграмм, блок 7 ключей, Блок 6 памяти временных диаграмм со- 20 держит генератор 8, делитель 9 с прогр аммируемым коэффициентом деления, регистр 10 хранения с переменным коэффициентом деления, программируема таймер 11 блок 12 запуска, блок 13 оперативной памяти, Программатор работает следующим образам, Из микроЭВМ через адаптер 1 в: блок 6 памяти записывается программа программирования конкретной микросхемы, установленной по средством разъема на плате 8, В блок 5 программируемого источника питания по сигналу от блока 3 управления записыва- 35 ется код, устанавливающий необходимые напряжения программирования. В регистр 2 адреса записывается адрес программируемой ячейки. В регистр 4 данных записываются данные, подлежа- 40 щие программированию в ПЗУ, Обмен информацией между микроЭВМ и блоками программатора прои=-водится при помощи блока 3 управления, После занесения в программатор всей предваритель-45 ной информации из микроЭВМ блоком 3 у пр авл ения выдает ся ко манд а з апу ск а программы, записанной в блоке б памят ти, В соответствии с временной диаг" раммой программирования на микросхему ПЗУ подается адрес ячейки из регистра 2 адреса, программируемые данные из регистра 4 данных и высоковольтные импульсы программирования из программируемого источника 5 питания через ключи блока 7. При этом перед программированием конкретной микросхема ПЗУ из обслуживающей прог-! раммы заносится в регистр 10 блока

6 необходимый коэффициент делителя исходной частоты генератора 8. Это нужно для различной дискретизации частоты при формировании временных диаграмм в диапазоне 0,1 — 10 мкс (для прораммирования различных типов микросхем ПЗУ), В блок 6 записывается про гр амма временной ди агр азы, В програмируемый таймер 11 заносится код необходимых временных задержек в соответствии с частотой дискретизации. После этого происходит запуск таймера 11 по сигналу от микроЭВМ, который включает блок 12, Информация с выхода блока 13 управляет силовыми ключами блока 7 и выдачей информации с регистров 2 и 4.

Длительность интервалов временной диаграммы формируется с помощью программируемого таймера 11, который на заданное время блокирует прохождение тактовой частоты для считывания оперативной памяти, Блок 12 запуска со" держит триггер признака программиро-. вания, который устанавливается при запуске блока оперативной памяти и переключается обратно по окончании цикла программирования по сигналу с т аймер а 11.

По окончании цикла программирования управление снова передается микроЭВМ, Следующий цикл программирования начинается после записи новых значений в регистры 2 и 4 адреса и данных, Информация с выхода этих регистров передается на программируемую микросхему только по сигналам с выхода блока 6. памяти, т,е, по программе, Это дает возможность программировать микросхему ПЗУ с совмещенной шиной

"Адре с/д анны е", Формул а изобретения

Программатор для постоянных запоминающих устройств, содержащий адаптер, регистры адреса и данных, блок ключей, программируемый источник питания, блок управления, блок памяти временных диаграмм, состоящий иэ генератора и таймера, первая и вторая группа входов адаптера являют. ся входами программатора, первая группа выходов адаптера соединена с информационными входами регистров адреса и данных, и программируемого источника питания и таймера, вторая группа выходов адаптера соединена с входами задания режима блока управ1456994

Составитель Н,Лустов

Техред Л. Олийнык

Корректор Н, Гунько

Редактор С.Пекарь

- Заказ 7553/49 Тираж 558 Под пис ное

BHHHHH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 ления, выходы регистров адреса и данных являются информационными выходами программатора, выходы программируемого источника питания соединены с первой группой входов блока ключей, выходы которого являются выходами программатора, первый выход блока уп, равления соединен с входом синхронизации адаптера, второй, четвертый, пятый и шестой выходы - с входами управления записью регистров адреса и таймера, регистра данных и программируемого источника питания соответственно, отличающийся тем,15 что, с целью расширения функциональных возможностей за счет оперативного изменения программирования для новых типов микросхем, в программатор введены делитель, регистр хране- рд ния, блок запуска и блок оперативной памяти, причем выход генератора соединен с тактовым входом делителя, входы задания коэффициента деления которо го соединены с информационными выходами регистра хранения, выход, делителя соединен с тактовым входом блока запуска, входы задания режима которого соединены с выходами таймера, выход блокà sапуска соединен с управляющими входами блока оперативной памяти, вход управления записью которого соединен с седьмым выходом блока управления, а информационные входы — с первой группой выходов адаптера, первый, второй, третий и четвертый выходы блока оперативной памяти соединены с вторыми входами блока ключей, пятый и шестой выход .блока оперативной памяти соединены с входами управления чтением регист-. ров адреса и данных, третий вход блока управления соединен с входом управления записью регистра хранения, информационные входы которого соединены с первой группой выходов адап-. тера,