Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может использоваться в системах контроля памяти. Целью изобретения является увеличение быстродействия и достоверности контроля, а также расширение функциональных возможностей устройства за счет контроля блоков памяти с двунаправленными вxoдa м-выходами. Устройство содержит блок генерации тестов, генератор тактовых импульсов, триггер пуска, триггер сбоя, регистры начального и конечного адреса, счетчик адреса, первый и второй блоки сравнения, блок ввода информации, элементы И. Цель изобретения достигается введением программируемого блока генерации тестов, регистра начального адреса, позволяющего в совокупности с регистром конечного адреса задавать любую зону адресов для контроля, а также введе-: нием коммутатора, осуществляющего сопряжение устройства с двунаправленными входами-вь1ходами ко11тролируемого блока памяти. При обнаружении ошибки устройство зацикливается на выполнении операции по адресу с ошибкой , 1 з.п. ф-лы, 2 ил,. а (/

СС(ОЭ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (и) (59 4 0 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

- ПО ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4088996/24-24 (22) 14,07,86 (46) 07.02,89, Бюл, Ф 5 (72) Ю,А.Агарок, Г,Д,Голубев, В,А,Стенькин и Л.В,Чулкина (53) 681.327, 6(088,8) (56 ) Автор ское свидетельство СССР

В 610!80, кл, G 11 С 29/00, 1976.

Авторское свидетельство СССР

9 842978, кл, G 11 С 29/00, 1979,. ! (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ

ПАМЯТИ (57) Изобретение относится к области вычислительной техники и может использоваться в системах контроля памяти, Целью изобретения является увеличение быстродействия и достоверности контроля, а также расширение функциональных возможностей устройства за счет контроля блоков паИзобретение относится к вычислительной технике и может использоваться в системах контроля памяти.

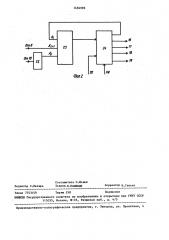

Целью изобретения является увеличение быстродействия и достоверности контроля, а также расширение функциональных возможностей устройства за счет контроля блоков памяти с дву..направленными входами-выходаьи, На фиг, 1 представлена схема устройства для контроля блоков памяти; на фиг.2 — схема .блока генерации тестов.

Устройство (фиг. 1) содержит генератор 1 тактовых импульсов, первый 2 и второй 3 элементы И, счетчик 4 адмяти с двунаправленными входами-выходами, Устройство содержит блок ге" нерации тестов, генератор тактовых импульсов, триггер пуска, триггер сбоя, регистры начального и конечного адреса, счетчик адреса, первый и. второй блоки ср авнения, бло к ввода информации, элементы И, Цель изобретения достигается введением программируемого блока генерации тестов, регистра начапьного адреса, позволяющего в совокупности с регистром конечного адреса задавать любую зону адресов для контроля, а также введением коммутатора, осуществляющего сопряжение устройства с двунаправленными входами-выходами контролируемого блока памяти, При обнаружении ошибки устройство зацикливается на выполнении операции по адресу с ошибкой, 1 з,п, ф-лы, 2 ил, 2 реса, первый 5 и второй 6 блоки сравнения, триггер 7 цикла, триггер 8 сбоя, третий элемент И 9, блок 10 ввода информации, регистр 11 конечного адреса, регистр 12 начального адреса, коммутатор 13, блок 14 гене рации тестов, На фиг,! также показаны проверяемый блок 15 памяти, управляющие выходы блока генерации тестов: 16 — признака счета, 1?— признака конца теста, 18 — режима, !

9 — эталонного слова, а также синхровход 20 блока генерации тестов и вход 21 "Ответ памяти" устройства.

Блок генерации тестов (фиг,2) содержит регистр 22 теста, узел 23 хра6996

25

30 ку

40 с

55 з 145 нения программы (оперативное или постоянное ЗУ), регистр 24 программ.

Устройство работает следукицим образом, С блока 10 ввода информации задаются пределы зоны адресов контролируемого блока памяти, т,е, записыва ется в регистр 1 код конечного адреса в регистр 12 код начального адре са, а в блок 14 генер ации те сто в записывается код выбранного теста, который заносится в регистр 22 теста и является А„частью всего адреса узла

23 хранения теста, Далее по команде

"Начальная установка" устанавливаются в нулевое положение триггер 7 и регистр 24 программ блока 14, а триггер 8 - в единичное состояние, и содержимое регистра 12 переписывается в счетчик 4 адреса, а по команде

"Пуск"триггер 7 цикла устанавливается в единичное состояние и разрешает .через элемент И 2 прохождение сигнала с генератора 1 тактовых импульсов, причем выхбд 20 элемента И 3 является основным управляющим сигналом устройства, который воздействует на регистр 24 блока 14, переписывая содержимое узла 23 по нулевому А„адресу в регистр 24, На выходе регистра 24 появляются управляющие сигналы 16, 17, 19 и А часть нового адреса узла

23.

Управляющий сигнал 16 с регистра

24 подается на четвертый вход счетчика 4 адреса и разрешает наращивание адреса счетчика 4 на единицу. Выzop 17 регистра 24 осуществляет сброс, т,е, установку в нулевое положение триггера 7 цикла, Этот сигнал вырабатывается в узле 23 в конце теста, когда весь алгоритм теста выполнен и пришел сигнал со схемы 6 сравнения, который ук азыв ае т на то, что счетчик 4 адреса находится в том же состоянии, что и регистр 11 конечного адреса, Выход регистра 24 блока 14 генерации теста вырабатывает сигнал режи" ма работы блока памяти: запись в него информации или считывание из блока памяти хранимой информации с последующим ее сравнением в блоке 5 срав-. нения с эталонной информацией, Кроме того, этот сигнап дает разрешение на прохождение сигнала выхода с блока 5 сравнения на информационный вход триггера 8, управление которым осуществляется сигналом 21 с блока 15 памяти, В случае несовпадения выходной информации с блока памяти и эталонной информации три ггер 8 у ст ан ав- ливается в нулевое положение и запрещает дальнейшее управление счетчиком 4 адреса. Выход 19 представляет собой сигнал эталонного тестового слова, который в режиме записи через. коммутатор 3 передается в блок

15 памяти, а при считывании поступает в блок 5 сравнения. Управление коммутатором 13, т. е. переключение его в положение "Прием" или "Передача" осуществляется сигналом с выхода

18.

Техническим преимуществом устройства является то, что в случае возникновения сбоя триггер 8 не запрещает поступление тактового сигнала на контролируемый блок памяти, а только останавливают работу счетчика

4 адреса.и запись в регистр 24 программ воздействием на элемент И 3, Это позволяет при постоянном адресе и тесте тщательно проследить неисправную цепь блока памяти в активном режиме и обнаружить неисправную ячейФо р мул а и з о б р е т е ни я

1, Устройство для контроля блоков памяти, содержащее генератор тактовых импульсов, выход которого подключен к первому входу первого элемента И, второй вход которого соединен с выходом триггера цикла, а вы-ход является выходом выборки устройства, второй элемент И, первый вход которого подключен к выходу триггера сбоя, первый вход которого соединен с выходом третьего элемента И, первый вход которого подключен к выходу первого блока сравнения, блок ввода информации, выходы кода адреса которо ro соединены с входами регистра конечного адреса, выходы которо го подключены к входам первой группы второго блока сравнения, входы втор ой группы ко тороî ro соединены с выходами сче тчика адреса, являющимися адресными выходами устройства, о т л и ч а ющ е е с я тем, что, с целью увеличения быстродействия и достоверности контроля, а также расширения функ циональных возможностей устройства

5 1456 за счет контроля блоков памяти с дву.— направленными входами-выходами, в устройство введены блок генерации тестов, регистр начального адреса и

5 коммутатор, причем синхровход счетчика адреса соединен с выходом второго элемента И и с синхровходом блока генерации тестов, вход признака конца адреса которого подключен к выходу 10 второго блока сравнения и к входу установки начального адреса счетчика адреса, информационные входы которого соединены с выходами регистра начального адреса, входы которого под- 15 ключены к выходам кода адреса блока ввода информации, выходы кода теста, которого соединены с одноименными . входами бока генерации тестов, выходы признаков счета и конца теста кото- 20 рого подключены соответственно к управляющему входу счетчика адреса и к первому входу триггера цикла, второй вход которого соединен с выходом пуска блока ввода информации, выход начальной установки которого подключен к одноименным входам триггеров цикла и сбоя, счетчика адреса и блока ге" нерации тестов, выход режима которого соединен с вторым входом третьего 30 элемента И, управляющим входом коммутатора и является выходом записи-считывания устройства, выход эталонного

996 слова блока генерации тестов подключен к первому входу первого блока сравнения и к информационному входу коммутатора, выход которого соединен с вторым входом первого блока срав-. нения > а Информационные входы-выходы являются одноименными входами-выходами устройства, выход первого зле мента И подключен к второму входу второго элемента И, второй вход триггера сбоя является входом ответа памя ти у строй ст в а, 2. Устройство по п, 1, о т л ич а ю щ е е с я тем, что блок генерации тестов содержит узел хранения

Ф про грамм, одни адресные входы, которого соединены с выходами кода следу юще го адр е с а р е ги стр а про гр амм, другой адресный вход является входом признака-конца адреса, третьи адресные входы узла хранения программы подключены к выводам регистра теста, I входы которого являются входами кода теста, выходы узла хранения программ подключены к информационным входам регистра программ, синхровход и ! вход начальной установки, а также выходы признака счета, признака конца теста, режима и эталонного слова которого являются одноименными входами и выходами блока.!

456996

Составитель О.Исаев

Те хред. JI. Олиущык

Редактор С,Пекарь

КоРРектоР Н, Гунько

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Заказ 7553/49 Тирах 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5