Устройство для контроля цифровых блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков ;средств цифровой вычислительной техники . Цель изобретения - повышение достоверности контроля цифровых блоков и быстродействия устройства. Указанная цель достигается путем ввеле ния в устройство D-триггера 10, счетчика 11 и образования новых линий связи. Кроме того, устройство содержит задатчик 1 тестов, мультиплексор 3, генератор 4 пачки импульсов , элемент И 5, счетчик 6, сигнатурный анализатор 7, блок 8 управления , блок 9 памяти сигнатур, блок 12 сравнения, триггер 13 правильности сигнатур и индикатор 14. Устройство обеспечивает однозначность сравнения снятой сигнатуры с данного вьшода с эталонной сигнатурой этого же вывода. При этом обеспечивается необходимость ручного подключения выводов контролируемого цифрового блока 2 к сигнатурному анализатору 7 при помощи кнопки блока 8 управления. 1 э.п. ф-лы, 3 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) А1 (594 С О1 Р 31 2

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ пО изоБРетениям и oTHpblTHflM

ПРИ ГННТ СССР

: (21) 4268302/24-21

l(22) 26.06.87 (46) 15.02.89. Бюл. 11 6, 71) Научно-исследовательский и конструкторско-технологический институт средств контроля электронной аппаратуры и .изделий электронной техники

"Контрольприбор" (72) Л.Л. Лебедь и М.И. Особов (53) 621. 317.799(088.8) (56) Авторское свидетельство СССР

11- 830391, кл. G 05 F 11/26, 1981.

Авторское свидетельство СССР

9 1148009, кл. G 01 R 31/28, )981, (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ

БЛОКОВ (57) Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков средств цифровой вычислительной техники. Цель изобретения — повышение до с то ве рно сти контроля цифро вык бло- ков и быстродействия устройства. Указанная цель достигается путем введе ния в устройство Э-триггера 10, счетчика 11 и образования новых линий связи. Кроме того, устройство содержит эадатчик 1 тестов, мультиплексор 3, генератор 4 пачки импульсов, элемент И 5, счетчик 6, сигнатурный анализатор 7, блок 8 управления, блок 9 памяти сигнатур, блок 12 сравнения, триггер 13 правильности сигнатур и индикатор 14. Устройство обеспечивае т одно значнос ть сравнения снятой сигнатуры с данного вывода с эталонной сигнатурой этого же вывода. g

При этом обеспечивается необходимость ручного подключения выводов контролируемого цифрового блока 2 к сигнатурному анализатору 7 при помощи кнопки С блока 8 управления. э.п. ф-лы, 3 ил.

1458841

Изобретение относится к вычислительной технике и может быть использовано для контроля логических блоков средств вычислительной техники, диск- 5 ретной автоматики.

Цель изобретения — повышение дост оверности контроля и быстродействия устройства за счет однозначности сравнения снятой сигнатуры с данного 10 вывода с эталонной сигнатурой этого же вывода, и исключение необходимости ручного подключения выходов контролируемого блока к сигнатурному анализатору при помощи кнопки блока уп- 15 равления.

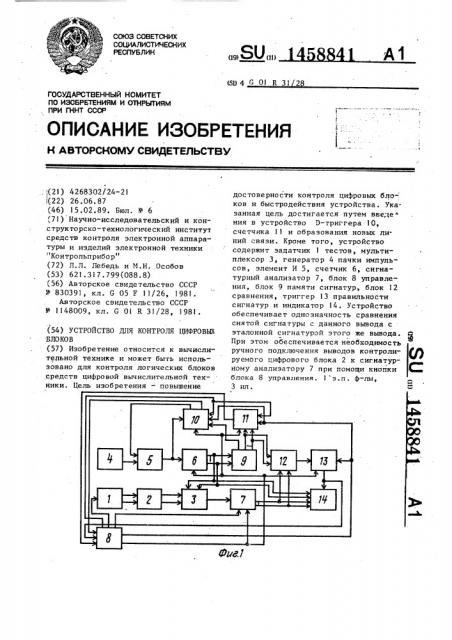

На фиг. -1 приведена блок-.схема устройства;.на фиг, 2 — функциональная схема блока управления; на фиг.3 — формат информации, хранящий- 20 ся в блоке памяти сигнатур.

Устройство содержит задатчик 1 тестов, контролируемый цифровой блок

2, мультиплексор 3, генератор 4 пачки импульсов, первый элемент 5 И, первый счетчик 6, сигнатурный анализатор 7, блок 8 управления, блок 9 памяти сигнатур, D-триггер 1О, второй счетчик 11, блок 12 сравнения, триггер 13 правильности сигнатур и 30 индикатор 14, информационные входы мультиплексора 3 соединены с клеммами для подключения выходов контролируемого цифрового блока 2, а выход — с информационным входом сигнатурного анализатора 7. Выходы задатчика 1 тестов связаны с клеммами для подключения входов контролируемого цифрового блока 2, а вход — с первым выходом блока 8 управления. Выход 40 генератора 4 пачки импульсов подключен через первый элемент И 5, к счетному входу. первого счетчика 6 и Свходу D-триггера 10. Информационные выходы первого счетчика 6 соединены 45 с адресными йходами блока 9 памяти сигнатур, управляющими входами мультиплексора 3 и третьими входами индика— тора 14. Группа информационных выходов блока 9 памяти сигнатур связана с первыми входами блока 12 сравнения и информационными вхо-. дами второго счетчика. 11. Выход блока 12 сравнения соединен с информационным входом триггера 13 правильности сигнатур, выход которого подключен к первому входу индикатора 14 и второму входу блока 8 управления.

Вторые входы индикатора 14 соединены с вьг-.одом сигнатурного анализатора 7. и вторыми входами блока 12 сравнения.

Второй выход блока 8 управления подсоединен к ус тано вочным входам си гнатурного анализатора 7, первого счетчика 6, триггера 13 правильности сигнатур, R-входу D-триггера 10 и

R-входу второго счетчика 11. Синхровход сигнатурного анализатора 7 соединен с третьим выходом блока 8 управления. Второй выход блока 9 памяти сигнатур связан с D-входом;3".-риггера 10, первый S-вход которого соединен с вычитающим входом второго счетчика 11, синхровходом триггера

13 правильности сигнатур и четьерTblM выходом блока 8 управления. Счетный вход второго счетчика 11 подключен к второму S-входу D-триггера 10 и пятому выходу блока S управления.

Второй вход первого элемента И 5 соединен с прямым выходом первого

D-тригегра IO, инверсный выход которого связан с первым входом блока 8 управления, третий вход которого соединен с выходом переноса второго счетчика 11.

Блок 8 управления содержит кноп-. ку 15 пуска, элемент ИЛИ 16, D-триггер 17, элемент И 18, генератор 19

J импульсов, счетный триггер 20, третий счетчик 21, кнопку 22 исходной установки и резистор 23, 1

Кнопка исходной установки 22 соединена первым выводом с общей IIIHHoH устройства, вторым выводом — с вторым выходом блока, установочными вхо дами счетного триггера 20, счетчика

21 и первым входом элемента ИЛИ 16, второй вход которого связан с четвертым выходом блока и выходом счетчика 21, счетный вход которого соединен с третьим выходом блока и первым выходом счетного триггера 20, второй выход которого подключен к первому выходу блока, а счетный вход. K выходу элемента ИЛИ 16, первый вход которого соединен с выходом генератора 19 импульсов, а второй — с выходом Dтриггера 17, D-вход которого соединен через резистор 23 с шиной питания, С-вход — с первым входом блока, а R-вход — с выходом элемента ИЛИ

16, третий вход которого соединен с третьим входом блока, а четвертый вход — с вторым входом блока, пятый выход которого подключен к первому з 14588 выходу кнопки пуска 15, второй вывод которой соединен с общей шиной устройства.

Блок 9 памяти сигнатур представ-.

5 ляе т собой пос тоянное запоминающее устройство (ПЗУ) с организацией и х,k+1) бит, где n — максимальный номер выхода контролируемого цифрового-блока; k — разрядность сигнату- 10

P61 °

По нулевому адресу в П3у записывае тся- количе ство выходов контролируемого цифрового блока 2 в двоичном коде. В адресном поле (с 1 по n) 15 в информационном слове (c 1 по k) записывается эталонная сигнатура каждого выхода контролируемого цифрового блока 2 в ячейку, адрес которой соответствует порядковому номеру выхо- 20 да, при этом в информационном слове (разряд k+! ) записывается "0", если этот вьпсод подлежит контролю по данной сигнатуре,или "1", если данный вывод в контролируемом цифровом бло- 25 ке 2 отсутствует или он является входом.

Устройство работает следующим образом.

Блок 8 управления выдает сигнал 30 начальной установки, который устанавливает сигнатурный анализатор 7, первый счетчик 6, второй счетчик 11 первый D-триггер .10 и триггер 13 правильности сигнатур в исходное нулевое состояние. По сигналу "Пуск" из блока 8 управления во второй счетчик 11 записывается по информационным входам из блока 9 памяти сигнатур количество выходов в контролируе- 40 мом цифровом блоке 2 в двоичном коде.

По этому же сигналу первый D-триггер 10 устанавливается в единичное состояние и своим прямым выходом открывает первый элемент И 5, По первому сигналу с генератора 4 пачки импульсов через элемент И 5 первый счетчик 6 устанавливается в единичное состояние, из блока 9 памяти сигнатур выбирается содержимое первого адреса. 50

Если первый выход в контролируемом цифровом блоке является выходным> то в разряде (k+1) блока 9 памяти сигнатур записан Й . По заднему фронту сигнала с первого элемента

И 5 первый Э-триггер !О устанавливается в нулевое состояние, своим прямым выходом закрывает первый элемент

И 5. Ча первом счетчике 6 фиксирует41

4 ся единичное состояние. К информационному входу сигнатурного анализатора 7 через мультиплексор. 3 подключаются первый выход контролируемого цифрового блока 2. Эталонная сигнатура, соответствующая первому выходу, записана по первому адресу в блоке 9 памяти сигнатур. Эталонная сигнатура поступает с информационных выходов блока 9 памяти сигнатур на первые входы блока 12 сравнения. По положительному перепаду с инверсного выхода первого D-триггера блок 8 управления выдает сигнал по первому выходу, по которому осуществляется вывод с задатчика 1 тестов первого теста на входы контролируемого блока 2. С первого выхода блока 2 информация через мультиплексор 3 поступает на сигнатурный анализатор 7, представляющий собой сдвигающий регистр, охваченный обратными связями через схему сложения по модулю два.

По первому сигналу сдвига с блока 8 управления эта информация записывается в первый разряд анализатора 7.

По второму сигналу с блока 8 управ" ления задатчик 1 тестов выдает второй тест на блок 2, а с первого выхода блока 2 через мультиплексор 3 второй бит информации поступает на вход анализатора 7 и по второму сигналу сдвига с блока 8 управления записывается в анализатор 7 и т.д. до тех пор, пока вся тестовая программа не будет выведена из задатчика 1 тестов и вся последовательность кодов с первого выхода контролируемого блока 2 не окажется свернутой в сигнатурном анализаторе 7.

Свертка этой информации поступает в параллельном коде на вторые входы индикатора. После этого блок 8 управ-" ления выдает сигнал с четвертого вы-. хода, который фиксирует на триггере

13 правильности сигнатур результат сравнения информации, полученной на сигнатурном анализаторе 7 с первого выхода блок 2 и выведенной из первого адреса блока 9 памяти сигнатур.

В результате если снятая сигнатура с первого вывода блока 2 отлична от эталонной сигнатуры, записанной по первому адресу в блоке 9 памяти сигнатур, то считается, что данный вывод блока неисправен. Сигнал с выхода триггера 13 правильности сигнатур, означающий несравнение снятой

50

5 14588 и эталонной сигнатуры, поступает на второй вход блока 8 управления, по которому останавливается процесс контроля . На индикаторе 14 высвечива5 ется номер вывода, по которому произошло несравнение, признак несравнения и снятая с вывода сигнатура.

В случае сравнения снятой и эталонной сигнатуры, т.е. триггер 13 пра- I0 вильности сигнатур находится в нулевом состоянии, по заднему фронту сигнала с четвертого выхода блока 8 управления содержимое второго счетчика 11 уменьшается на единицу, а 15 первый Э-триггер 1 0 устанавливается в единичное состояние и своим прямым выходом открывает первый элемент И 5..

Сигналы сгенератора 4 пачки жипульсов через открытый элемент И 5 поступают 20 на счетный вход первого счетчика 6.

Из блока 9 памяти сигнатур выбирается содержимое второго адреса и к сигнатурному анализатору 7 через мультиплексор 3 подключается второй выход блока 2.

Если с второго выхода блока 9 памяти сигнатур считан ноль, означающий, что второй выход контролируемого блока 2 подлежит контролю, первый 30

D-тригrер 10 устанавливается в нулевое состояние.. Происходит снятие и сравнение сигнатуры с второго вывода также, как и для первого, Если с второго выхода блока 9 памяти сигнатур считана единица, означающая, что данс ный вывод контролируемого цифрового блока 2 не подлежит контролю, первый

D-.òðèããåð 10 остается в единичном состоянии, первый счетчик 6 изменяет д0 состояние на единицу, из блока 9 памяти сигнатур выбирается информация со следующего адреса и т.д,, пока с второго выхода блока 9 памяти сигна- тур не считается ноль, означающий, что данный выход контролируемого циф- рового блока 2 подлежит контролю по эталонной сигнатуре, записанной в этом адресе.

41 управления прекращается процесс контроля.

Блок 8 управления работает следующим образом.

При нажатии кнопки 22 счетный триггер 20, третий счетчик 21 и второй D-триггер 17 через элемент ИЛИ

16 устанавливаются в исходное состояние и на анализатор 7, первый счетчик 6, второй счетчик 1 I, первый

Р-триггер 10 и триггер 13 выдается сигнал начальной установки. При нажатии кнопки 15 на первый П-триггер 10 и второй счетчик I I выдается сигнал пуска. При поступлении положительного перепада на первый вход блока с инверсного выхода, первого D-триггера 10 второй D-триггер 17 устанавливается в единичное состояние . Прямым выходом второй D-триггер 17 открывает элемент И 18 и импульсы с гене-. ратора 19 поступают на счетный вход триггера 20. С выхода счетного триггера 20 снимаются две последовательности импульсов, сдвинутые друг относительно друга на половину такта.

Одна из последовательностей используется для задания тестов из задатчика 1, другая — для сдвига информации в анализаторе 7. Третий счетчик

21 подсчитывает количество тактов в тестовой последовательности и по окончании счета выдает сигнал на четвертый выход блока 8 управления и через элемент ИЛИ 16 сбрасывает в

"0" второй D-триггер 17, который блокирует второй элемент И 18 и прерывает поступление импульсов задания тестов и сдвига на задатчик 1 и анализатор 7. Сигналы с второго и третьего входов блока 8 управления поступают на схему ИЛИ 16, устанавливая в нулевое состояние второй

D-триггер 17, если снятая с выхода контролируемого цифрового блока сигнатура не соответствует эталонной или если процесс контроля цифрового блока окончен, т.е. второй счетчик

11 обнуляется.

После каждого снятия сигнатуры с выходов контролируемого цифрового блока 2 и ее сравнения с эталонной содержимое второго счетчика 11 уменьшается на единицу. После того, как все выходы контролируемого блока 2 проверены, содержимое второго счетчика 1) равно нулю и по сигналу переноса с второго счетчика 11 блок 8

Формула изобретения

1. Устройство для контроля цифровых блоков, содержащее задатчик тестов, мультиплексор, сигнатурный анализатор, генератор пачки импульсов, первый. элемент И, первый счетчик, блок памяти сигнатур, блок сравнения, 58841 8

40

7 1÷ триггер правильности сигнатур, индикатор, блок управления, причем информационные входы мультиплексора соединены с клеммами для подключения выходов контролируемого цифрового блока, а выход — с информационным входом сигнатурного анализатора, выход эадатчика тестов соединен с клеммами для подключения входов контролируемого цифрового блока, а вход †.с первым выходом блока управления, выход генератора пачки импульсов соединен через первый элемент И со счетным входом первого счетчика, информационные выходы которого соединены с адресными входами блока памяти сигнатур, соединенного группой информа ционных выходов с первыми входами блока сравнения, выход которого сое- . динен с информационным входом триггера правильности сигнатур, выход которого соединен с первым входом индикатора, соединенного вторыми входами с выходами сигнатурного анализатора . и вторыми входами блока сравнения, второй выход блока управления сое" динен с установочными входами сигнатурного анализатора первого счетчика и триггера правильности сигнатур, синхровход сигнатурного анализатора соединен с третьим выходом блока управления, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля и быстродействия устройства в него ввецены D-триггер и второй счетчик, причем информационные входы второго счетчика соединены с группой информационных выходов блока памяти сигнатур, вторым выходом соединенного с D-входом D-триггера, первый S-вход которого соединен с вычитающим входом второго счетчика, синхровходом триггера правильности сигнатур и четвертым выходом блока . управления, счетный вход второго счетчика соединен с вторым S-входом

D-триггера и пятым выходом блока уп °

30 равления, С-вход D-триггера соединен с выходом первого элемента И, вторым входом соединенного с прямым выходом

D-триггера, инверсный выход которого соединен с первым входом блока управления, соединенного вторым входом с выходом триггера правильности сигнатур, третьи входы индикатора соединены с информационными выходами первого счетчика и с управляющими входами мультиплексора, третий вход блока управления соединен с выходом переноса второго счетчика, R-вход

D-триггера соединен с R-входом второго счетчика и установочным входом первого счетчика, 2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок управления содержит кнопку пуска, D-триггер, элемент И, счетный триггер, счетчик, элемент ИЛИ, генератор импульсов; резистор, кнопку исходной установки, соединенную первым выводом с общей шиной устройства, вторым выводом — с вторым выходом блока, установочными входами счетного триггера, счетчика и первым входом элемента ИЛИ

ИЛИ, второй вход которого соединен с четвертым выходом блока и выходом счетчика, счетный вход которого соединен с третьим выходом блока и пер" вым выходом счетного триггера, второй выход которого соединен с первым выходом блока, а счетный вход — с выходом элемента И, первый вход которого соединен с выходом генератора импульсов, а .второй — с выходом D-триггера, D-вход которого соединен через резистор с шиной питания, С-вход— с первым входом блока, а R-вход соединен с выходом элемента ИЛИ, третий вход которог соединен с третьим входом блока, а четвертый вход - с вторым входом блока, пятый выход которого соединен с первым выводом кнопки пуска, второй вывод которой соединен с общей шиной устройства.

1458841

ЛОМ

У

ЛОМ

ОД13

Составитель Е.,Строкань

Редакто р Л. Пчолинская Техред Л. Сердюкова. Корректор М. Шаропщ

Заказ 368/51 Тираж 71! Подписное

ВНИИПИ ГосУдарственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4