Устройство для ввода данных

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах. Цель ияобретения - -расширение функционалывлх возможностей устройства за счет организации автоматического (без учас тия программиста) выравниваиия двух синхронных,, но сдвинутых во времени потоков данных с целью ввода их в процессор, выполняющий диадические

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

15ц 4 G 06 F 3/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (2)) 4268684/24-24 (22) !3.04.87 (46) !5.02.89. Вюл. Ь - 6 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) А.И.Гречишников, В.Е.Сметанко и В.В.Сигарева (53) 681.325(088.8) (56) Авторское свидетельство СССР

11 1269144, кл. G 06 F 13/00, 1985.

Патент Японии Н - 58-57776, кл. G 06 F 5/06, опублик. 1982.

„„SU„„1458871 А1 (54) УСТРОЙСТВО ДЛЯ ВВОДА ДАННЬК (57) Изобретение относится к вычислительной технике и может быть использовано в многопроцессорю х вычислительных системах. Цель изобретения — расширение функциональных воэможностей устройства sa счет организации автоматического (без участия программиста) выравнивания двух синхронных, но сдвинутых во времени потоков данных с целью ввода их в процессор, выполняющий диадические

1458871 операции. Это достигается тем, что в устройство, .содержащее три мультиплексора 1, 2 и 3, два блока 5 и 6 памяти, первый регистр 7 узел 9 управления и генератор 12 тактовых сигналов, введены узел 10 адресации, триггер 11, второй регистр 8 и четвертый мультиплексор 4. Потоки входных данных принимаются на первую 13 и вторую 14 группы информационных входов мультиплексора 1. Сигналы готовности данных на входах 15 и 16 свидетельствуют о..появлении данных соответственно на группах 13 и 14 инИзобретение относится к области вычислительной техники и может быть использовано в многопроцессорных вычислительных системах, в частности в конвейерных вычислительных системах, для ввода потоков данных в процессоры, выполняющие диадические операции.

Целью изобретения является рас- 10 ширение функциональных возможностей устройства .-за счет организации режима автоматического выравнивания

Двух синхронных, но сдвинутых во времени потоков данных, для ввода их в процессор, выполняющий диадические

on ер ации.

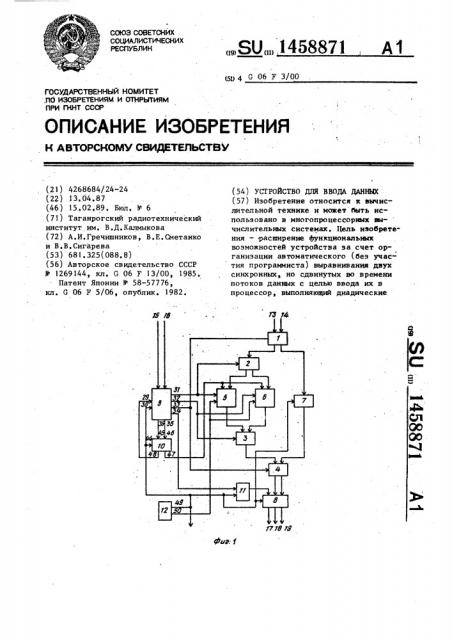

На фиг. 1 представлена структурная блок-схема устройства; на фиг. 2 и

3 — функциональные схемы узлов уп- 2О равления и адресации, на фиг. 4— временные диаграммы работы устройства.

Устройство (фиг. 1 ) содержит третий, первый, второй и четвертый 25 мультиплексоры 1-4, первый и второй блоки 5 памяти и 6, первый и второй регистры 7 и 8, узел 9 управления, узел 10 адресации, триггер 11 и гене= ратор 12 тактовых сигналов. 30

Потоки входных данных принимаются на первую 13 и вторую 14 группу информационных входов мультиплексора 1.

Сигналы готовности данных на входах

15 и 16 свидетельствуют о появлении данных соответственно на информационформационных входов, Выход 17 регистра 8 является управляющим выходом готовности выходных данных устройства. Группы 18 и 19 выходов регистра

8 являются первой и второй группами информационных выходов устройства.

Устройство обеспечивает задержку данных, приходящих на одну группу информационных входов, до момента прихода данных на другую группу входов, после чего начинается одновременная выдача данных на обе группы информа-. ционных выходов устройства. 1 с. и

2 з.п. ф-лы, 7 ил. ных входах 13 и 14. Выход 17 регистра 8 является управляющим выходом готовности устройства, на который выдается сигнал готовности выходных данных устройства. Группы выходов

18 и 19 регистра 8 являются первой и второй группами информационных выходов устройства.

Узел 9 управления содержит (фиг.2) регистр 20, первый 21 и второй 22 элементы ИЛИ, мультиплексор 23, первый — четвертый триггеры 24-27 и элемент ИСКЛ10ЧАЮЩЕЕ ИЛИ 28, входы 29 и 30, выходы 31-36.

Узел 10 адресации содержит (фиг.3) первый 37 и второй 38 регистры, элемент НЕ 39, триггер 40, счетчик 41 адреса, схему 42 сравнения и мультиплексор 43, входы 44-46, группу выходов 47 и выход 48.

На выходах 49 и 50 генератор 12 тактовых сигналов формирует тактовые последовательности (фиг. 1). На фиг. 2 показаны также выходы 51 и 52 мультиплексора 23.

Устройство работает следующим образом.

Узел 9 анализирует наличие сигналов 15, 16 готовности данных на информационных входах 13, 14 и переключает мультиплексор 1 таким образом, что на информационный вход мультиплексора 2 передается поток данных, появившийся первым на информационных входах 13 и 14 устройства. Поток

3 14 данных, который приходит вторым, передается на информационные входы регистра 7 ° Если на входы 13 и 14 данные начинают поступать одновременно, то данные с входов 13 поступают на мультиплексор 2, а данные с входов 14 — на входы регистра 7.

Регистр 7 осуществляет задержку на один такт приходящих на его входы данных. Блоки 5 и 6 памяти осуществляют задержку данных, поступающих на вход мультиплексора 2, на п+1 такт (n — число тактов относительного сдвига между потоками данных, которые приходят на входы 13 и 14).

Величина п определяется узлом 9 по сдвигу между сигналами 15 и 16.

Узел 10 формирует на выходе 47 адреса, поступающие на адресные входы блоков 5 и 6.

Мультиплексор 4, переключаясь, как и мультиплексор l сигналом 33 узла 9 управления, обеспечивает выдачу данных через регистр 8 с входов.

13 всегда на выходы 18, а с входов

14 на выходы 19 устройства. Триггер II предназначен дпя формирования выходного сигнала готов-. ности данных после прихода второго сигнала готовности данных на входь1

15 и 16 устройства.

Генератор 12 тактовых сигналов на выходах 50 и 49 формирует две непрерывные последовательности прямоугольных импульсов со скважностью, равной 2, сдвинутые во времени друг относительно друга на 1/4 периода.

Тактовая последовательность сигналов на выходе 49 служит для синхронизации всех узлов устройства и синхронизации внешних процессоров.

В процессе работы устройства возможны следующие ситуации.

1. Данные на информационных входах 13 появились раньше, чем на входах 14. Соответственно сигнал готэвности данных на входе 14 появился раньше, чем сигнал на входе 16. На фиг.4 приведена диаграмма работы устройства для этого случая при сдвиге между входными потоками данных на один тактовый период (n=l).

Фронт сигнала на выходе элемента

ИЛИ 21 устанавливает триггер 24 в состояние "1" и на выходы 51 и 52 мультиплексора 23 поступают сигналы

15 и 16 соответственно, задержанные на 1/2 тактового периода в регистре

58871

20. "1" на выходе 33 триггера 24 переключает. мультиплексор 1 так, что на информационные входы мультиплексора 2 передаются данные с входов. 13, 5 а на входы регистра 7 - с входов 14.

Положительные перепады сигналов

51 и 52 устанавливают с разницей во времени.на один тактовый период в !

0 состояние "1" триггеры 26 и 27, которые предварительно были установлены в состояние "0" уровнем "0" сигнала на выходе элемента ИЛИ 21. При этом на выходе элемента ИСКЛК)ЧАЮКЕЕ

ИЛИ 28 появляется сигнал, длительность которого равна временному сдвигу между потоками данных на входах

13 и 14 устройства, Фронт этого сигнала записывает исходное состояние

20 А счетчика 41 в регистр 37 и устанавливает в состояние "1" триггер

40, который разрешает счет счетчику

41. На Р-вход триггера 40, не показанный на фиг. 3, постоянно подается

2g сигнал "1". Первый фронт сигнала 49., пржпедший после появления сигнала на входе 15, увеличивает содержимое счетчика 4! на "1". Спадом сигнала на выходе 35 это новое содержимое счет3р чика 41 записывается в регистр 38 и "1" на выходе элемента НЕ 39 разрешает работу схемы 42 сравнения, Так как в этот момент данные на обоих информационных входах схемы 42 срав35 нения равны (A, + 1 ), сигнал на выходе схемы сравнения разрешает запись информации в счетчик 41 из регистра 37.

Поэтому следующим фронтом сигнала на входе 44 счетчик 41 установится

4О в состояние А, затем опять в .А +1 и т.д. до тех пор, пока триггер 40 не установится в состояние "0", т.е. пока присутствуют данные на входах

13 или 14 устройства.

"1" на выходе триггера 40 разрешает передачу на выход 48 мультиплексора:43 сигнала с выхода схемы 42 сравнения. Сигнал с выхода 43 поступает на счетный вход триггера i25 и, 50 так как на выходе элемента ИЛИ присутствует сигнал "I", триггер 25 работает в режиме деления частоты, переключая поочередно блоки 5 и 6 на запись и,чтение. На К-вход триггера

25, не показанный на фиг. 2, постоянно подается сигнал "1".

Таким образом, первые два слова

1 I данных I, и 2, с входов 13 записываются в блок 5 памяти по адресам А и

5 145887

А,+1. Затем третье 3, и четвертое 4 .слово данных записывается в блок 6 памяти по адресам А и А +1 и по этим же адресам из блока 5 считываются слова 1, и 2 . Далее в блок 5 записы вается слово 5,. по адресу А, а из ( блока 6 считывается слово 3 и т.д.

В результате на выходе мультиплексора

3 поток данных, пришедший первым на 10 выходы 13 устройства, оказался задержанным на 2 тактовых периода,т.е. на n+1 А так как регистр 7 обеспечивает задержку данных, поступающих на его входы, на один тактовый период, то на информационных входах регистра 8 потоки данных появляются в одном такте и окончательно выравниваются на выходах регистра 8 без участия программиста. Запись информации 20 в регистр 8 производится спадом сигналов ца выходе 49, что вносит дополнительную задержку информации на 1 /2 тактового периода, °

Сигнал с выхода 52 мультиплексо- 25 ра 23 фронтом сигнала на входе 30 записывается в триггер 11, с выхода которого поступает на отдельный вход регистра 8 для формирования сигнала на выходе 17 готовности выходных 30 данных. Таким образом, сигнал на выходе 17 является задержанным на 1,5 тактового периода сигналом на входе

16, которые начинают поступать вторыми во времени на входы 14.

2. Данные на группах входов 13 и

14 появляются одновременно. Временная диаграмма работы устройства для этого случая приведена на фиг. 5.

Особенности этого режима по сравне- 40 нию с.режимом 1 заключаются в следующем е с

Так как сигналы яа выходах 51 и 52 мультиплексора 23 появляются одновременно, одновременно устанавливаются в 45 состояние "1" триггеры 25 и 26, элемент ИСКЛ1ОЧА1ОЩЕЕ ИЛИ 28 остается. в состоянии "0". Триггер 40 также остается в состоянии "0", Сигнала разрешения счета нет и счетчик 41 остается в состоянии А, Сигнал."0" на выходе триггера 40 подключает на .выход 48 мультиплексора 43 проинвертированный сигнал с выхода 49 генератора тактовых сигналов

12, Триггер 25, управляющий режимом блоков 5 и 6, переключается в результате каждым фронтом сигнала на выходе 49.

1„ 6

Таким образом, вначале по адресу

А в блок 6 записывается слово 1

Затем в блок 6 по адресу А записываI ется слово 2, а из блока 5 считывается слово 1 и т.д. Вследствие этого поток данных с входов 13 задерживается на 1 тактовый период;в блоках

5 и 6„ а поток данных с входов 14 задерживается в регистре 7. На выходах 18 и 19 устройства данные появляются одновременно.

3, Данные на информационных входах 13 появляются позже, чем на вхо = дах 14. Временная диаграмма для этого случая при сдвиге между. входными потоками данных на 4 тактовых периода приведена на фиг. 6.

Особенности этого режима по сравнению с режимом 1 заключаются в том, что триггер 24 фронтом сигнала на выходе элемента ИЛИ 21 устанавливается в "0", Мультиплексор 1 передает на входы мультиплексора 2 данные с входов 14, а на входы регистра 7 данные с входов 13 устройства. В блоIf и ках 5 и 6 данные 1 .. ° 8з задерживаются на 5 тактов и одновременно с ! t данными 1 ° ° 8 лшявляются на Выхо дах соответственно 19 и 18 устройства, .Мультиплексор 23 переключается таким образом, что на выходы 51 и

52 передаются соответственно сигналы с входов 16 и 15 готовности входных данных. Таким образом, сигнал на выходе 17 готовности выходных данных является задержанным на 1,5 тактового периода сигналом на входе. 15 го-товности входных данных 13.

4. Новый поток данных на одной из групп входов устройства появляется, когда на другую группу входов еще продолжает поступать предыдущий поток данных На фиг. 7 приведена временная диаграмма работы устройства

О для случая, когда первое слово 1 данных, пришедшее на входы 14 устройства, совпадает по времени с приходом последнего слова 8 предыдущего третьего потока данных, приходящих на входы 13, Сдвиг между соответствующими словами четвертых потоков данных составляет 2 тактовых периода.

В этом случае устройство работает аналогично режиму 3, но адреса на выходе счетчика 41 изменяются в пределах от А +1 до А,+3, Фо рмул а

7 )458 из обретения

). Устройство для ввода данных, содержащее три мультиплексора, два блока памяти, первый регистр, узел

- управления и генератор тактовых сигналов, первый выход которого соединен с синхронизирующим входом узла уп.равления, первая и вторая группы выходов первого мультиплексора соединены соответственно с информационными входами первого и второго блоков памяти, выходы которых соединены соответственно с первой и второй группами информационных входов второго мультиплексора, управляющие входы первого и второго мультиплексоров соединены соответственно с первым.и вторым выходами узла управления, о тл и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей устройства за счет организации режима автоматического выравнивания двух синхронных сдвинутых во времени 25 потоков данных, в него введены четвертый мультиплексор, второй регистр, узел адресации и триггер, причем выход триггера соединен с информационным входом второго регистра, вторая и gg третья группы информационных входов второго регистра соединены соответственно с первой и второй группами выходов четвертого мультиплексора, пер1 вая и вторая группы информационных входов которого соединены соот35 ветственно с группами выходов второго мультиплексора и первого регистра, первая и вторая группы выходов третьего мультиплексора соединены соответственно с информационными входами первого мультиплексора и первого регистра, первая и вторая группы информационных входов третьего мультиплексора являются соответственно информационными входами устройства, первая и вторая группы выходов второго регистра являются информационными выходами устройства, выход второго регистра является выходом готов50 ности устройства, .первый и второй входы режима узла управления являются управляющими входами готовности устройства, входы управления режимом первого и второго блоков памяти сое55 динены соответственно с первым и вторым выходами узла управления, входы выбора блоков памяти соединены с вторым выходом генератора тактовых сиг87) 8 налов, группы адресных входов блоков памяти соединены с группой выходов узла адресации, управляющие входы, третьего и четвертого мультиплексоров соединены с третьим выходом узла управления,, четвертый, пятый и шестой выходы которого соединены соответственно с информационным входом, триггера, первым синхронизирующнм входом и входом сброса узла адресации, выход которого соединен со счетным входом узла управления, синхронизирующие входы первого и второго регистров и триггера соединены с первым выходом генератора тактовых сигналов, синхронизирующим выходом устройства и вторым синхронизирующФ4 входом узла адресации.

2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что узел управления содержит мультиплексор,че" тыре триггера, два элемента ИЛИ, элемент ИСКЛ)ОЧАЮЩЕЕ -KIH и регистр, причем первый и второй информацион-, ные входы регистра являются первыми вторым информационными входами узла, синхронизирующий вход регистра является синхронизирующим входом узла, первый и второй выходы регистра соединены с первым и вторым информационными входами мультиплексора, информационный вход первого триггера соединен с первым входом первого элемента ИЛИ и с первым информационным входом узла, второй вход первого элемента ИЛИ соединен с вторым информационным входом узла, счетный вход которого соединен с синхронизирующим входом второго триггера, прямой и инверсный выходы которого являются соответственно первым и вторым выходами узла, управляющий вход второго триггера соединен с выходом второго элемента ИЛИ, первый вход которого соединен с первым выходом,мультиплексора и со счетным входом третьего триггера, выход первого триггера соединен с управляющим входом мультиплексора и является третьим выходом уз, ла, второй выход мультиплексора соеди" нен со счетным входом четвертого триггера и вторым входом второго элемента KIH и..является четвертым выходом узла, первый и второй входы и выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с выходами третьего и четвертого триггеров и пятым выходом узла, выход первого элемента

1458871

ИЛИ соединен с синхрониэирующим входом первого триггера, входами сброса третьего и четвертого триггеров и является шестым выходом узла.

3. Устройство по п. 1, о т л и— ч а ю m е е с я тем, что узел адресации содержит два регистра, элемент

НЕ, триггер, счетчик, схему сравнения и мультиплексор, причем выход мультиплексора является выходом узла, второй синхронизирующий вход которого соединен со счетным входом счетчика и инверсным информационным входом мультиплексора, прямой информационный вход которого соединен с выходом схемы сравнения и входом разрешения записи счетчика, вход разрешения счета счетчика и управляющий вход мультиплексора соединены с выходом триггера, синхронизирующий вход которого соединен с синхрониэирующим входом первого регистра, входом элемента НЕ и первым синхрониэирующим входом узла, вход сброса которого соединен с входом сброса триггера, выход элемента HE соединен с синхронизирующим входом второго регистра и входом разрешения схемы сравнения, группа выходов первого регистра соединена с группой информационных входов счетчика, группа выходов которого соединена с группами информационных входов первого и второго регистров и первой группой входов схемы сравнения и.группой выходов узла,вторая группа входов схемы сравнения соединена с группой выходов второго регистра.

1458871

1" ? 37 4 5у апнц

17

Фиг.5

li 4 5 8е

14 ? l A 4е 2» Si

St

Stff3l 1 ? 2у 5 8 1

ÔS Ь

ДаиИ1

il il +Я 1 il

° 7 +2 Ф

ar.нИ

Юаи Ж1. ак гИ7 Baw463t

1т ? Х 4 5р

Л +1 A 1 Л i1 Ле

1 7 Ji 4 Sg

Л .Р.? iS i4 Ь, т 2+S Л,ФЛИ3% ФЛ:ИЭ,ЙМЭ ФЮ ИЛ ФЛ

Arz 867 аим37 даи 4611

Au263f

S 1 ? i 4е S 2