Устройство для контроля интегратора

Иллюстрации

Показать всеРеферат

Изобретение относится к области технической диагностики, в частности к функциональному диганостированию динамических звеньев. Целью изобретения является повьппение достоверности контроля интегратора. Указанная цель достигается за счет использования линейной аппроксимации реального выходного сигнала интегратора на малом временном интервале. Для этого введены сумматор 6, компаратор 7, источник пороговых напряжений 8, элемент НЕ 11, аналоговый ключ 4, делитель частоты 3. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5ц 4 -С 06 С 7/186

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCH0MV СВИДЕТЕЛЬСТВУ

9 ив 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

IlO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР (21) 4273852/24-24 (22) 30.06.87 (46) 15.02.89. Бюл. Ф 6 (72) С.В. Кочетков и P.Н. Лопарев (53) 681.335(088.8) (56) Прагер И.Л . Электронные аналоговые вычислительные машины. М.: Машиностроение, 1979, с. 73-74, рис. 44, табл. 3,4.

Гутников В.С. Применение операционных цеплителей в измерительной технике. Л.: Энергия, 1975, с,90-93, рис. 40а.

„.SU„„1458877 А1 (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНТЕГРАТОРА (57) Изобретение относится к области технической диагностики, в частности к функциональному диганостированию динамических звеньев. Целью изобретения является повьппение достоверности контроля интегратора. Указанная цель достигается за счет использования линейной аппроксимации реального выходного сигнала интегратора на малом временном интервале. Для этого введены сумматор 6, компаратор 7, источник пороговых напряжений 8, элемент

HE 11, аналоговый ключ 4, делитель частоты 3. 2 ил.

1458877

Изобретение относится к области технической диагностики,в частности к функциональному диагностированию динамических звеньев, и может использоваться в промышленности средств связи

Целью изобретения является повышение достоверности контроля интегратора.

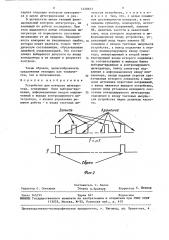

На фиг. 1 показана блок- схема устройства; на фиг. 2 — временная диаграмма, поясняющая работу схемы.

Устройство содержит контролируемый интегратор 1, являющийся об»ьектом контроля и подключенный к информационному входу 2 устройства, делитель. 3 частоты, подключенный к входу установки исходного состояния интегратора 1, аналоговый ключ 4, блок 5 выборки-хранения, сумматор

6, компаратор 7, источник 8 пороговых напряжений, выход 9 устройства, вход 10 тактовых импульсов и элемент НЕ 11.

Устройство работает следующим образом.

В начале цикла интегрирования происходит установка нулевых (а в общем случае и ненулевых) начальных условий путем подачи импульса Т на вход интегратора 1. Этот импульс формируется от импульсной последовательности Т, поступающей на вход делителя 3 с коэффициентом деления и, т.е.

А

Т = nT (см. фиг. 2) . При этом соответствующий импульс высокого логического уровня и длительностью приходит на вход управления режимом работы блока 5 выборки и хранения, разрешая запись начального значения напряжения на выходе интегратора 1.

Одновременно низкий логический уровень, поступающий с выхода элемента

НЕ 11 на управляющий вход ключа 4, закрывает. последний. На вход сумматора б поступают два равных по величине напряжения, которые суммируются с разными знаками, в результа+

1 те чего Кс(К =О) R,. Это соответствует низкому уровню сигнала S на выходе 9. По окончании времени на входе установки в исходное состояние интегратора 1 устанавливается низкий уровень, который снимает режим установки начальных условий.

Этот же уровень по входу управления блока 5 запрещает запись значений сигнала Бвь,х c выхода: интегратора l и переводит блок 5 в режим хранения.

Кроме того, инверсия этого низкого уровня с элемента НЕ ll поступает

5 на управляющий вход ключа 4, открыI вает его, и сигнал U „с входа 2 устройства поступает на вход сумматора 6., На два других входа сумматора б приходят текущие значения U „х и заполненное значение с выхода блока 5.

Как известно, приращение выходного сигнала интегратора hUsb,„ýà

° .время (Т-ь) можно определить из

15 соотношения: дщ»»в» (T-ñ ) 0„„, „„,- — постоянная инте»грир6вания, а знак минус отражает инвертирующие свойства операционного усилителя. где

Тогда (Т- )

Таким образом, считая величину. К поII стоянной на всем промежутке Т, можно аппроксимировать приращение интегральной зависимости на участке

30 (Т-Г) линейной функции. Для этого сигнал U „ с-входа 2, поступающий через открытый ключ 4, необходимо просуммировать с коэффициентом К на сумматоре 6 с разностью текущего и запомненного сигнала U „,„„. .Тогда с учетом инверсии U > no отношению

»

Бв j x имеем

40 R4 " 11вьи 11вых(,1 + KUaxt y где ивхФ

U,„: — соответственно текущие значения входного и вы45 ходкого сигнала интегратора 1;

11, х(1 — запомненное значение поступающее с выхода блока 5.

Если интегратор I функционирует правильно, то сигнал R<- в данном слу+ чае не будет выходить за допуски К„ и К, которые учитывают погрешность аппроксимации, т.е. на выходе

9 будет низкий уровень сигнала S, При нарушении работоспособности интегратора 1 Rt перейдет границы допусков и на выходе 9 появится высокий уровень сигнала S. Такая элеменз 14 тарная операция контроля повторяется в цикле интегрирования и раз.

В результате имеем текущий функциональный контроль интегратора, не влияющий на работу последнего. При этом выделяются любые отклонения интегратора от нормального состояния независимо от их природы. Периодич-ность контроля не увеличивает ошибку которая может включать только методическую составляющую, обусловленную линейной аппроксимацией. Эта составг ляющая выбирается допуском на входе компаратора и не входит в результат контроля, 58877 пульсов устройства, о т л и ч а ющ е е с я тем, что, с целью повышения достоверности контроля, в него введены сумматор, компаратор, источник пороговых напряжений, элемент

НЕ, делитель частоты и аналоговый ключ, вход которого подключен к информационному входу устройства, yn, 1p. равляющий вход через элемент НЕ соединен с входом тактовых импульсов устройства, а выход подключен к первому неинвертирующему входу сумматора, инвертирующий и второй неин1Б вертирующий входы которого подключены соответственно к выходам блока выборки-хранения и контролируемого интегратора, выход. сумматора подключен к информационному входу комgp паратора, входы задания порогов срабатывания которого соединены с выходами источника пороговых напряжений, а выход является выходом устройства, причем вход установки исходного сос25 тояния контролируемого интегратора. подключен к входу тактовых импуль- . сов устройства через делитель частоты.

Таким образом, целесообразность предложения очевидна как технически, так и экономически.

Фо рмула изо б ре тения

Устройство для контроля интегратора, содержащее блок выборки-хранения, информационным входом подключенный к выходу контролируемого интегратора, а входом управления режимом работы — к входу тактовых имЯалисъ

Хранение

T=nl

Фиг 2

Составитель С. Белан

Техред A.Кравчук . Корректор С. ШекмаР

Редактор О. Спесивых

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

Заказ 345/53 Тираж бб7 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГЕНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4!5