Устройство для определения ортогональной составляющей вектора

Иллюстрации

Показать всеРеферат

СО!ОЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

151) 4 G 06 G 7/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ . H ABTOPCHQMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

-llO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 3967696/24 — 24 (22) 2! . 1 О. 85 (46) 15.02.89. Вюл. К- 6 (71) Смоленский филиал Московского энергетического института (72) А.M. Ковалев, В.В. Круглов и Г.Д. Панин (53) 681.3(088.8) (56) Авторское свидетельство СССР

N - 771678, кл. G 06 G 7/12, 1978.

Авторское свидетельство СССР

Ф 894734, кл. С 06 G 7/20, 1980. (54)(57) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ

ОРТОГОНАЛЬНОЙ СОСТАВЛЯЮЩЕЙ ВЕКТОРА, содержащее первый интегратор, первый переключатель и элемент сравнения, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, устройство содержит второй интегратор, инвертор, второй, третий, четвертый и пятый переключатели, сумматор и блок управления, содержащий счетчик и дешифратор, соединенные последовательно, при этом вход задания модуля вектора устройства соединен с первым входом сумматора и с первым входом первого переключателя, выход

Изобретение относится к аналоговой вычислительной технике и может найти применение для получения ортогональной составляющей вектора, заданного модулем и второй составляющей, например в навигационных системах.

Цель изобретения — повышение быстродействия.

„„SU„„1458878 А 3 которого соединен с первым входом элемента сравнения, вход задания известной ортогональной составляющей вектора устройства соединен с вторым входом первого переключателя и с первым входом второго переключа— теля, выход которого соединен с вто-. рым входом сумматора, третий вход первого переключателя соединен с шиной нулевого потенциала, вход первого интегратора соединен через третий переключатель с шиной задания постоянного напряжения и с шиной нулевого потенциала, выход первого интегратора через инвертор соединен с вторым входом второго переключа— теля, второй вход элемента сравнения соединен через четвертый переключатель с выходами первого и второго интеграторов, вход второго интегратора через пятый переключатель соединен с выходами сумматора и с шиной нулевого потенциала, вы— ход элемента сравнения соединен с входом счетчика, а соответствующие выходы дешифратора соединены с управляющими входами переключателей.

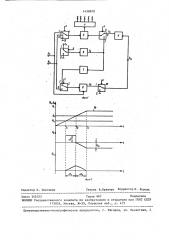

На фиг. 1 изображена схема .устройства; на фиг. 2 — временные диаГраммы.

Устройство содержит первый переключатель I, второй переключатель 2, элемент 3 сравнения, блок 4 управления, третий переключатель 5, первый интегратор 6, инвертор 7, четвертый переключатель 8, сумматор 9, пятый з

14588 переключатель 10, второй .интегратор

11. Блок 4 управления содержит счетчик и дешифратор.

Устройство работает следующим об-.

5 разом.!

В первом такте под воздействием сигналов, вырабатываемых блоком 4 управления, третий 5 и четвертый 8 10 переключатели переводятся в положение I второй переключатель 2 в положение II, таким же в начале данного такта оказывается и положение переключателей 1 и 10, Вследствие этого на элемент 3 сравнения подаются два напряжения U — известной ортогональной составляющей и линейно нарастающее U К t напряжеО <

K, — крутизна интегратора 6, t — текущее время). В момент сравнения этих напряжений С< = Uñ /K0 U срабатывает элемент 3 сравнения, под воздействием сигнала, формируемого блоком

4, переключатель 1 переводится в по- ложение Х. После этого элемент, 3 сравнения фиксирует момент t

= и /к„v,. зо

В этом же такте на время <

Напряжение Б имеет величину

К (1м + 1с, ) где K — коэффициент передачи сумматора, поэтому по окончании первого такта выходное напряжение второго интегратора 11, име- 4р ющего крутизну Кц, определяется соот-1, << 1 ношением U« = К< дt, У = К,< К> х (11м Uc, ) /1-1

78

Во втором такте переключатель переводится в положение III, переключатель 2 в положение I при этом выходное напряжение сумматора 9 имеет вид линейно изменяющегося от нуля, а напряжение на выходе интегратора 11 уменьшается по параболическому закону. Момент 1, когда данное напряжение становится равным нулю, Фиксируется элементом 3 сравнения. Интервал ht определяется равенством

5t /к„, и,.

В момент t переключатель 5 перез водится в положение II и интегратор . б переводится в режим памяти (положение переключателей 2 и 10 сохраняется прежним), На выходе устройства при этом оказывается напряжение, равное искомой ортогональной составляющей Ц

2. 2

U U при соответствующем

< выборе масштаба сумматора.

Простейший вариант блока управления представляет собой трехразрядный триггерный счетчик и дешифратор, при этом нулевая комбинация счетчика используется для приведения устройства в исходное состояние (сброс интеграторов)

По команде пуска в счетчик записывается комбинация 001, которая сохраняется до момента t< ° Далее при поступлении от элемента 3 сигнала в счетчике Фиксируется комбинация 01 0, затем в момент t она переходит в комбинацию 011, а в момент t код в счетчике становится равным 100, соответствуя режиму. хранения результата. Дешифратор переводит указанные комбинации в управляющие сигналы в соответствии с описанной логикой управления переключателями.

1458878 и,, Фиг. Я

Техред A. Кравчук Ko ppe K то p H° . Король г

Редактор О. Спесивых

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

Заказ 345/53 Тираж 667 Подписное БНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5