Запоминающее устройство с сохранением информации при отключении питания

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в системах -управления, к которым гфедъявляется требование по сохранению информации в оперативном запоминающем устройстве при аварийном отключении питания. Цель изобретенияповьпление надежности устройства за счет исключения воздействия помех, возникающих при отключении и включении основного питания, на функционирование блока оперативной памяти. Во время действия помех формирователь 6 вырабатывает сигнал запрета, поступающий на ключ 7, который осуществляет блокировку выполнения режима выборки в блоке 1 оперативной памяти, хране1ше информации в котором обеспечивается за счет энер1лии резервного источника 2 питания. В рабочем режиме функционирование устройства обеспечивается основны источником 3 питания , подключаемым к блоку 1 оперативной памяти через эле.зент 4 развязг.- ки, и возможностью прохождения сигналов выборки через ключ 7 на вход бло- jKa 1 оперативной памяти. 2 ил. е (Л с 4 П 00 00 (О.. ю

СОЮЗ СОВЕТСКИХ социАлистичесних

РЕСПУЬЛИН

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОЬРЕТЕНИЯМ И ОТКРЦТИЯМ

ПРИ ГКНТ СССР (21) 4095624/24-24 (22» 24.07.86 (46) 15.02 ° 89. Бюл. Р 6. (72) С.И.Борзенков, У.Г.Латыпов и И.В.Иузалев (53) 681.327 (088.8) (56) Авторское свидетельство СССР

Р 1116461, кл. С 11 С 29/00, 1982, Авторское свидетельство СССР

У 1179436, кл. G 11 С 29/00, 1983. (54) ЗАПОЬЯНАЮЩЕЕ СтРОйСтВО С СОХРАНЕНИЕМ ИНФОРИЙЦИ ПРИ. ОТКЛЮЧЕНИИ

ПИТАНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано в системах управления, к кото- рым предъявляется требование по сохранению информации в оперативном запоминающем устройстве при аварийном отключении питания. Цель изобретения(19) U (ill 1 458892 ш@G11С29/ОО,С06F1216 повышение надежности устройства за счет исключения воздействия помех, возникающих при отключении и включении основного питания, на функционирование блока оперативной памяти.

Во время действия помех формирователь

6 вырабатывает сигнал запрета, поступающий на ключ 7, который осуществляет блокировку выполнения режима выборки в блоке 1 оперативной памяти, хранение информации в котором обеспечивается за счет энергии резервного источника 2 питания. В рабочем режиме функционирование устройства обеспечивается основным источником 3 питания, подключаемым к блоку 1 оперативной памяти через элемент 4 развяз= ки, и возможностью прохождения сигналов выборки через ключ 7 на вход блока i оперативной памяти. 2 ил.

1458892

Изобретение относится к вычислительной технике и может быть использовано в системах управления, к которым предъявляются требования по сох ранению информации в оперативном запоминающем устройстве при аварийном отключении питания.

Целью изобретения является повышение надежности устройства.

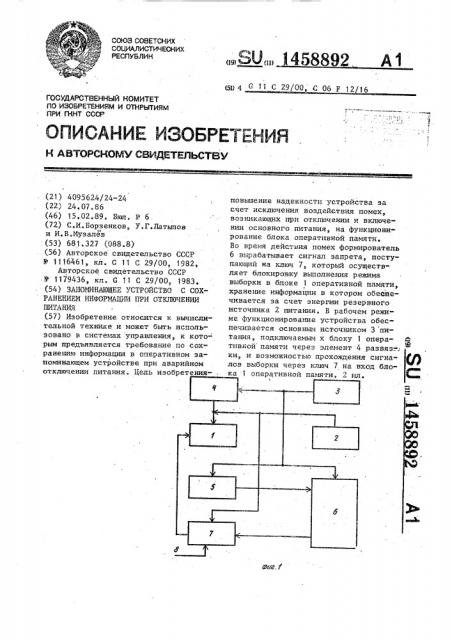

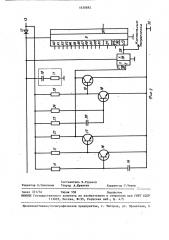

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 — принципиальная схема устройства для одного разряда, выполненного на базе микросхемы 537РУ2А.

Устройство содержит блок 1 оперативной памяти, резервный 2 и основной

3 источники питания, элемент 4 развязки, элемент 5 задержки, формиро" ватель 6 сигнала запрета, ключ 7 и вход 8 сигнала выборки.

Устройство, реализованное для одного разряда (см. фиг.2), содержит микросхемы 9 памяти (на фиг. 2 пока" зана микросхема типа 537РУ2А), ре-.:> зервный источник питания выполненный на конденсаторе 10 и резисторе

11, элемент развязки, выполненный на диоде 12, шину 13 основного питания (основной источник питания не локазан), элемент задержки, выполненный на конденсаторе 14 и резисторе 15, формирователь сигнала запрета, вы-, полненный на транзисторах 16-19, входящих в сборку НТ251, конденсаторе

20 и резисторах 21-25, ключ, выполненный на микросхеме 26: типа 564КТЗ, имеющей входы 27, 28 и выход 29, шину 30 нулевого потенциала.

Устройство работает следующим образом.

При отключении и включении основного питания формирователь 6 вырабатывает сигнал, блокирующий передачу .через ключ 7 сигнала выборки,на микросхему 9 памяти.

В момент отключения питания отрицательный потенциай, вызванный разрядом конденсатора 2Р прикладывается к базе транзистора 18, вызывая

его быстрое закрытие и открытие транзистора 19, обеспечивающего появление блокирующего (низкого) потенциала на входе 28 микросхемы 26, При окончательном отключении питания . данный потенциал на входе 28 поддерживается путем его выдачи через резистор 22.

30 .Формула изобретения

5

IS

При включении основного питания блокирующий потенциал на входе формирователя 6 удерживается до тех пор, пока не зарядится конденсатор 14 элемента задержки и не вызовет открытие транзистора 16, потенциал на коллек- . торе которого обеспечит закрытие транзистора 17, шунтирующего транзистор 19.

Во время действия сигнала запрета как сигнал выборки, так и помехи, возникающие на входе 27 микросхемы

26, не проходят в микросхему 9 памяти. Блок оперативной памяти находится в режиме невыборки и поэтому помехи i возникающие на адресных, информационный и управляющих шинах, не.оказывают на него отрицательного влияния. . При отсутствии сигнала запрета блок 1 оперативной памяти управляется сигналами выборки, поступающими с входа 8 в ключ 7 на вход 27микросхемы

26 и далее на микросхемы 9 памяти.

Поскольку ключ 7 (микросхема 26) запитывается от резервного источника питания, то в момент отключения ! (включения) основного питания генерация помехи на вьисоде 29 исключается °

Запоминающее устройство с сохранением информации при отключении питания, содержащее блок оперативной памяти, резервный и основной источники питания, элемент развязки и элемент задержки, причем вход питания блока оперативной памяти соединен с, выходом резервного источника питания и выходом элемента развязки, вход которого подключен к выходу основного источника питания и входу элемента задержки, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, оно содержит, формирователь сигнала запрета и ключ, выход которого соединен с входом обращения блока оперативной памяти, информационный вход ключа является входом сигнала выборки устройства, вход питания ключа соединен с выходом резервного источника питания, управляющий вход ключа соединен с. выходом формирователя сигнала запрета, вход питания которого соединен с выходом основного источ ника питания, информационный вход формирователя сигнала запрета подключен к выходу элемента задержки.

1458892

Составитель В.Рудаков

Редактор О.Спесивых Техред А.Кравчук Корректор C. 1åðíè

Заказ 371!54 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4