Устройство для преобразования импульсного сигнала по длительности

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в автоматических телефонных станциях. Цель изобретения - повышение быстродействия за счет устранения задержки появления импульсов на выходе при одновременном расширении функциональных возможностей за счет обеспечения возможности преобразования импульсов с длительностями больше и меньше пороговой в импульсы с двумя фиксированными значениями длительности . В устройство, содержащее инвертор 8, детектор 5 нулевогд значения, пороговый детектор 4 и интегратор 1, введены электронный ключ 7, элемент ИЛИ 6, формирователь 9 переднего фронта импульса и резисторы 13, 14. При поступлении, входного импульса шину 10 напряжение на выходе интет i (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИК

„,Я0„„1458966 . A t (д1) 4 Н 03 K 5/153

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPGH0MV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4268314/24-21 (22) 22.06.87 (46) 15.02.89. Бюл. ¹- 6 (71) Научно-исследовательский институт ВЗФ (72) С.И.Колесников и Ж.С.Жмурина (53) 621.374 (088.8) (56) Патент США № 3668423, кл. Н 03 К 5/153, 1973.

Патент Японии ¹ 60-134624, кл. Н 03 К 5/153, 1985. (54) УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ

ИМПУЛЬСНОГО СИГНАЛА ПО ДЛИТЕЛЪНОСТИ (57) Изобретение относится к импульсной технике и может быть использовано в автоматических телефонных станциях, Цель изобретения — повышение быстродействия эа счет устранения задержки появления импульсов на выходе при одновременном расширении функциональных возможностей эа счет обеспечения возможности преобразования импульсов с длительностями больше и меньше пороговой в импульсы с двумя фиксированными значениями длительности. В устройство, содержащее инвертор

8, детектор 5 нулевого значения, по роговый детектор 4 и интегратор t, введены электронный ключ 7, элемент

ИЛИ 6, формирователь 9 переднего фронта импульса и резисторы 13, 14.

При поступлении, входного импульса на шину 10 напряжение на выходе инте лем 9. Выходной импульс имеет длительность t. Если напряжение с интегратора 1 переходит в нулевой уровень до окончания входного импульса, пороговый детектор 4 возвращается в исходное состояние позже, и длительность выходного импульса равна 2t. Шина 11 служит для блокировки ° 2 ил.

1458966 гратора 1 сначала быстро уменьшается, а после срабатывания порогового детектора 4 медленно нарастает. Если это напряжение переходит нулевой уровень после-окончания входного импульса, то пороговый детектор 4 возвращается в исходное состояние импульсом, формируемым детектором 5 и формировате1

Изобретение относится к импульсной технике и может быть использовано в электронных автоматических телефонных станциях для приема и анализа сигналов управления. S

Цель изобретения —. повышение быстродействия sa счет устранения saдержки появления импульсов на выходе при одновременном расширении функциональных возможностей путем обеспе- 10 чения возможности преобразования импульсов с длительностями больше и меньше пороговой в импульсы с двумя фиксированными значениями длительности. 15

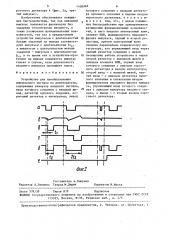

На фиг. 1 показана схема предлагаемого устройства на фиг. 2 — временные диаграммы работы устройства.

Устройство содержит. интегратор с первым 2 и вторым 3 времяэадающими 20 резисторами, пороговый детектор 4, детектор 5 нулевого значения, элемент ИЛИ 6, электронный ключ 7, инвертор 8 входного сигнала, формирователь 9 переднего фронта импульса, входную шину 10 устройства, шину 11 блокировки работы устройства, выходную шину 12 устройства, первый и второй резисторы 13 и 14.

Выход интегратора 1 подключен к первому входу порогового детектора

4 и входу детектора 5. Первый вход элемента ИЛИ 6 соединен с выходом порогового детектора 4 и входом интегратора 1, второй вход — с входной 35 шиной 10, а третий вход - с выходом детектора 5 и сигнальным входом формирователя 9, выход которого соединен с вторым входом порогового детектора 4. Управляющий вход формирователя 40

9 соединен с выходом инвертора 8.

Электронный ключ 7 подключен параллельно конденсатору в интеграторе 1.

Управляющий вход электронного ключа

7 подключен через первый резистор 13 к выходной шине 12 и через второй резистор 14 к шине 11.

Интегратор 1 выполнен на операционном усилителе с времязадающим конденсатором в цепи обратной связи усилителя и двумя времязадающими резисторами 2 и 3. Первый времязадающий резистор 2 служит для задания значения временного интервала t<, времени действия помехи. Второй времязадающий резистор 3 определяет временной интервал, т.е. заданную длительность выходного сигнала.

Пороговый детектор 4 выполнен на операционном усилителе по схеме регенеративного комнаратора — триггера

Шмитта и предназначен для сравнения величин напряжений на выходе интегратора 1 и его входе. Детектор 5 выполнен на операционном усилителе с разомкнутой петлей обратной связи и служит для останова работы устройства, Элемент ИЛИ 6 выполнен на диодах и работает от сигналов отрицательной полярности.

Электронный ключ 7 выполнен на полевом транзисторе и предназначен для запуска и останова работы устройства.

Инвертор 8 входного сигнала выполнен на биполярном транзисторе р-п-рструктуры и служит для подачи напряжения положительной полярности (в ,момент действия входного сигнала) на управляющий вход формирователя 9 переднего фронта импульса, выполненного как RC-дифференцирующая цепь и предназначенного для возврата по1458955

25

55 рогового детектора 4 в исходное состояние.

Устройство работает следующим образом.

В исходном состоянии вход и выход интегратора 1 замкнуты с помощью электронного ключа 7 и поэтому напряжение на его выходе близко к нулю.

Напряжение на выходе порогового детектора 4 имеет положительную полярность, так как цикл работы устройства заканчивается на этом его состоянии, Напряжение на выходе детектора

5 нулевого значения имеет положительную полярность по той же причине, Так как на входной шине 10 напряжение имеет положительную полярность, на выходной шине 12 напряжение также имеет положительную полярность, поэтому затвор полевого транзистора смещен в прямом направлении и электронный ключ 7 замкнут (фиг. 2a,g) .

Под воздействием входного импульсного сигнала электронный ключ 7 размыкается. При этом на выходной шине 12 появляется отрицател ьный потенциал входного сигнала °

Напряжение на выходе интегратора

1 начинает убывать по линейному закону (фиг. 2 ). Крутизна изменения напряжения определяется величиной входного напряжения интегратора 1, величиной времязадающего резистора 2 и емкостью конденсатора в интеграторе

1. Сопротивление времязадающего резистора 2 в несколько раз меньше сопротивления времязадающего резистора

3, Как только напряжение на выходе интегратора 1 по величине становится равным порогу срабатывания порогового детектора 4, напряжение на выходе последнего скачком достигает отрицательного значения (фиг. 2 ь) . Напряжение на выходе интегратора 1 начинает линейно нарастать (фиг. 2F) со скоростью,. определяемой величиной времязадающего резистора 3. По достижении напряжением на выходе интегратора 1 нулевого значения срабатыва-. ет детектор 5 (фиг. 2г). Напряжение на его выходе скачком достигает отрицательного значения. Из этого перепада напряжений формирователь 9 переднего фронта формирует короткий импульс отрицательной полярности. Если на входной шине 10 импульсный сигнал уже закончился, то данный короткий импульс воздействует на вход порогового детектора 4 и возвращает его в исходное состояние (первый импульс на фиг. 2ч), после чего йалряжение на выходе интегратора 1 лересекает нулевой уровень в обратном направлении, напряжение на выходе детектора 5 и на выход-. ной шине 12 становится положительным, электронный ключ 7 замыкается. На выходной шине 12 формируется импульсный сигнал длительностью (фиг. 2, ) . Если входной импульс еще не закончился, то короткий импульс с выхода формирователя 9 не воздействует на вход порогового детектора 4, так как напряжение положительной полярности с выхода инвертора 8 запирает формирователь 9. Напряжение на выходе интегратора 1 продолжает расти уже в положительной области полярностей до достижения порога срабатывания порогового детектора 4, который при этом возвращается в исходное состояние.

После этого напряжение на выходе интегратора 1 начинает линейно спадать и при достижении им нулевого значения напряжение на выходе детектора 5 нулевого значения достигает положительного значения, электронный ключ 7 замыкается. При этом длительность выходного импульса равна

2 (второй импульс на фиг. 2 ).

Если необходимо запретить работу преобразователя длительности, например, при приеме импульсов набора номера, на шину 11 подается положительный потенциал, достаточный для

40 замыкания электронного ключа 7 . фиг ° 2а,четвертый импульс) .При этом входные импульсы передаются на выходную шину без изменения длительности.

Таким о бра эом, пр едл ar аемое ус тройство различает по длительности два импульсных сигнала, разность длительностей которых может быть очень мала. Разрешающая способность по длительности для устройства-прототипа и предлагаемого устройства практически одинакова.

Если на вход устройства воздействуют импульсы помех, длительность которых меньше заданной величины t,, то на выходе устройства они появляются без изменения длительности, так как напряжение на выходе интегратора

1 не достигает порога срабатывания по.

1458966

Формула изобр етения

Устройство для преобразования импульсного сигнала по длительности, содержащее инвертор входного сигнала, вход которого соединен с входной шиной, детектор нулевого значения, пороговый детектор и интегратор, выход

Составитель А. Смирнов

Редактор А.Лежнина Техред М.Дидык Корректор И.Муска

Заказ 378/58 Тираж 879 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная, 4

5 рогового детектора 4 (фиг. 2а, третий импульс) .

Изобретение обеспечивает повышение быстродействия, так как выходной импульс появляется фактически без задержки относительно входного, а также расширение функциональных возможностей, так как в предлагаемом устройстве импульсам с длительностью больше заданнрй на выходе соответствуют импульсы с длительностью 2 а импульсом с длительностью меньше заданной — импульсы с длительностью в .то время как в устройстве-прототипе на выходе появляется импульс только в случае, если длительность входного импульса превышает порог. которого соединен с входами детектора нулевого значения и первым входом порогового детектора, о т л и ч а ющ е е с я тем, что, с целью повышения. быстродействия при одновременном расширении функциональных возможностей, в него введены электронный ключ, элемент ИЛИ, формирователь переднего

10 фронта импульса, первый и второй резисторы, причем электронный ключ включен параллельно конденсатору интегратора, его управляющий вход через первый резистор соединен с шиной

15 блокировки работы устройства и через второй резистор с выходной шиной и выходом элемента ИЛИ, первый вход которого соединен с выходом порогового детектора,и входом интегратора, 20 второй вход — с входной шиной, третий вход — с выходом детектора нулевого значения и сигнальным входом формирователя переднего фронта импульса, управляющий вход которого соединен с выходом инвертора входного сигнала, а выход — с вторым входом порогового детектора.