Устройство для выполнения преобразования координат

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении специапизиро-, ванных ЭВМ. Целью изобретения является расширение области применения . за счет выполнения преобГ)азования в экспоненциальном масштабе. Устройство преобразует декартовые координаты в полярные с компенсацией изменения масштаба координат вектора и, . кроме того, позволяет .вычислять функцию М Х.. Для этого в устройство , содержащее три регистра, три сумматора-вычитателя, два сдвигателя, первый блок памяти, введены четвертый регистр, четвертый и пятый сумматоры-выч11татели, вычитатель, .второй блок памяти, 1 ил. S

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (59 4 С 06 Р 7/548

gpf < ."., t, лЯ

AATEH7! ..-:. -лЕС1-;АД

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTGPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР (21) 4278?77/24-24 (22) 06.07.87 (46) 28.02.89. Бюп. Р 8 (71) Кировский политехнический институт (72) И.В.Санников и А.Н.Чуватин (53) 681.325 (088.8) (56) . Рабинович 3. Л., Раманаускас В.А.

Типовые операции в вычислительных машинах. — Киев., Техника, 1980, с. 220, 236*

Байков В.Д., Смолов В.Б. Апнаратурная реапиэация элементарных функций в ЦВМ вЂ”.Л.: из-во Ленинградского университета, 1975 - с. 19, 71

{прототип) (54) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ПРКОБРАЗОВЬКИЯ КООРДИЯАТ

Изобретение относится к вычислительной технике и может бить использовано при построении специализированных ЗВМ.

В предлагаемом изобретении приводится техническое решение задачи пре. образования декартовйх координат в полярные с одновременным умножением координат вектор;. на экспоненту, т.е. вычисления выражений сдедука1е-. го вида: т а l

М е (X+Y}

А - arcing (Y/Õ) где Х,Т вЂ” декартовы координаты(абсциссаа и ордин ат а1 вектора;

„„Я0„„1462299 А 1 (57) Изобретение относится к вычислительной технике и может быть использовано при построении специализиро-, ванных ЭВМ. Целью изобретения явля- ется расширение области применения эа счет выполнения преобразования в экспоненциальном масштабе. Устройство преобразует декартовые координаты в полярные с компенсацией изменения масштаба координат вектора и, кроме того, позволяет:вычислять т функцию М = Х,е, Для этого в устройство, содержащее три регистра, три сумматора-вычитателя, два сдвигателя, первый блок памяти, введены четвертый регистр, четвертый и пятый а

Ж сумматоры-вычит атели, вычит атель „ . второй блок памяти. 1 ил.

2 Феи

M,А — полярные координаты (мо- ф дуль и аргумент) вектора; CO

Т вЂ” аргумент экспоненты.

При Т = 0 выполняется преобразование декартовых координат в по- цр лярные с компенсацией изменения масш- р таба координат.

Целью изобретения является расширение области применения устройства за счет возможности преобразования в экспоненциальном масштабе.

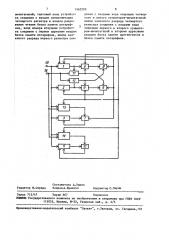

На чертеже представлена блок-схема предлагаемого устройства для выполнения преобразования координат, Устройство для выполнения преобразования координат содержит регистры 1-4, сумматоры-вычитатели 5-9, 62299

Сг . = arctg (Y/X);

3 14 вычитатель 10 сдвигатели 11 и 12, . блоки 13 и 14 памяти арктангенсов и логарифмов, тактовый вход 15, вход

16 номера итерации.

Введем следующие обозначения, поясняющие работу устройства: А„, В„ ордината и абсцисса вектора, повернутые на угол С„; D переменная алгоритма, используемая для преобразования аргумента экспоненты на л-ом шаге; Е„С )-I + 1) — оператор направления изменения аргумента вектора на л-ом шаге алгоритма; Р»б (-1 +1) оператор направления изменения мо дуля вектора на л-ом шаге алгорит ма; л — сквозной номер шага от начала вычислений; к — номер выполняемой итерации; n - количество разрядов в дробной части числа, количест: во выполняемых итераций; (n + 3) разрядность устройства, включая два разряда в целой части числа и знаковый.

Область определения функций: (14) (15) (16) D

2ni\

О е /arctg(Y/Х) /ы /4; (1) (2) (3) (4) А = Y

В; 4X.

С =О

Итер ации: л/2 для четных л

Результаты: (13) А д,,= О

О (Y) «1; I/г ««Х а1; О«(т) 1

Области значений функций:

Устройство реализует следующий алгоритм преобразования декартовых координат в полярные.

Начальные условия:

Е» ЗНАК (А») э (5)

Р„ЗНАК (Э„); (6)

Ал+< =А» + Р» А„2 -Е» л 2 j (")

В»+1 В»+Р» В» 2 +Е» А» 2,1 (")

С»+, С„+Е„. arctg(2 /(1+Р„2 ) (9)

D„< D»-О,51п(1+Р„2 +2 ) (10) где л 1,2,...,2n, (11) (л + 1)/2 для нечетных л; (12) При Т = 0 устройство выполняет преобразование декартовых координат Х и Y в полярные

Ь т

М = (Х + Y .) и А = arctg (Y/X) без искажения модуля вектора, а при

Y = О вычисляет функцию М Х е

В исходном положении (см. блоксхему устройства) в регистрах находятся следующие данные: в первом регистре 1 ордината вектора У; во втором регистре 2 абсцисса вектора Х; в третьем регистре 3 число О; в четвертом регистре 4 аргумент экспоненты Т.

Т аким о бр аз ом, р е ализ ов аны выр ажения (1 ) — (4) .

Устройство работает циклически.

26 На л-ом шаге на "тактовый вход 15 устройства подается синхросигнал, на вход номера итерации 16 устройства — номер К выполняемой итерации.

При этом двум синхросигналам соответЗО ствует одно значение номера выполняемой итерации, т.е. используются двойные шаги итераций в соответствии с выражениями (11} и (12). Под воздействием синхросигналов и номеров итераций в устройстве развивается вычислительный процесс.

Под воздействием каждого синхросигнала реализуется один шаг алгоритма в соответствии с выражениями (5) (l0).

Режимы работы(сложение или вычитание 1 третьего 7, четвертого 8, пятого 9 сумматоров-вычитателей задает сигнал с выхода знакового разряда первого регистра 1 - выражение (5) . Режимы работы (сложение или вычитание) первого 5 и второго 6 сумматоров-вычитателей задают сигнал с выхода знакового разряда четверто.

ro регистра 4. Этот же сигнал управляет выбором соответствующей константы в блоках 13 и 14 памяти— выражение (6).

В соответствии с номером выполняемой итерации в первом 11 и втором

12 сдвигателях выполняется сдвиг пре дыдущих значений соответственно ординаты А„и абсциссы В„вектора на

К разрядов вправо, т.е. на выходах

5 14622 первого 11 и второго 12 сдвигателей формируются величины соответственно

А„ ? и В„2 . Предыдущее значение ординаты вектора А„, ее прираще-к к " 5 ния А .2 и 8„2 поступают соответственно из первого регистра 1, первого 11 и второго 12 сдвигателей в цепь, состоящую из первого 5 и четвертого 8 сумматоров-вычитателей; в резульате в четвертом сумматоревычитателе 8 формируется новое значение ординаты вектора А„+,, которое фиксируется в первом регистре 1 выражение (7), Предыдущее значение 15 абсциссы вектора В„, ее приращения

-К . -К

В 2 и А„2 поступают соответственно из второго регистра 2, второго

12 и первого 11 сдвигателей в цепь, состоящую из второго 6 и пятого 9 2р сумматоров-вычитателей, в результате в пятом сумматоре-вычитателе 9 фор-. мируется новое з начение аб сциссы вектора В д+,, которое фиксируется во втором регистре 2 — выражение (8). 25

Предыдущее значение аргумента вектора С и арктангенсная константа

are tg (2 "/ (1 + Р„2 ) поступают соответственно из третьего регистра

3 и блока 13 памяти арктангенсов в третий сумматор-вычитатель 7, где формируется новое значение аргумента вектора Сд,, которое фиксируется в ,третьем регистре 3 — выражение (9) .

Предыдущее значение преобразован35 ного аргумента D ýêñïîíåíòû и логарифмическая константа 0,5 1п (1 +

+ Р„2 + 2 " ) поступают соответственно из четвертого регистра 4 и блока 14 памяти логарифмов в вычитатель 10, где формируется новое значение преобразованного аргумента

D „, экспоненты, которое фиксируется в четвертом регистре 4 .- выражение (10).

Все итерационные шаги выполняются в устройстве аналогично рассмотренному °

После Выполнения и итераций с 50 двойными шагами в регистрах зафиксированы следующие результаты: в первом регистре 1 А „+, О> во втором регистре 2 В „, = е" (Х +Yz) 1/2; в тРетьем РегистРе 3 С „+, are tg(Y/Õ); 55 в четвертом регистре 4 Dz О, Таким образом, реализованы выражения (!3) - (16).

99 6

Фор мул а из обретения

Устрой тно для выполнения преобразования координат, содержащее три регистра, три сумматора-вычитателя, два сдвигателя и блок памяти арктангенсов, причем выходы первого и второго регистров соединены с информационными входами соответственно первого и второго сдвигателей, входы первого операнда первого и второго сумматоров-вычитателей соединены с выходами соответственно первого и второго регистров, тактовый вход устройства соединен с входами синхронизации первого, второго и третьего регистров и с входом разрешения чтения блока памяти арктангенсов, вход номера итерации устройства соединен с входами сдвига первого и второго сдвигателей и с первыми адресными входами блока памяти арктангенсов, выход знакового разряда первого регистра соединен с входом кода операции третьего сумматора-вычитателя, вход первого операнда которого соединен с выходом блока памяти арктангенсов, вход второго операнда ". третьего сумматора †вычитате соединен с выходом третьего регистра, выход третьего сумматора-вычитателя .соединен с информационным входом третьего регистра, о т л и ч а ю щ ее с я тем, что„с целью расширения области применения за счет возмож.— ности преобразования в экспоненциальном масштабе, и него введены четвертый регистр, четвертый и пятый сумматоры-вычитатели, вычитатель и блок памяти логарифмов, выход которого соединен с входом вычитаемого вычитателя, вход уменьшаемого которого соединен с выходом четвертого регистра, выход вычитателя соединен с информационным входом четвертого регистра, выходы первого и второго сумматоров-вычитателей соединены с входами первого операнда соответственно четвертого и пятого сумматоров-вычитателей, выходы которых соединены с информационными входами соответственно первого и второго регистров, выход первого сдвигателя соединен с входами второго операнда первого и пятого сумматоров-вычитателей, выход второго сдвигателя соединен.с входами второго операнда второго и — четв ерт ого суммат оров1462299

Составитель АЗорин

Редактор Ю. Середа Техред A. Кравчук Корректор С.Черни

Заказ 713/47 Тираж 667 Подписное

ВНЦИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 вычитателей., тактовый вход устройства соединен с входом синхронизации четвертого регистра и входом разрешения чтения блока памяти логарифомовв, вход номера итерации устройства соединен с первым адресным входом блока памяти логарифмов, выход знакового разряда первого регистра соединен с входами кода операции четвертого и пятого сумматоров"вычитателей выход знакового разряда четвертого регистра соединен с входами кода операции первого и второго сумматоров-вычитателей и вторыми адресными входами блока памяти арктангенсов и блока памяти логарифмов,