Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в спе1щализированных вычислителях . Целью изобретения является расширение класса решаемых задач за счет возможности вычисления среднего геометрического. Устройство содержит с5Т4матор 1 , блок 2 сдвига, экспоненциальный преобразователь 3, логарифмические преобразователи 4, 5,0..,п соответственно с первого по п-й. 1 ило

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1462302

А1 д11 4 G 06 F 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

Рхл mg> mx

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (2! ) 4213646/24-24 (22) 19.03.87 (46) 28.02.89. Бюл. У 8 (71) Ереванский политехнический институт им.К.Маркса (72) К.Ж.Цатрян и Г.Ж.Цатурян (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 1171788, кл. С 06 F 7/552, 1984.

Авторское свидетельство СССР

К 1146660, кл. О 06 F 7 /552, 1984. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях. Целью изобретения является расширение класса решаемых задач за счет воэможности вычисления среднего геометрического. Устройство содержит сумматор 1, блок 2 сдвига, экспоненциальный преобразователь 3, логарифмические преобразователи 4, 5,...,n соответственно с первого по п-й. 1 ил.!

462302

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Целью изобретения является расширение класса решаемых задач за счет возможности вычисления среднего геометрического п чисел.

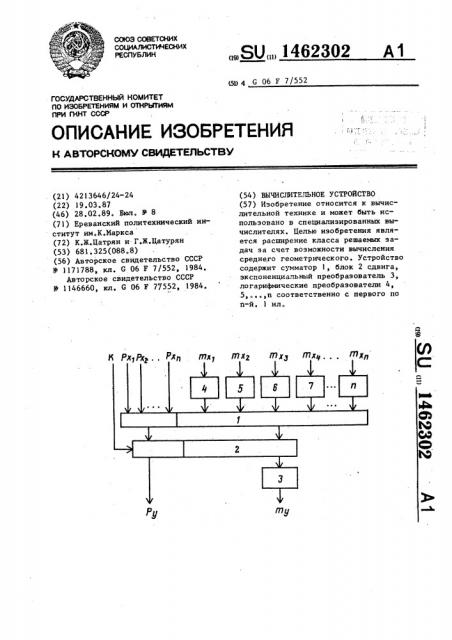

На чертеже представ. пена функциональная схема предлагаемого устройства.

Устройство содержит сумматор 1, блок 2 сдвига, экспоненциальный преобразователь 3, логарифмические преобразователи 4 и 5,...,n соответст: венно с первого по п-й.

Устройство функционирует следующим образом.

Вычисление среднего геометричес- 2О кого значения чисел, представленных

: в форме с плавающей запятой, с использованием операций логарифмирования и экспоненцирования реализуется по следующему алгоритму: 25 (Р <-, + Р )

У = х «

Р (Р + +Р +с) 30 х«

1

=ехр ) (log mx<

+ ° ° -. 10g mõ -с) э

35 (-, . ) о ° 9mx << ! с1

9 шх< >

a=2,2,3,...; с = Е at(logjam +...+1од ш„„)

По значениям мантисс mÄ,,...,m из соответствующих логарифмических преобразователей выбираются значения

1

Р „ операндов поступают на входы старших разрядов сумматора 1. 7аким образом, в сумматоре 1 вычисляются: в младших разрядах -A=log ш„,+...., log mx„- С, в старших разрядах — В =Р„, +...+

+Р +С где С - сумма переносов из младших разрядов.

Результат, полученный в сумматоре

1, подается на информационные входы блока 2 сдвига„ а на его управляющий вход поступает значение К с входа устройства. Блок 2 сдвига осуществляет сдвиг полученного результата вправо на К разрядов, т.е. на выходах старших разрядов блока 2 получается

-К значение P =2 ° В, а на выходах к младших разрядов - значение D 2 А.

Значение P с выходов старших разрядов блока 2 сдвига подается на выходы порядка результата устройства. По значению D младших разрядов блока 2 сдвига из экспоненциального преобразователя 3 выбирается значение m<

=ехр D и подается на выходы мантиссы а результата устройства.

Формула изобретения

Вычислительное устройство, содержащее первый и второй логарифмические преобразователи, экспоненциальный преобразователь, блок сдвига и сумматор, причем входы младших разрядов первого и второго слагаемых сумматора соединены с выходами соответственно первого и второго логарифмических преобразователей, о т л и— ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач за счет воэможности вычисления среднего геометрического и чисел, в него до" полнительно введены логарифмические преобразователи с третьего по п-й выходы которых соединены младшими разрядами входов слагаемых сумматора соответственно с третьего по п-й, выходы сумматора соединены с информационными входами блока сдвига, выходы младших разрядов которого соединены с входами аргумента, экспоненциального преобразователя, выходы которого соединены с выходами мантиссы результата устройства, выход порядка которого соединен с выходами старших разрядов блока сдвига, управляющий вход которого соединен с входом показателя степени устройства, входы порядков с первого по и-й устройства соединены со старшими разрядами входов слагаемых сумматора соответственно с первого по п-й

Р входы мантисс .с первого по п-й устройства соединены с входами аргументов логарифмических преобразователей соответственно с первого по п-й.