Функциональный логарифмический преобразователь

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКих

СОЦИЛЛИСТИЧЕСКИХ

РЕСПУБЛИК (19>Я0 (1и 1 4

Ai (59 4 С 06 Г 7/556

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A ВТОРСНОМЪ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ по изоБ Бтениям и отнеытиям пРи Гкнт сссР (?1) 4297042/24-24 (22) 26.08,87 (46) 28.02.89. Бюл. У 8 (72) 10.Â.Õozëoâ, А.М.Литвин,В.Д.Циделко, С.Г.Богославский и А.В..Крюков (53) 681.325(088.8) (56) Авторское свидетельство СССР

11 881741, кл. G 06 Г ?/556, 1979.

Авторское свидетельство СССР

У 1397905, кл. G 06 F 7/556, 1985, (положительное решение по заявке

Р 4146759/24-24 от 19.05.87). (54 ) ФУНКЦИОНАЛЬНЫЙ ЛОГАРИФМИЧЕСКИЙ

ПРЕОБРАЗОВАТЕЛЬ . (57) Изобретение относится к цифровой вычислительной технике и может

Изобретение относится к цифровой вычислительной технике и может быть использовано для преобразования иразрядных двоичных чисел при построе-, нии специализированных вычислительных цифровых устройств для обработки сигналов в микропроцессорных системах повышенного быстродействия.

Целью изобрете ия является повышение точности.

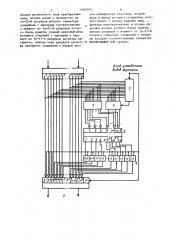

На чертеже представлена блок-схема предлагаемого преобразователя.

Преобразователь содержит регистр .

1 аргумента, сумматор 2, блок 3 памяти, группу элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ 4, сумматор 5, блок 6 памяти, де" шифратор 7 участков. быть использовано при построении специализированных вычислительных систем, информационно-измерительных систем и устройств для обработки сигналов. Целью изобретения является повышение точности. В состав функционального логарифмического преобразователя входят регистр аргумента, два сумматора, два блока памяти, группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и дешифратор участков. В данном функциональном преобразователе повышение точности достиг=.ется sa счет использования общего поля значений основной корректирующеч функции и разделения на два участка поля дополнительной корректирующей функции. 1 ил.

Работа преобразователя основана на кусочно-линейной аппроксимации х, функций y=log (1+х), у=2, где х с, (0,1) с последующей коррекцией разности (в дальнейшем функцией коррекции) между исходными функциями и их линейными приближениями.

Пусть функции у (х) и ср (z) представляют собоч разности между исходными функциями логарифма и антило,гарифма соответственно и их линейными приближениями. ср,(x)=log (1+z)-z; (1) р (z)=1+z-2", (2)

Анализ показывает, что/щ (z) / (2 и /ср (х)/„„„,(2

1462303

Сф (Х) р Х»" (Х у 1 (р,(z), х6 (О, х ) 25

З0:ционным входом. регистра аргумента, у -=

40

55 которого соединены с первыми входами соответствующих разрядов второго сумматора,, вторые входы с первого по третий разрядов которого соединены с

Функция разности второго порядка имеет ви д

q,(х)-(у (х), х 6 О,х ); (3) анализ которой показывает, что (q, (х) / „,с г- .

Функция разности второго порядка

jap (х), х х (О, х, }; (» )

СР (х) : (() (x), х Г (х», 1).

Очевидно, что /ц (х)/„„ „,с.2

Таким образом

cg (х)+(д(х), х б (О,х ) (5) yз(х) + (4),, ХЕ (хо, l ) Запишем результирующие уравнения преобразования для функции y=log (l+

+ z) z +g (х)+ (g (х),ХЕ (О,х(„) У)

z+Q)(z) х Е (х, 1), (7) для функции у =2"

1+х - Cp (х), х б (О,х ) (8) 1+х (Ц (z)+cf (х) )»х» f z ), 1 ) °

Численное значение х, можно найти„ приравняв между собой правые части уравнений (1) и (2): log (1+z)-х

Я и

=1+х-, 2 . Решая уравнение относительно х, находим, что х =0,485836...„, или для двоичной системы счисления х = 0,011111000101. ° .

Рассмотрим работу преобразователя в режиме логарифмирования. На вход задания вида функции преобразователя поступает сигнал низкого уровня. Дешифратор 7 участков формирует сигнал высокого уровня, если х б(О,х ) и сигнал низкого уровня, если хб (х„,1)

s соответствии с которым на выходах второго блока памяти 6 формируется значение функции q (х), если

Х6 (0,х,). Группа элементов ИСКЛЮЧАЮЩЕЕ HJlH (пропускает выходной код второго сумматора 5 .беэ изменений„

На выходе преобразователя получаем функцию согласно уравнению (7).

В режиме антилогарифмирования на

}вход задания вида функции преобразователя поступает сигнал высокого

20 уровня, Дешифратор 7 участков вырабатывает сигнал низкого уровня, если

x E (О,x,) и сигнал высокого уровня, если х е х,1), в соответствии с KQ торым на выходах второго блока 6 памяти формируется значение q„(z), если х (х,,l). Группа элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 4 осуществляет инверсию суммарной корректирующей функции и совместно с сигналом вида функции преобразователя, подключенным к вхо,ду переноса первого сумматора 2,осуществляет выполнение операции вычитания х- с1),(х) или х"(Cp>(x)+Cp+(x)), заменяя ее операцией сложения в дополнительном коде. В результате на выходе преобразователя формируется точное значение функции у, согласно функции (8).

Формула изобретения

Функциональный логарифмический преобразователь, содержащий регистр аргумента, первый сумматор, первый блок памяти и группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем вход аргумента преобразователя соединен с информавыходы разрядов с первого по и-й которого (и"разрядность аргумента) соединены с первыми входами соответственно с первого по п-й разрядов первого сумматора, вторые входы разрядов с первого по третий которого соединены с входом задания вида функции преобразователя, первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы и входом переполнения первого сумматора, выход которого соединен с выходом преобразователя, выходы элементов ИСКПЮЧАЮЩЕЕ ИЛИ с первого по (и-3)-й соединены с вторйми входами

» соответственно с четвертоro по п-й разрядов первого сумматора, о т л ич ающий с я тем, что, с целью увеличения точности; в него введены второй блок памяти, дешифратор участков и второй сумматор, причем выходы с первого по (n-2)-й разрядов регистра аргумента соединены с адресным входом первого блока памяти, выходы с первого по (n-3)-й разрядов

14б2303 входом логического нуля преобразователя, вторые входы с четвертого по (и-3) "й разрядов второго сумматора соединены с выходами соответственно с первого по (n-6)-й разрядов второго блока памяти, первый адресный вход которого соединен с выходами с первого по (п-4)-й разрядов регистра аргумента, выходы всех разрядов регист- 10 ра аргумента соединены с первым входом дешифратора участков, второй . вход и выход которого соединены соот-ветственно с входом задания вида функции преобразователя и вторым адресным входом второго блока памяти, выходы разрядов с первого по (и-3)-й второго сумматора соединены с вторыми входами соответствующих элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ группы.