S-й сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть Hct пользовано для построения быстродействующих арифметических устройств, работающих как в двоичной, так и в позиционно-остаточной системах счисления . Целью изобретения является ; уменьшение объема оборудования. Цель достигается тем, что сумматор, содержащий первую группу коммутаторов 1, блок 4 формирования переноса, блок 5 формирования коррекции, труп-; пу матриц 9 элементов И, группу блоков 10 элементов ИЛИ, группу шифра- : торов 11, группу регистров 12, пер- I вую и вторую группы дешифраторов 18,: 19, содержит элемент ИЛИ 14, элемент 15 задержки, вторую группу коммутаторов 16 и группу блоков 17 хранения констант с соответствующий связями., 2 ил. 1

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСГ1УБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ б

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4272587/24-24 (22) 01.07.87 (46) 28,02.89. Бюл. У 8 (72) В.Г.Евстигнеев, А.И.Кощарновский.и Т.Б.Ермакова (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 1290314, кл. G .06 F 7/72, 1985, Авторское свидетельство СССР

В 1285468, кл, G 06 F 7/72, 1985. (54) S-Й СУММАТОР (57) Изобретение относится к вычислительной технике и может быть ис". пользовано для построения быстродействующих арифметических устройств, ;работающих как в двоичной, так и в

ÄÄSUÄÄ 1462306 А1 (51) 4 G 06 F 7/72 G 06 F 7/50 позиционно-остаточной системах счисления. Целью изобретения является уменьшение объема оборудования, Цель. достигается тем, что сумматор, содержащий первую группу коммутаторов

1, блок 4 формирования переноса, 1 блок 5 формирования коррекции, груп-,: пу матриц 9 элементов И, группу блоков 10 элементов ИЛИ, группу шифраторов 11, группу регистров 12, пер-, вую и вторую группы дешифраторов 18, 19, содержит элемент ИЛИ 14, элемент

15 задержки, вторую группу коммутато. ров 16 н группу блоков 17 хранения констант с соответствующими связями., 2 ил. !

Ф

1462306

"1 а, +Ь1+ ;,,К, =0, а; + b;+f;, -S, 1, если а +Ь. +

Ь; и

-S, (3) передана с а Я

l ч, Š— я, О, если

1, если

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств, работающих как в двоичной так и в позиционно-остаточной системах счисления.

Целью изобретения является уменьшение объема оборудования.

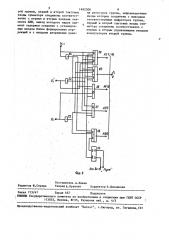

На фиг.l представлена схема предлагаемого S-сумматора; на фиг.2— схема блока формирования коррекции.

Сумматор (фиг.1) содержит первую группу коммутаторов 1, первый и вто-рой тактовые входы 2 и 3 сумматора, ! .блок 4 формирования переноса, блок

:5 формирования коррекции, выход 6 пе. реноса сумматора, вход 7 запуска

: сумматора, вход 8 переноса сумматора, группу матриц элементов И 9, группу 20 ,: блоков элементов ИЛИ 10, группу шиф раторов 11, группу регистров 12„ выаход 13 суммы сумматора, элемент ИЛИ

:14, элемент 15 задержки, вторую

При сложении операндов а„

f;, образуются величины: ,7 =а +Ь ° Я +1р C =S, E +l одна из которых должна быть иа выход S-сумматора.

В блоке 5 по анализу величин v ! и входного переноса f;, формируется выходной перенос f, и адрес бло- 45 ка 17 хранения констант.

В каждом из блоков 17 хранения констант группы размещены константы емца а = 10,1 — й, I — 51, причем, константы — S и 1 — S хранятся в до50 полнительном коде.

Блок 4 формирования переноса мо.жет быть реализован согласно прототипу в виде блока постоянной памяти или комбинационным.

Каждый из группы шифраторов ll

Формирует на своих выходах двоичный код величины, поступивший на вход, по соответствующим основаниям. группу коммутаторов !6, группу блоков 17 хранения констант, первую группу дешифраторов 18, вторую группу дешифраторов 19, группу входов 20 первого слагаемого сумматора, группу входов 21 второго слагаемого сумматора.

Блок 5 формирования коррекции 1 (фиг.2) содержит с первого по третий элементы НЕ 22-24, триггер 25, первый элемент И-ИЛИ-НЕ 26, первый и второй элементы И-НЕ 27 и 28, второй и третий элементы И-ИЛИ-НЕ 29 и

30.

В основу работы S-сумматора положено представление операндов а, и Ь; в коде системы остаточных классов (СОК) по совокупности из п оснований таких, что 2 S g, Я = .П P °

) =-1 а,,=(, „...,.С„), Ь,=(P„...,Р„) (1) Операция сложения выполняется по правилу работы полного сумматора если a;+b;+f, S (2) В блоке 4 формирования переноса

I формируется перенос V; и сигнал V, распространения переноса, согласно следующим правилам:

О, если Q Q S-l (4) если Я = 8-1, Сумматор работает в два такта.

По входу 7 триггер 25"блока 5 устанавливается в исходное (нулевое) положение.

В первом такте по входу 2 подается первый тактовый сигнал, открываю щий коммутаторы 1 и 6 первой и второй групп по первым информационным входам. Операнды а; и Ь . с входов

20 и 21 сумматора проходят через коммутаторы групп 1 и 16 через дешифраторы 18 и 19 первой и второй групп и поступают на входы матриц элементов И группы, на выходах которых образуется сумма (а„ +Ь;) по соответствующим основаниям. Бпоки 10 элементов ИЛИ группы преобразуют ре1462306

А(0) = v

А(1) = v;

А(-S)= v;

А(1-S)=v;

f;, f; °

f; ) )° (К=О) .(к=!) (к= -s) (к=1-s) I

v; (v;

Ч (5) v;

25 зулнтат суммирования с выходов матриц 9 элементов И группы в кад один из P который поступает на входы блока 4 формирования переноса и на

1 входы соответствующих шифраторов 11 группы, где по каждому основанию образуется двоичный код. Через время, определенное временем задержки срабатывания элементов блоков 1, 18, 9, 10 и 11, первый тактовый сигнал пройдя элемент ИЛИ 14 и элемент 15 задержки поступит на входы приема информации регистров )2 группы и запишет в них результат суммирования. и сигнал переноса f в следующий

S-й разряд. ; =v; v; v v Е;, v, (6) Через открытые по вторым информационным входам коммутаторы 1 и 16 групп и одна из констант с блоков

17 группы и содержимое регистров 12 группы проходят дешифраторы 18 и 19 д0 групп и поступают на входы матриц 9 группы, на выходе которых формируется результат (а;+Ь; +К). На блоках элементов ИЛИ 10 группы и шифраторах

11 группы результат суммирования преобразуется в код (1 из P ), а затем, в код СОК, который заносйтся на регистры 12 группы.

Формула изобретения 40

S-й сумматор, содержащий первую группу коммутаторов, блок формирования переноса, блок формирования коррекции, группу матриц элементов И, группу блоков элементов ИЛИ,группу шифраторов, группу регистров, первую и вторую группы дешифраторов, причем выходы дешифраторов первой и второй группп соединены соответственна с первыми и вторыми группами входов соответствующих матриц элементов И группы, выходы которых соединены с входами соответствующих блоков элементов И группы, выходы которых соединены с входами соответствующих шифраторов группы и соответствующими входами блока формирования переноса, выходы перекоса и условия

На этом заканчивается первый такт работы сумматора.

Во втором такте по входу 3 подается второй тактовый сигнал, открывающий коммутаторы 1 и 16 первой и второй групп по вторым информационным входам. К этому моменту времени блок 4 формирования переноса выдал в блок 5 сигналы v; и v, сформированные в соответствии с (4), а блок

5 на основе этих сигналов и значения сигнала К;, (О или 1) сформировал адрес (А) блоков 17 хранения констант па правилу

1 распространения переноса которого соединены соответственно с первым и вторым информационными входами блока формирования коррекции, третий информационный вход которого соединен с входом переноса сумматора, вход запуска и выход и ренаса которого соединены соатветс-.женно с входом сброса и первым выходам блока формирования коррекции, первый и второй тактовые входы сумматора соединены соответственно с первыми и вторыми управляющими входами коммутаторов первой группы, выходы регистров группы являются выходом суммы сумматора, о т— л и ч а ю шийся тем, чта, с целью уменьшения объема оборудования, он содержит элемент задержки, элемент ИЛИ, вторую группу коммутаторов и группу блоков хранения констант, причем второй выход блока формирования коррекции соединен с адресными входами блоков хранения констант группы, входы первого слагаемого группы сумматора и выходы блоков хранения констант группы подключены соответственно к первым и вторым информационным входам соответствующих коммутаторов первок группы, выходы которых соединены с входами соответствующих дешифраторов первой группы, входы второго слагаемого группы сумматора и выходы регистров группы подключены соответственно к первым и вторым информационным входам соответствующих коммутаторов второй группы, выходы которых соединены с входами соответствующих дешифраторов втоФиг. 2

Составитель A.Клюев

Редактор В.Середа Техред A.Кравчук . Корректор Э„Лончакова

Заказ 713/47 Тираж 667 Подписное ВНИИПИ. Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, -35, Раушская наб., д. 4/5 !

Производственно-издательский комбинат "Патент", r.Óærîðîä, ул. Гагарина,101

5 рой группы, первый и второй тактовые входы сумматора соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого через элемент задержки соединен с установочньи входом блока формирования коррекций и с входами разрешения прие1462306 6 ма регистров группы, информационные входы которых соединены с выходами соответствующих шифраторов группы, первый и второй тактовые входы сум5 матора соединены соответственно с первым и вторым управляющими входами коммутаторов второй группы.