Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для ввода информации в ЭВМ, Целью изобретения является расширение ; функциональных возможностей за счет определения момента изменения входной информации, Устройство содержит первый блок I сравнения, коммутатор 2, второй блок 3 сравнения, первый регистр 4, информационные входы 5 устройства, информационные выходы 6 устройства, второй 7 и третий 8 регистры, первый триггер 9, таймер 10, входы 11 настройки устройства, второй триггер 12, выход 13 готовности устройства, третий триггер 14, элемент 15 задержки, синхронизирующий выход 16 устройства, генератор 17 импульсов, элемент И 18, элемент ИЛИ 19, Указанная цель достигается за счет введения в устройство элемента И 18,второго блока 3 сравнения, третьего регистра 8, генератора 17, первого и третьего триггеров 9 и 14, таймер а 10 и эле мент а ИЛИ 19. 2 ил. о (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИ К

РЕСПУБЛИК (5р 4 G Об F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4263493/24-24 (22) 17.06,87 (46) 28.02.89. Бюл. М- 8 (71) Институт кибернетики им, В.М. Глушкова (72) И.Е,Овчарук и С,Ю.Лелестов. (53) 681, 327. 8(088„8) (56) Авторское свидетельство СССР

Р 1201842, кл, G 06 F 13/00, !983, Авторское свидетельство СССР

1242972, кл, G 06 F 13/00, 1984, Авторское свдетельство СССР

Н 1196883, кл. G 06 F 13/00, 1983. (54) УСТРОЙСТВО Д.ПЯ ВВОДА ИНФОРИАЦИИ (57) Изобретение тельной технике и может быть исцользовано для ввода информации в ЭВИ.

Целью изобретения является расширение . функциональных возможностей за

ÄÄSUÄÄ 1462330 А1 счет определения момента изменения входной информации, Устройство содержит первый блок 1. сравнения, коммутатор 2, второй блок 3 сравнения, первый регистр 4, информационные входы 5 устройства, информационные выходы 6 устройства, второй 7 и третий

8 регистры, первый триггер 9, таймер

l0 входы 1 настройки устройства, второй триггер 12, выход 13 готовности устройства, третий триггер 14, элемент 15 задержки, синхронизирующий выход 16 устройства, генератор 17 импульсов, элемент И 18, элемент ИЛИ

19. Указанная цель достигается за счет введения в устройство элемента

И 18, второго блока 3 сравнения, третьего регистра 8, генератора 17, первого и третьего триггеров 9 и 14, таймера 10 и элемента ИЛИ 19. 2 ил, 1462330

-Изобретение относится к вычислительной технике и может быть использовано дпя ввода информации в 3BNÄÄ

Целью. изобретения является расширение функциональных возможностей за

5 счет определения мощности изменения входной информации.

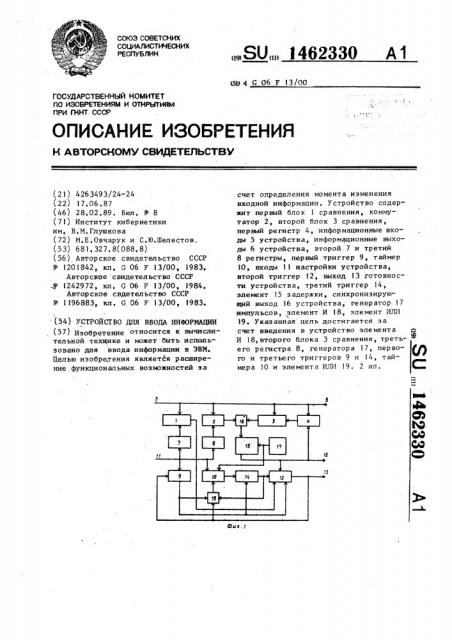

На фиг.l представлена структурная схема предлагаемого устройства; на фиг.2 " временные диаграмм, Устройство содержит первый блок i сравнения, коммутатор 2, второй блок

3 сравнения, первый регистр 4,-информационные входы 5 устройства, инфор- 15 мационные выходы 6 устройства, второй

7 и третий 8 регистры, второй триггер 9, таймер 10, программированный вход 11 устройства, первый триггер 12, выход 13 готовности устройства, тре- 20 тий триггер 14, элемент 15 задержки, синхронизирующий выход 16 устройства, генератор 17 импульсов, элемент И 18, элемент ИЛИ 19.

Блоки 1 и 3 сравнения могут быть 25 выполнены на интегральных микросхемах К555СП1, коммутатор 2 - K155TN2, триггер 12 - K155731, таймер 10КР580ВИ53 (для увеличения времени выдержки три счетчика могут быть сое" 30 динены последовательно), Элемент 15 задержки. может быть выполнен на счетчике с занесением типа

К155ИЕ7. На вход управления занесени ° ем поступает сигнал с элементов И 18> на тактовый вход счетчика "+1" пода" ются сигналы синхросерии с генератор ра 17., Сигнал на выходе 16 является сигналом переноса счетчика элемента

15, На информационном входе счетчика задается число тактов задержки в обратном коде, В исходном состоянии счетчик элемента 15 находится в режиме занесения информации под воздейст" вием сигнала с элемента И 18 с уровнем "0", При переходе сигнала с элемента И 18 в состояние "1" начинается работа счетчика в режиме счета, Генератор 17 может быть выполнен по одной из типовых схем, Вход 11 программирования устройства организован в виде шины таким образом, чтобы обеспечить занесение информации в регистры 7 и 8, триггер 9 и таймер

10, Устройство работает следукщим об55 разом,, При включении питания триггеры 9, ! 2 и 14 устанавливаются в состояние

"0" (цепи сброса не показаны), Выходной сигнал с прямого выхода триггера

9 подается на первый вход элемента

ИЛИ 19, который вырабатывает сигнал запрета счета и выдает его на управляющий вход таймера 10, Выходной сигнал "0" с прямого выхода триггера 12 поступает на выход 13 готовности устройства, сигнализируя об исходном состоянии, При наличии этого сигнала в регистры 7 и 8 и таймер 10 может быть записана информация настройки, После настройки в регистре 7 хранится код признака информации, при котором с входа 5 должен начаться ввод информации; в регистре 8 хранится код, установленные разряды которого разрешают -ввод информации с соответствующими им двоичными признаками (например, установленный нулевой разряд разрешает ввод информации с входа 5 с признаком 0000, 1-й - 0001, 15-й 1111; 1-й и 2-й 0000 и 0001 и т.д, ); таймер 10 хранит и отсчитывает временной интервал, в течение которого происходит ввод информации.

После настройки устройства триггер

9 сигналом с входа 11 устройства устанавливается в состояние "1", разблокируя тем самым триггеры 12 и 14, Элемент

ИЛИ 19 вырабатывает сигнал запрета счета, поступающий на управляющий вход таймера 10, Поступающая с инфор" мационных входов 5 устройства информация сравнивается блоком 3 сравнения с кодом, подаваемым с выходе регистра 4. В регистре 4 хранится код, поступающий с входа 5 устройства. 3апись этого кода происходит стробирующим сигналом с элемента 15. При несовпадении блок 3 вырабатывает сигнап "1", поступающий на вход элементаИ 18, Выход регистра 8 соединен с информационным входом коммутатора 2, Двоичный код информации с входа 5 поступает на адресный вход коммутатора 2, что приводит к выдаче коммутатором 2 соответствующего разряда с его входа.

Например, признак 0000 на адресном входе коммутатора 2.приводит к выдаче нулевого разряда регистра 8. Если

У этот разряд установлен в состояние

"1", через элемент И 18 происходит запуск элемента 15 и формирование с задержкой на выходе 16 устройства синхронизирующего сигнала, указывающего на смену информации на информационных

Устройство для ввода информации, содержащее первый регистр, информационные входы которого являются информационными входами устройства, второй регистр, информационные входы которого являются входом программирования устройства, а выходы соединены с вторыми входами первого блока сравнения, коммут атор, элемент з адержки, первый триггер, прямой выход которого является выходом готовности устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных воэможностей за счет определения момента изменения входной информации, в него введены элемент И, второй блок сравнения, третий регистр, второй и третий триггеры, таймер, элемент ИЛИ и генератор импульсов, выход которого соединен с тактовыми входами элемента задержки и таймера, вход установки второго триггера, информационные входы третьего регистра и таймера соединены. с входом программирования устройства, первые входы первого и второ го блоков ср авнения, входы адреса коммутатора соединены с информационными входами устройства, выход первого регистра соединен с вторым входом второго блок сравнения, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом коммутатора, информационные входы которого соединены с выходами третьего p . гистра, выход элемента И соединен с управля юшин

3 14623 выходах 6 устройства, Сигнал с выхода элемента 15 используется для стробирования ре ги стра 4, в которой з аписывается информация с входов 5 уст5 ройства, При этом коды на первом и втором входах блока 3 сравнения становятся одинаковыми, сигнал неравенства снимается, После этого выходным сигнапом "0" элемента И 18 элемент 15 10 задержки переводится в исходное состояние и тем самым формирует задний фронт импульса на выходе 16 устройства. Таким образом производится отслеживание изменений информации на вхо- 15 дах 5 устройства. Длительность задержки элемента 15 выбирается такой, чтобы исключить влияние помех, Если с выхода коммутатора 2 под воздействием информации с входов 5 устройства 20 будет выдан сигнал "0", будет блокирована выработка элементом И 18 сигнала запуска элемента 15 задержки и,таким образом, ввод информации с этим признаком не будет стробироваться. 25

Сигналом начала ввода информации, например в ЭВМ, является сигнал "1" на выходе 13, вырабатываемый триггером 12. Срабатывание этого триггера 10 происходит с приходом синхроимпульса . с элемента 15 задержки при наличии сигнала "1", вырабатываемого блоком

1 сравнения при равенстве кода, храни. мого в регистре 7, и кода, поступающего с входа 5 устройства, После этого элемент ИЛИ 19 прекращает выработку сигнала запрещения счета с управляющего входа таймера 10,и происходит ввод информации с выработкой синхро.сигнапа иа выходе 16 при наличии разрешающего сигнала на выходе 13 устройства. По истечейии заданного временного интервала выходным сигналом таймера 10 устанавли.вается в .- 45 состояние "1" триггер 14, После этого под воздействием выходного сигнала "0" с инверсного выхода триrrepа 14 по приходу синхросигнапа с выхода элемента 15 задержки триггер 12 устанавливается в состояние "О". Уровень "0" на выхо" де 13 указывает на окончание ввода, Этим же сигналом триггер 9 устанавливается в исходное состояние. Работа таймера блокируется выходным сигналом логического элемента ИЛИ 19, Для продолжения работы необходимо установить триггер 9 в состояние "1" и за разрешить тем самым работу триггеров

12 и 14, Устройство вырабатывает на выходе

13 сигнал ввода с момента поступления на вход 5 информации с заданным в регистре 7 признаком начала ввода в течение времени, отсчитываемого таймером 10, Кроме того, внутри этого временного интервала на выходе 16 вырабатывается сигнал о поступлении с входа 5 информации с одним на задан— ных в регистре 8 двоичным признаком.

Применение предлагаемого устройства позволяет исключить режим программного опроса входа 5 для определения момента изменения информации и перейти к более эффективному режиму работы ЭВМ по прерываниям сигналов по выходам 13 и 16 для выборочного ввода информации с выхода 6 устройства.

Фор мул а из обретения

1462330

СоставителЬ С, Кулиш

Техр ед Л. Олийнык

Корректор С.Шекмар

Редактор Т, Парфенова

3 аказ 7 14/48 Тираж 667 Подпи сное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, >К-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Ужгород, ул. Гагарина,IOI входом элемента задержки, выход которого соединен с тактовыми входами первого регистра, первого триггера и является синхронизирукнцим выходом устройства, прямой выход второго триггера соединен с первым входом элемент а ИЛИ, входом сброса тр етье го триггера и первым К-входом первого триггера, выход первого блока сравне" ния соединен с первым Х-входом первой ) 9 г(а) 18

14

ro триггера, вторые I- и К-входы которого соединены с инверсным выходом трет ье го три г rep а и вторым входом элемента ИЛИ > третий вход которого сое- . динен с входом сброса второго триггер а и прямым выходом пер во го три гге" ра, выход элемента ИЛИ соединен с управляющим входом таймера, выход которого соединен с входом установки третьего триггера,