Устройство для обмена информацией

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах , в многомашинных вычислительных системах, в локальных сетях обмена данными и в системах обмена данными между ЭВМ и абонентами. Целью изобретения является повышение быстродействия . Устройство состоит из М каналов , каждый из которых содержит блок элементов И-ИЛИ, блок элементов И, информационный регистр, три элемента И, элемент ИЛИ-НЕ, элемент задержки . 1 ил,

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН аэ) ш> 1 4 2 (51) 4 G 06 F !3/14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГЙНТ СССР (21) 4295117/24-24 (22) 10.08. 87 (46) 28.02. 89, Бюл. М- 8 (72) В. В, Соколов и Ю.И, Сорокин (53) 681. 325{088. 8) (56) Авторское свидетельство СССР

К 1118997, кл. G 06 F 13/14, 1983, Авторское свидетельство СССР

jj 1328822, кл, G 06 F 13/14, 1986, (54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ (57) Изобретение относится к вычисли1

Изобретение относится к вычислит ел ьной технике и может быт ь и с пол ьзовано в цифровых вычислительных машинах, в многомашинных вычислительных системах, в локальных сетях обмена данными и в системах обмена данными между ЭВМ и абонентами.

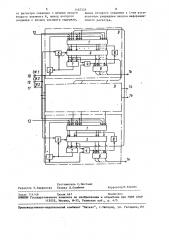

Целью изобретения является повышение быстродействия устройства, На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит блок,1 элементов И-ИЛИ, информационный регистр 2, элементы И 3-5, блок 6 элементов И, элемент ИЛИ-НЕ 7, элемент 8 з адержки в каждом из M каналов 9, входы 10-13 и выходы 14.

Сущность работы утройства состоит в том, что каждая К-я ЭВМ может записывать информацию в любой свободный р е ги стр . 3 апи с анн ая ин фор маци я не пр ерывно циркулирует в регистрах 2, причем при наличии "1" в К-м разряде ретельной технике и может быть использовано в цифровых вычислительных машинах, в многомашинных вычислительных системах, в локальных сетях обмена данными и в системах обмена данными между ЭВМ и абонентами, Целью изобретения является повышение быстродействия, Устройство состоит из М каналов, каждый из которых содержит блок элементов И-NJIH блок элементов

И, информационный регистр, три элемента И, элемент ИЛИ-HE элемент задержки. 1 ил. гистра 2 осуществляется считывание информации К-й ЭВМ, Функционирование устройства осу ществляется в результате поступления циклической последовательности из трех синхроимпульсов, осуществляюцих: р

СИ 1 — запись и считывание информации; СИ 2 — перепись информации из

i-го регистра в (i+1)-й, а из M-го регистра — в первый; СИ 3 — стирание информации в тех регистрах, где все

М адресных разрядов установлены в: СЛ состояние "0".

Поскольку запись информации осуществляется только при условии нахождения всех M адресных разрядов в состоянии "О", то принципиально невозможно считывание и запись информации в любом из кайалов устройства одновременно.

Устройство работает следующим образом, з

146

В исходном состоянии регистры 2 всех каналов установлены в состояние

"О", На выходах элементов ИЛИ-HE 7 сформированы разрешающие потенциалы, При подаче тактового импульса на вход

1О он через открытые элементы И 3 подается на вторые тактовые входы блоков элементов И-НЕ 1, осуществляя запнсь информации от каждой ЭВМ и соответствующие регистры 2. Поступающие сб входа 11 устройства такто" вЦе импульсы подаются на первые тактовые входы блоков элементов

И ИЛИ 1, осуществляя перепись и формации из i- ro ре ги стр а в (i+1)-й, а из M-ro регистра - в пЕрвый, Поступающие далее с входа 10 . пр следующие тактовые импульсы, пройдя элементы И 3 и 4, размещающие или э апрещающие з апись и. съем информации, о суще ст вляют (или не осуществляют) запись информации из К-й ЭВМ в любой свободный рагистр или считывание, если в К-м регистре записан код "1" и номер регнстра совпадает с номером 3ВМ, причем при считывании информации в адресной части соответствующего регистра 2 осуществляется обнуление разряда, соответствующего номеру адресата, путем задержки импульса с выхода элемента И 4 элементом 8 задержки, Как и в устройстве-прототипе перепись информации из регистра в регистр о существляется парафазным колом, При записи информации обычным кодом исПользуют ся тактовые импульсы, поступающие с входа 12, которые подаются

Иа первые входы элементов И 5, на вторые входы которых подаются разрешающие потенциалы с выходов соответCòâóþùèõ элементов ИЛИ-НЕ 7, если информация передана всем адресатам.

М актовые и мпул ь сы, пройдя элементы И подаются на входы установки в нулевое состояние разрядов соответствующего регистра, При записи информации парафазным кодом, как в устройстВе-прототипе, тактовые импульсы, поступающие со входа 12, не используются, а элемент И 5 оказывается ненудным, Формул а из обр ет ения

Устройство для обмена информацией, содержащее M каналов, причем первые информационные вход и выход i-ro ка2335 а нала (i= !, М) являются входом и выходом устройства для подключения соответсвенно к информационным выходу и входу i-й ЭВМ, первый и второй тактовые входы i-го канала являются соответственно первым и вторым тактовыми входами устройства, второй информационный вход i-го канала сое нен с вторым информационным выходом (i-1)-го канала, второй информационный вход первого канапа соединен с вторым информационным выходом M-го канала, при этом каждый канал содержит блок элементов И-HJIH блок элементов И, информационный регистр, два элемента И, причем первый и второй информационные входы блока элементов И-ИЛИ являются соответственно первым и вторым информационными входами канала, информационный выхсд блока элементов И является первым информационным выходом канала, адресные и информационные разрядные выхо25 ды информационного регистра образуют второй информационный выход канала, первый вход первого элемента И соединен с первым входом второго элемента

И и является первым тактовым входом канала, первый тактовый вход блока элементов И-ИЛИ является вторым тактовым входом канала, при этом выход второго элемента И соединен с тактовым входом блока элементов И, информационные входы которых соединены

35 с информационными разрядными выходами информационного регистра, информационные входы которого соединены с информационными выходами блока элементов И-ЙЛИ, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в каждый канал введены третий элемент И, элемент

ИЛИ-НЕ и элемент задержки, причем третий тактовый вход i-ro канала является третьим тактовым входом устройства, при этом в каждом канале первый вход третьего элемента И является третьим тактовым входом канала, выход третьего элемента И соединен с установочным входом информационного регистра, адресные разрядные .выходы которого соединены с входами элемента ИЛИ-НЕ, выход которого соединен с вторым вхо55 дом третьего элемента И и с вторым входом первого элемента И, выход которого соединен с вторым тактовым входом блока элементов И-ИГИ, i-й адресный разрядный выход информационно10

11

Составитель С,Пестмал

Редактор Т, Парфенова Техред Л. Олийнык

Корректор Н, Король

Заказ 714/48 Т,ираж 667 Подпи сное

ВНИИПИ Государственного комитета по иэобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4!5

Проиэводственно"иэдательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101

5 . 1462335 6 го регистра соединен с вторым входом выход которого соединен с i-ым уставторого элемента И» выход которого новочным раэрядным входом информацисоединен с входом элемента эадержки> онного регистра.