Процессор для реализации операций над элементами нечетких множеств

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для использования в информационносоветующих системах оперативного управления технологическими процессами , а также нечетких логических регуляторах, реализующих нечеткие алгоритмы управления и -работающих в реальном масштабе времени. Цель изобретения заключается в повьппении производительности процесса за счет - уменьшения выборки операндов. Поставленная цель достигается тем, что в процессор, содержащий регистр 2, схему 4 сравнения, первый 3 и второй 5 коммутаторы, группу 7 элементов И, блок 6 управляющей памяти, счетчик 8. и элемент И 10, введено ассоциативное запоминающее устройство 1, что позволило уменьшить время выборки обрабатываемых операндов. 7 ил. 0

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5И 4 G 06 F 15/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4266290/24-24 (22) 22. 06. 87 (46) 28. 02.89. Бюл. у 8 (7 1) Харьковский институтрадиоэлектроники им.акад.M.Ê.ßíãåëÿ (72) И.И.Завизиступ и С.И.Колодяжный (53) 681.325(088.8)

l (56) Авторское свидетельство СССР

Р 1280381, кл. С 06 Р 15/20, 1985.

Авторское свидетельство СССР

Р 1256010, кл. G 06 P 7/00, 1985. (54) ПРОЦЕССОР ДЛЯ РЕАЛИЗАЦИИ ОПЕРАЦИЙ НАД ЭЛЕМЕНТАМИ НЕЧЕТКИХ МНОЖЕСТВ (57) Изобретение относится к вычислительной технике и предназначено для использования в информационносоветующих системах оперативного

„„SU„„1462348 A i управления технологическими процессами, а также нечетких логических регуляторах, реализующих нечеткие алгоритмы управления и .работающих в реальном масштабе времени. Цель изобретения заключается в повышении производительности процесса за счетуменьшения выборки операндов. Поставленная цель достигается тем, что в процессор, содержащий регистр 2, схему 4 сравнения, первый 3 и второй

5 коммутаторы, группу 7 элементов И, блок 6 управляющей памяти, счетчик 8 и элемент И 10, введено ассоциатив- . ное запоминающее устройство 1, что позволило уменьшить время выборки обрабатываемых операндов. 7 ил.

1462348

Изобретение относится к вычислительной технике и предназначено для использования в информационно-совету1ощих системах оперативного управления 5

Технологическими процессами, а также

s нечетких логических регуляторах, реализующих нечеткие алгоритмы управления и работающих в реальном масштабе времени. 10

Целью изобретения является повьг шение производительности процессора эа счет уменьшения времени выборки операндов.

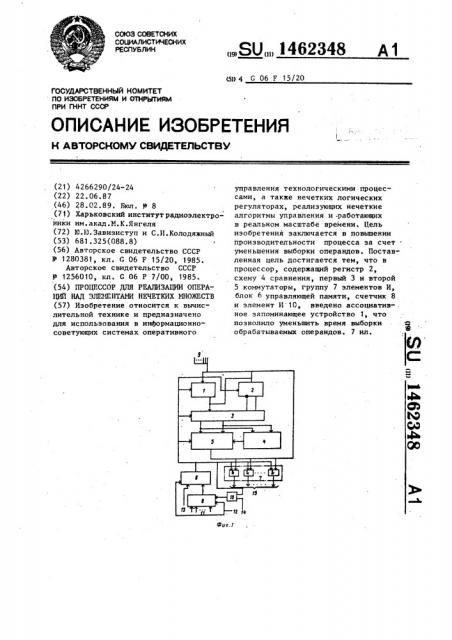

На фиг. 1 представлена структурная 15 .схема предлагаемого процессора; на фиг. 2 — структура признака слова ин::формации, хранимого в ассоциативном ,:запоминающем устройстве; на фиг. 3—

:структурная схема ассоциативного за- 20 ,: поминающего устройства (АЗУ); на фйг. 4 — функциональная схема запоминающей ячейки АЗУ; на фиг. 5—

;формат команды процессора для па раллельной обработки информации", на фиг. 6 — формат команды процессора для последовательной обработки инфор0 .:мацки; на фиг. 7 — формат команды

-м . ю процессора для одноместной операции.

Процессор (фиг. 1) содержит ассо30 циативное запоминающее устройство 1, регистр 2, первый коммутатор 3, схему

4 сравнения, второй коммутатор 5 блок 6 управляющей памяти (УП), группу 7 элементов И, .счетчик 8, вход 9 35 исходных значений, элемент И 10, вход И 10, вход 11 адреса микрокоманды, вход .12 задания режима работы, вход 13 загрузки программ, тактовый вход 14, выход 15 результата.

Признак слова информации (фиг. 2) содержит признак 16 лингвистической переменной и признак 17 терма.

Ассоциативное запоминающее устройство (фиг.3) содержит вход 18 признака 45 лингви стичес кой переменной, вход 19 признака терма, информационный вход

20, выход 21 и 1 x k запоминающих ячеек, где 1 — число, равное сумме терм-множеств всех переменных, а 50

k — число элементов функции принадлежности терма.

Замоминающая ячейка (фиг. 4) содержит вход 22 признака слова, вход

23 записи признака, схему 24 сравнения, триггер 25 совпадения, вход 26 сброса триггера совпадения, вход 27 управления выходом, группу элементов

ИСКЛЮЧА10НЕГ ИЛИ 28, . выход 29, группу

30 триггеров, хранящих признак, группу 31 триггеров, хранящих инфор-. мацию, вход 32 записи-считывания информации, информационный вход 33.

Формат команды для параллельной обработки информации (фиг. 5) содержит поле 34 признака вида обработки, поле 35 кода операции, поле 36 признака первого операнда, поле 37 признака второго операнда, поле 38 признака результата и поле 39 длины обрабатываемых массивов.

Формат команды для последовательной обработки информации (фиг. 6) содержит поле 40 признака последовательной обработки, поле 41 кода операции, поле 42 признака первого операнда, поле 43 признака второго операнда и поле 44 признака результата.

Формат команды для одноместной операции (фиг. 7) содержит поле 45 признака одноместной операции, поле

46 кода операции, поле 47 признака операнда и поле 48 признака адреса регистра.

Процессор работает следующим образом.

Исходные данные,с которыми оперирует процессор с входа 9 поступают в АЗУ. Данные — это значения функций принадлежностей нечетных мно. — ... жеств, принимающие значения из интервала 0,1. Процессор реализует следующие операции над значениями а и b нечетных множеств: дополнение 1 а

1 — а, пересечение (минимум) с

= мин (a, Ъ), объединение (максимум) с = макс (а, Ь), импликация а -Ъ

= макс (1-а, b), эквивалентность а Ъ = мин (макс(1-а, Ь), макс (1-Ъ, а), операцию транзитной передачи данных через процессор, операцию

"Ассоциативная запись", операцию

"Ассоциативное чтение" (с — результат выполнения двухместных операций).

В нечетких алгоритмах управления иснользуются .лингвистические переменные (ЛП), например, "Температура", "Скорость вращения" и т.д. ЛП ".Температура" может принимать значения типа "Иалая", "Средняя", "Большая" и т.д. Каждое значение (терм) пред-. ставляется в виде нечеткого множества, например "Температура" "Большая" = 0(50 С + 0,1/60 С + 0,5/80 С +

+ 1/100 С, где О, 01„ 05, 1 — элемен1462348 ты функции принадлежности нечеткого множества; 50; 60; 80; 100 С вЂ” базо. вое множество нечеткого множества, знак + обозначает операцию объединения. Совокупность значений ЛП

5 образует терм-множество значений ЛП.

При использовании АЗУ поиск необходимого нечеткого множества, соот-. .. ветствующего какому-либо значению ЛП, 10 осуществляется в соответствии со структурой признака, показанной на фиг. 2 °

Например, необходимо обработать

ЛП "Температура" со значением "Большая". Определяем признак ЛП "Температура" и признак терма "Большая" в виде двоичных кодов. Длина признака

ЛП определяется числом участвующих при решении задачи ЛП, а длина признака терма — множеством термов данной ЛП. Тогда, при одном обращении к памяти все ячейки АЗУ, хранящие значения функции принадлежности нечеткого множества "Температура" = 25

"Большая", будут подготовлены для чтения.

Запоминающая ячейка АЗУ работает следующим образом.

Код признака с выхода управля-, З0 ющей памяти поступает на схему сравнения и на триггеры группы 30. В . зависимости от сигнала на входе 23, ° вырабатываемого управляющей памятью, происходит либо запись нового признака, 35 либо сравнениепоступившего признака и признака слова, ранее хранимого

:в запоминающей ячейке, в схеме 24 сравнения. При их совпадении триггер

25 устранавливается в "единичное 40 состояние". Наличие уровня "1" на выходе триггера 25 совпадения разрешает работу информационной части запоминающей ячейки, т.е. когда выход триггера 25 находится в сос- 45 тоянии "1", возможны запись или считывание информации с триггеров группы 31, причем запись информации в триггеры группы 31 или считывание будут зависеть от сигнала поступив- 50 шего с выхода управляющей памяти, на входе 32. Записываемая информация поступает на входы 33 запоминающей ячейки. После записи в триггеры группы 31 она может быть передана на выходную шину 29 через группу элементов ИСКЛПЧАЮЩЕЕ ИЛИ 28 в прямом или инверсном коде, в зависимости от сигнала, поступившего с выхода управляющей памяти на вход 27 управления выходом.

Если при подаче на вход АЗУ признака сразу в нескольких ячейках установится в единицу триггер совпадения, то первой будет считана ячейка с меньшим номером столбца АЗУ, что определяется аппаратурной реализацией

АЗУ. После считывания информации с данной ячейки триггер совпадения сбрасывается сигналом с выхода управляющей памяти, поступившим на вход 26 триггера, и ячейка с номером столбца АЗУ, ближайшим к считанной, будет готова для считывания информации.

На фиг. 5 — 7 представлены форматы команд процессора.

Формат команды процессора для одноместной операции (фиг. 7) используется в операциях "Ассоциативная запись" и

"Ассоциативное чтение" для обмена информацией между АЗУ процессора и оперативным запоминающим устройством

ЭВМ. Содержимое поля 47 интерпретируется в зависимости от кода операции или как признак результата, или как адрес оперативного запоминающего устройства. Обе команды инициируют передачу массивов информации (т.е. используются для записи в АЗУ и считывания на АЗУ элементов функции принадлежности терма ЛП) . Число элемейтов массива указывается в коде операииид

Рассмотрим работу процессора на примере выполнения им команды после.-, довательной обработки информации. При поступлении сигнала "Начальный сброс" на вход 12 процессор сбрасывает счетчик 8 и регистр 2 в нулевое состояние. При поступлении на вход

12 сигнала "Пуск" на вход 13 УП поступает код операции, блок 6 УП выдает сигнал на элемент И 10, и тактовые сигналы с генератора импульсов по входу 14 через элемент

И 10 поступают на счетчик 8, и происходит выдача управляющей памятью первой микрокоманды. После выполнения команды УП закрывает элемент И 10, который блокирует прохождение тактовых сигналов на счетчик 8. Для изменения последовательности выполнения микропрограмм необходимо загрузить в счетчик по входу 11 адреса микрокоманды новый адрес микрооперации.

После завершения выполнения команды результат может быть выдан через

5 14623 группу 7 элементов И на выход процессора 15 или записан в АЗУ 1 или регистр 2.

Рассмотрим выполнение процессором команды последовательной обработки— мин (1а, Ь).

Микропрограмма этой команды имеет вид: подача на АЗУ признака второго операнда (b); считывание второго операнда в регистр подача на АЗУ признака первого операнда (а); считывание с АЗУ инверсного значения пер вого операнда (la) и считывание с, регистра второго операнда (Ь); пере: дача через коммутатор 3 в схему4 сравнения. операндов .1 а иЬ;передача через коммутатор 5, в зависимости от сигнала со схемы сравнения, 1-,ro или 2-го операнда в АЗУ или выдача его на выход процессора 15; запись результата операции по признаку в АЗУ или запись в регистр. На этом выполнение команды заканчивается °

Формула изобретения

Процессор для реализации операций над элементами нечетких множеств, содержащий регистр, схему сравнения, первый и второй коммутаторы, группу элементов И, блок управляющей памяти, счетчик и элемент И, причем первый вход элемента И подключен к тактовому входу процессора, выход элемента И соединен с счетным входом счетчика, выход которого. подключен к адресному входу блока управляющей памяти, вход, записи счетчика соединен с входом записи блока управляющей памяти и входом задания режима работы процессора, информационный вход блока управляющей памяти подключен к входу загрузки программ процессора, информационный вход счетчика соединен с 45 входом адреса микрокоманды процессора, прямой выход реГистра подключен к первому информационному входу первого коммутатора, второй информационный вход которого соединен с инверсным,выхолом регистра, первый информационный выход первого коммута-, тора подключен к первому информаци-. онному входу второго коммутатора и первому входу схемы сравнения, вто48

6 рой вход которой соединен с вторым информационным выходом первого коммутатора н вторым информационным входом второго коммутатора, информационный выход второго коммутатора подключен к информационному входу региотра, второй вход элемента И соединен с первыми входами элементов И группы и выходом признака конца. операции блока управляющей памяти, вторые входы элементов И группы подключены к соответствующим разрядам информационного выхода второго коммутатора, выходы элементов И группы образуют выход результата процессора, первый управляющий вход второго коммутатораподключен к выходу кода операции блока управляющей памяти, второй управляющий вход второго коммутатора соединен с выходом схемы сравнения, управляющий вход первого коммутатора подключен к выходу признака первого операнда и выходу признака второго операнда блока управляющей памяти, вход записи. регистра соединен с выходом признака второго операнда блока управляющей памяти, о т л и ч а юшийся тем, что, с целью повышения производительности за счет уменьшения времени выборки операндов, в него введено ассоциативное запоми.-. нающее устройство, причем информационный вход ассоциативного запоминающего устройства подключен к информационному выходу второго коммутатора и входу исходных значений процессора, выход ассоциативного запоминающего устройства соединен с третьим информационным входом первого коммутатора и информационным входом регистра, вход признака ассоциативного запоминающего устройства подключен к выходу признака первого операнда и выходу признака результата блока управляющей памяти, выход признака результата блока управляющей памяти соединен с входом записи регистра, вход записи-считывания информации, вход управления выходом, входь1 записи признака и входы сброса триггеров совпадения ассоциативного запоминающего устройства подключены к соответствующим выходам задания режима блока управляющей памяти.

1462348

-1462348

00 t(gg

Я О И Z7 38 ЮУ

Фиг. $

Фиг, Е

Фие. 7

Составитель В. Есипов

Редактор Т. Парфенова Техред Л.Олийнык Корректор С. Черни

Заказ 715/49 Тираж 667 Подписное

BHHHIIH Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35 ° Раушская наб., д. 4/5

П анно-издательский комбинат "Патент", г. ужгород, ул. Гагарина,301

Производственно-и

Призна

Признак

Юризнак ре

Эулылаща число ии клод м-.

ff0HE4/