Устройство для передачи информации

Иллюстрации

Показать всеРеферат

Изобретение относится к информационно -измерительной технике иможет использоваться в телеметрических системах. Устройство производит опрос телеметрируемых параметров и интегральное накопление этих параметров . За счет использования побитной обработки параметров повышается информативность устройства. Устройство содержит счетчик I , коммутатор 2, узел 3 сжатия данных, включающий в себя пороговый элемент 4, триггер 5, элемент И 6, блок 7 памяти и:ре-. зистор 8, сумматор 10 по модулю два, блок 13 синхронизации, триггер 12, элемент ИИ, блок памяти 9 и шину 4 единичного потенциала. 3 ил. с %б (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„, SU» 1462391 А1 (58 4 G 08 С 19/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

Il0 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4310961/24-24 (22) 17.07.87 (46) 28.02.89. Бюл. N - 8 (71) Государственный всесоюзный центральный научно-исследовательский институт комплексной автоматизации (72) Н,К. Архипова, В .Г . Микуцкий и Л.С. Нагирнер (53) 621 .398(088.8) (56) Модуль коммутации и преобразования частотных сигналов А611-23:

Руководство по эксплуатации

3.038.011 РЭ.

Авдеев Б.Я., Антонюк Е.М. и др.

Адаптивные телеизмерительные системы.— Л.: Энергоиздат, 1981, с. 100, рис. 3-26. (54) УСТРОИСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ (57) Изобретение относится к информационно-измерительной технике и может использоваться в телеметрических системах. Устройство производит onрос телеметрируемых параметров и интегральное накопление этих параметров . За счет использования побитной обработки параметров повышается информативность устройства. Устройство содержит счетчик 1, коммутатор

2, узел 3 сжатия данных, включающий

:в себя пороговый элемент 4, триггер

5, элемент И 6, блок 7 памяти и:резистор 8, сумматор 10 по модулю два, блок 13 синхронизации, триггер 12, элемент И 11, блок памяти 9 и шину

14 единичного потенциала. 3 ил.! 462391

Изобретение относится к информационно-измерительной технике и может использоваться в телеметрических системах для накопления интегральных значений измеряемых параметров .

Цель изобретения — повышение информативности устройства.

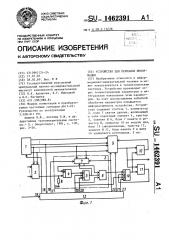

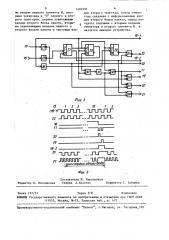

На фиг. 1 изображена структурная схема устройства1 на фиг . 2 — функ- 10 циональная схема блока синхронизации; на фиг. 3 — временные диаграммы, поясняющие работу блока синхронизации.

Устройство для передачи информации содержит счетчик 1, коммутатор 2, узел 3 сжатия данных, выполненный на пороговом элементе 4> первом. триггере 5, первом элементе И 6, первом блоке 7 памяти и ограничи- 20 тельном элементе (резисторе) 8, второй блок 9 памяти, суммагор 10 по модулю два, второй элемент И 11, второй триггер 1 2, блок 13 синхрониза : ции, шину 14 единичного потенциала, -тактовый 15 и управляющие 16 входы и первый 17 — седьмой 23 выходы блока 13 синхронизации.

Блок 13 синхронизации содержит элементы НЕ 24 и 25, элемент 26 задер.30 жки, триггеры 27-29, элемент 30 неравноэначности, элемент 31 задержки элементы И-НЕ 32 и 33, элементы И

34 и 35 и элемент И-HE 36.

Устройство работает следующим об- 35 разом.

На информационные входы устройст- . ва поступают сигналы от датчиков с дискретными уровнями "0" и "1 ". Для каждого информационного входа в бло- 40 ке 9 памяти хранится значение измеряемого параметра, которое увеличивается на единицу, если на входе произошло изменение сигнала "0" в "1".

По тактовому входу устройства на блок 13 синхронизации поступает импульсная последовательность, кото- . рая вызывает появление на его выходах .управляющих сигналов в соответствии с временной диаграммой на фиг.. 3. Импульсы с выхода 18 блока

13 поступают на счетный вход счетчика 1 выходы старших разрядов которого подключены к адресным входам ком 55 мутатора 3. Старшие разряды счетчика

1 задают также адрес ячейки в блоке

7 памяти, которая хранит предыдущее значение опрашиваемого канала.

Выход блока

7 паВыход элементаИ6

Выход порогового

Выход коммутатора

2. элемента мяти

1

1

0

Промежуточный уровень 1

Промежуточный уровень 0

1

Как следует из таблицы, сигнал на выходе узла 3 возникает при изНа каждом цикле опроса узел 3 сжатия данных формирует на выходе элемента И 6 импульс, если по отношенюо к предыдущему циклу опроса на данном входе произошло изменение сигнала

"0" и "1". Этот импульс устанавливает в "1" триггер 12.

В цикле опроса каждого информационного входа устройства на выходе блока 9 памяти последовательно начиная с младшего разряда формируется двоичный код измеряемого параметра опрашиваемого канала. Адреса ячеек блока 9 памяти для каждого бита измеряемого параметра задаются с помощью младших разрядов счетчика 1 .

Для увеличения значения измеряемого параметра на единицу служит схема, содержащая сумматор 10, триггер 12 и элемент И 11. Триггер 12 фиксирует изменение .состояния входа, а также служит для формирования сигнала переноса в следующий разряд, Новое значение каждого разряда измеряемого параметра с выхода сумматора 10 записывается в ячейку блока

9 по тому же адресу. При возникновении переноса в следующий разряд от элемента И ll подтверждается взведенное состояние триггера 12. Содер- жимое блока 9 может быть считано с выхода устройства одновременно с приращением параметра либо в какой либо другой момент времени, Узел 3 сжатия данных работает в соответствии со следующей таблицей истинности

14 менении сигнала иэ состояния 0" в состояние "1 " . В том случ ае, когда сигнал, поступающий с выхода коммутатора 2, имеет уровень "0" или "1", в соответствующую ячейку блока 7 записывается новое состояние опрашиваемого входа. Если сигнал, поступающий с выхода коммутатора 2, искажен помехой и имеет промежуточное значение между "0" и "1", в соответствующей ячейке блока 7 памяти сохраняется прежнее значение. В этом случае на первом входе порогового элемента 4 через резистор 8 действует сигнал высокого уровня, соответствующий "1".

Состояние выхода порогового элемента 4 определяется состоянием его второго входа. В соответствующую ячейку блока 7 вновь записывается прежнее состояние опрашиваемого входа устройства. Величина резистора 8 определяется используемой элементной базой и заданной помехоустойчивостью. В качестве порогового элемента 4 применен триггер Шмидта с элементом И на входе.

Блок 13 синхронизации обеспечивает формирование управляющих сигналов в соответствии с временной диаграммой на фиг . 3. На выходе блока 13 действуют следующие сигналы: 18-1 — счетные импульсы 18-2— сигнал разрешения счета; 17 — стробы записи и чтения блока 7 памяти;

19 — строб:триггера 5; 20 — импульс сброса триггера 5; 22 — сигнал чтения (записи) блоков 7 и 9 памяти;

21 — стробы записи и чтения блока

9 памяти; 23 — строб триггера 12.

Устройство реализовано на следующих элементах: счетчик 1 — К561ИЕ10, блок 7 и 9 памяти — К561РУ2, пороговый элемент 4 — К561ТЛ1, коммутатор

2 — К561 КП2, сумматор 1 0 — К561ЛП2.

В качестве базового объекта принят блок У-81, входящий в состав телемеханического комплекса УВТК-УН.

Блок У-81 использует суммирующий счетчик для каждого канала и обеспечивает опрос четырех входных каналов, Разработанный блок У-90, в котором реализовано предложенное устройство на том же конструктиве (одна плата

УТК) позволяет опрашивать 64 входных канала. При среднем числе каналов на одно устройство комплекса

64 одна плата блока У-90 позволяет

62391

4 заменить 8 плат У вЂ” 81. Таким образом, устройство обеспечивает по сравнению с базовым объектом сокращение

5 объема оборудования эа счет использования побитной обработки измеря„емого параметра, повышение информативности устройства .

S0

Формула изобретения

Устройство для передачи информации, содержащее коммутатор, информационные входы которого являются информационными входами устройства, блок синхронизации, первый выход которого соединен с первым управляющим входом первого блока памяти, второй блок памяти, шину единичного потенциала и пороговый элемент, о тл и ч а ю щ е е с я тем, что, с целью повьппения информативности устройства, в него введены счетчик, триггеры, ограничительный элемент, элементы И и сумматор, выходы первой группы счетчика соединены с соответствующими первыми адресными входами второго блока памяти и ад" ресными входами блока памяти и коммутатора, выход коммутатора соединен с первым входом порогового элемента и первым входом ограничительного элемента, выход которого подключен к шине единичного потенциала, выход порогового эЛемента соединен с информационным входом первого триггера, выход которого соединен с первым входом первого элемента И и информационным входом первого блока памяти, выход которого соединен с вторыми входами порогового элемента и первого элемента И, выход которого соединен с входом установки в "1" второго триггера, вьмод которого соединен с первыми входами сумматора и второго элемента И, выход второго элемента

И соединен с информационным входом второго триггера, выходы второй группы счетчика соединены с соответствующими вторыми адресными входами второго блока памяти, управляющий вход блока синхронизации подключен к одному из выходов второй группы счет ика, тактовый вход блока синхронизации является тактовым входом устройства, второй — седьмой выходы блока синхронизации соединены соответственно с входом счетчика, такто вым входом первого триггера и треть".

1462391

17

15 7 Я 3 16 1 2

r,â. nnrLrl,,1 Г1 П.П.Г

zz П . - . ...

° ° Ф

° ° °

1 ° °

19 е ° ° .18-Г

Э ° ° гз - - -Составитель М. Никуленков

Редактор Л. Пчолинская, Техред А.Кравчук

Корректор Л. Зайцева

Заказ 727/51 Тираж 518 Подписное

ВНИИПИ Государственного комитета по изобретениям и .открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãîpîä, ул. Гагарина, 101 им входом первого элемента И, входами установки в "0" первого и второго триггеров, первым управляющим входом второго блока памяти, вторыми управляющими входами первого и второго блоков памяти и тактовым входом второго триггера, выход сумматора соединен с информационным входом второго блока памяти, выход которого соединен с вторыми входами сумматора и второго элемента И и является выходом устройства.