Устройство для формирования частотно-манипулированных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радио- ;технике и может использоваться в частотно-временных системах телеме- .ханики. Цель изобретения - повьппение точности формирования частотно-манипулированных сигналов. Устр-во содержит блок питания 1, блок установки 2 в нуль, синтезатор- 3 сетки частот, фазовращатели 4 и 5, коммутатор 6, передающий фильтр 7, триггеры 8 и 9, интеграторы 10, 11 и 12, каждый из которых состоит из формирователя 13 прямоугольных импульсов и интегрируюс{ей цепочки 14, блоки выборки и хранения 15, 16, 17 и 18, источники 19 и 20 опорного напряжения, блоки сравнения 21 и 22 и ключи 23 и 24. Цель достигается путем снижения межсимвольных помех. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦ ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (б11 4 Н 04 1 27/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

8-89

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

fl0 ИЗОБРЕТЕНИЯМ И OTHPbtTHRM

ПРИ ГКНТ СССР (21) 4132264/24-09

1 (22) 08.10.86 (46) 28.02.89. Бюл. Р 8 (71) Донецкий филиал Института

tt

"Гипроуглеавтоматизация (72) Н.А.Чехлатый и В.А.Кисель (53) 621.376.52(088.8) (56) Авторское свидетельство СССР

Р 1190462, кл. Н 03 С 3/00, 1985. ,(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ЧАСТОТНО-ИАНИПУЛИРОВАННЫХ СИГНАЛОВ (57) Изобретение относится к радио;:технике и может использоваться в частотно-временных системах телеме,ханики. Цель изобретения — повьппение

ÄÄSUÄÄ 462508 А1 точности формирования частотно-манипулированных сигналов. Устр-во содержит блок питания 1, блок установки 2 в нуль, синтезатор 3 сетки частот, фазовращатели 4 и 5, коммутатор 6, передающий фильтр 7, триггеры 8 и 9, интеграторы 10, 11 и 12, каждый из которых состоит из формирователя 13 прямоугольных импульсов и интегрирующей цепочки 14, блоки выборки и хранения 15, 16, 17 и 18, источники

19 и 20 опорного напряжения, блоки сравнения 21 и 22 и ключи 23 и 24.

Цель достигается путем снижения межсимвольных помех. 1 ил.

1462508

Изобретение относится к радиотехнике и может бьггь использовано в частотно-временных системах телемеханики.

Цель изобретения — повьппение точ5 ности формирования путем снижения межсимвольных помех.

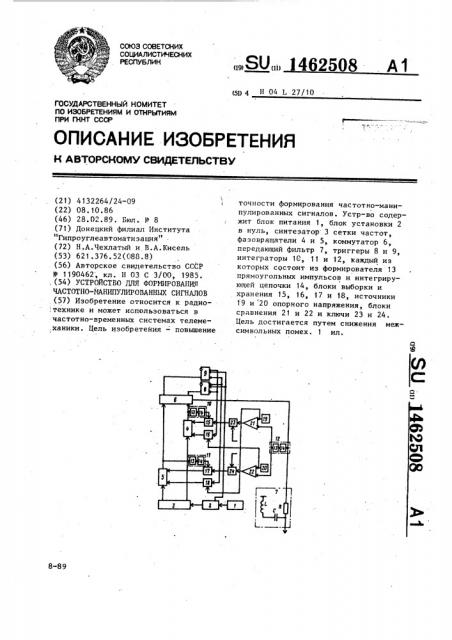

На чертеже представлена структурная электрическая схема устройства.

Устройство для формирования час, тотно-манипулированных сигналов содержит блок 1 питания блок 2 устаФ новки в нуль, синтезатор 3 сетки частот, первый и второй фазовраща- 15 ! етли 4 и 5, коммутатор 6, передаю щий фильтр 7, первый и второй триг,,геры 8 и 9, первый, второй и третий ! ! интеграторы 10-12 каждый из котоЭ, рых состоит из формирователя 13 пря- 20, моугольных импульсов и интегрирующей, цепочки 14, первый, второй, третий !

; и четвертый блоки 15-18 выборки и

,хранения, первый и второй источники

, 19 и 20 опорного напряжения, первый 25 и второй блоки 21 и 22 сравнения,,.первый и второй ключи 23 и 24.

Устройство работает следующим, образом.

При включении блока 1 питания, 30 . включается блок 2 установки в нуль. ( Сигнал с выхода блока 2 устанавливает в исходное состояние первый, второй .и третий интеграторы 10-12, первый и второй триггеры 8 и 9, первый, вто;-.. ,рой, третий и четвертый блоки 15-18, выборки и хранения и включает синте,затор 3 сетки частот.

С первого и второго выходов синте затора 3 сигналы рабочей частоты 40 и Г поступают соответственно на входы первого и второго фаэовращателей 4 и 5, и через них соответственно — на первый и второй входы коммутатора 6 и на первый и второй 45 интеграторы 10 и 11. В формирователях 13 всех интеграторов,10-12 формируются прямоугольные импульсы, длительность которых равна периоду следования высокочастотных импульсов на их входах и затем с помощью ин50 тегрирующих цепочек 14. преобразуется в амплитуду.

С выходов первого и второго интеграторов 1О и 11 сигналы поступают соответственно на входы первого и третьего блоков 15 и 17„ которые производят выборку сигнала при наличии на их управляющем входе переднего

Ъ фронта импульса соответствующего ключа 23 и 24. Амплитуда сигнала на выходе первого, второго и третьего интеграторов 10-12 в момент выборки определяет величину фаэового рассог-. ласования между высокочастотным сигналом, поступающим на передающий фильтр 7, и входным сигналом первого и второго фазовращателей 4 и 5. В каждый момент времени первый и второй блоки 15 и 16 находятся в режиме хранения, а третий .и четвертый блоки

17 и 18 — в ждущем режиме.

При поступлении сигнала манипуляции на управляющий вход первого ключа 23 последний открывается при равенстве амплитуды напряжения на выходе третьего интегратора 12 напряжению установки первого источника

19 опорного напряжения. Сигнал с выхода первого ключа 23 поступает на первый и второй блоки 15 и 16 и на первый и второй триггеры 8 и 9.

Передним фронтом импульсов первый и второй блоки 15 и 16 производят выборку сигнала, поступающего с первого интегратора 10 и с второго источника 20 опорного напряжения..Beличина уставки пропорциональна на-: чальной фазе синусоидального у сигй нала ВЧ посылки частотой f и выбирается из условия отсутствия свободнои составляющей переходного процесса при включении частоты.

Сигнал с выхода первого блока 15 поступает на второй управляющий вход первого фазовращателя 4, осуществляя при этом подстройку фазы сигнала Е о в пределах от 0 до. -360 в зависимости от уровня сигнала выборки, а опорное напряжение, пропорциональное с выхода второго блока 16 выборки и хранения поступает на первый управляющий вход первого фаэовращателя 4, осуществляя подстройку фазы в соответствии с усч авкой.

Одновременно с этим, сигнал с выхода первого ключа 23 приводит включение первого триггера 8 и вык лючение второго триггера 9. Сигнал с выхода первого триггера 8 поступает на управляющий вход коммутатора 6, на выходе которого происходит смена ВЧ посылки. При этом первый и второй блоки 15 и 16 обеспечивают хранение сигнала на время формирования ВЧ посылки f< . Выходной сигнал

08 з 14625 с коммутатора 6 поступает на передаю-. щий фильтр 7.

В следующем такте при поступле= нии манипулирующего сигнала на управ5 ляющии вход второго ключа 24,последний открывается при равенстве фазы

ВЧ сигнала t, поступающего на передающий фильтр 7, и уставки второго источника 20. Величина уставки выби- .10 рается из условия отсутствия свободной составляющей переходного процесса при отключении частоты f

Сигнал с выхода второго ключа 24 поступает на третий и четвертый блоки 17 и 18 и на первый и второй триггеры 8 и 9. Передним фронтом импульса третий и четвертый блоки

17 и 18 выборки и хранение производят выборку сигнала, поступающего 2О из второго интегратора 11 и первого источника 19 опорного напряжения.

Величина уставки пропорциональна начальной фазе(>, сигнала f, и выби- 25 рается из условия отсутствия свободной составляющей переходного процесса при ° включении частоты f . Сигнал с выхода третьего блока 17 поступает на первый управляющий вход второго 30 фазовращателя 5, осуществляя при этом подстройку фазы ВЧ .сигнала в пределах от 0 до -360, а сигнал с выхода четвертого блока 18 выборки и хранения поступает на второй вход второго фазовращателя 5, осуществляя подстройку фазы в соответствии с уставкой первого источника 19 опорного напряжения.

Формула из о бр ете ния

Устройство для формирования частотно-манипулированных сигналов, содержащее последовательно соединенные блок питания, блок установки в нуль и синтезатор сетки частот, выходы которого подключены к сигнальным входам первого фазовращателя, управляющие входы которого соединены с выходами первого и второго блоков выборки и хранения, и второго фазовращателя, управляющие входы которого соединены с выходами третьего и четвертого блоков выборки и хранения, а выходы первого и второго фазовращателей подключены соответственно к входу первого интегратора, выход которого соединен с сигнальным входом первого блока выборки и хранения, к первому сигнальному входу коммутато- . ра, к входу второго интегратора, выход которого соединен с сигнальным входом третьего блока выборки и хранения, и к второму сигнальному входу коммутатора, управляющие входы и выход которого соединены соответственно с выходами первого и второго триггеров и с входом третьего интегратора, который подключен к входу передающего фильтра, выход которого является выходом устройства, при этом управляющие входы первого и второго блоков выборки и хранения соединены с первыми установочными входами первого и второго триггеров, вторые и третьи установочные входы которых соединены соответственно с вторым выходом блока установки в нуль и с управляющими входами третьего и четвертого блоков выборки и хранения, о. т .л и ч а ю щ е е с я тем, что, с целью повышения точности формирования путем снижения межсимвольных помех, введены два ключа, два блока сравнения и два источника опорного напряжения, выходы которых подключены соответственно к первому входу первого блока сравнения, выход которого соединен с сигнальным входом первого ключа, и к первому входу второго блока сравнения, выход которого соединен с сигнальным входом второго ключа, выход которого и выход первого ключа соединены соответственно с управляющими входами четвертого и второго блоков выборки и хранения, к сигнальным входам которых подключены соответственно выходы первого и второго источников опорного напряжения, причем выход третьего интегратора подключен к вторым входам блоков сравнения, а управляющие входы ключей являются управляющими входами устройства.