Когерентный приемник частотномодулированных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - расширение полосы захвата при наличии частотной расстройки между прижимаемым и опорным сигналами и сокращение времени установления синхронизации. Когерентньш приёмник содержит квадратурные преобразователи 1 и 7, формирователь 2 опорных сигналов, управляемый г-р 3, фильтр 4 нижних частот, блок регенерации 5 информационных символов и блок тактовой синхронизации 6. Цель достигается введением блока преобразования 8 сигналов, измерителя 9 интервалов времени, блока вычисления (БВ) 10 частотного рассогласования, БВ 11 фазового рассогласования, БВ 12 рассогласования по задержке и блока устранения 13 обратной работы. Даны ил. выполнения блоков когерентного приемника. 11 ил. i (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

09) S (ш

А1 (5D 4 Н 04 L 27/14

ВНЫИЗМ3

ПАТЕНЕ"-1 ХКйЧЕСКР.Л;

, ; Б Д (-1 Д « ()., Д

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Фиг.1.

8-89

ГОСУДАРСТНЕНКЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4087609/24-09 (22) t4.07.86 (46) 28.02.89. Бюл. Р 8 (71) Московский авиационный институт им.Серго Орджоникидзе (72) П.П.Загнетов (53) 621.394.62 (088.8) (56) Hirade К., Muwta К. "А study of

Nodulation for Digital Mobil Telephony IEKE 29h Vehicalar Technic

Conferation, 1979, р. 16. (54) КОГЕРЕНТНЫЙ ПРИЕМНИК ЧАСТОТНОМОДУЛИРОВАННЫХ СИГНАЛОВ ° (57) Изобретение относится к технике связи. Цель изобретения — расширение полосы захвата при наличии частотной расстройки между прижимаемым и опорным сигналами и сокращение времени установления синхронизации. Когерентный приемник содержит квадратурные преобразователи 1 и 7, формирователь

2 опорных сигналов, управляемый г-р

3, фильтр 4 нижних частот, блок регенерации 5 информационных символов и блок тактовой синхронизации 6. Цель достигается введением блока преобразования 8 сигналов, измерителя 9 интервалов времени, блока вычисления (БВ) 10 частотного рассогласования, БВ 11 фазового рассогласования, БВ

12 рассогласования по задержке и блока устранения 13 обратной работы.

Даны ил. выполнения блоков когерентного приемника. 11 ил.

1462510

Изобретение относится к технике связи и может использоваться для когерентного приема цифровых сообщений в системах связи, использующих частотно-модулированные (ЧИ) сигналы с малым индексом девиации.

Цель изобретения — расширение полосы захвата при наличии частотной расстройки между принимаемым и опорным сигналами и сокращение времени установления синхронизации.

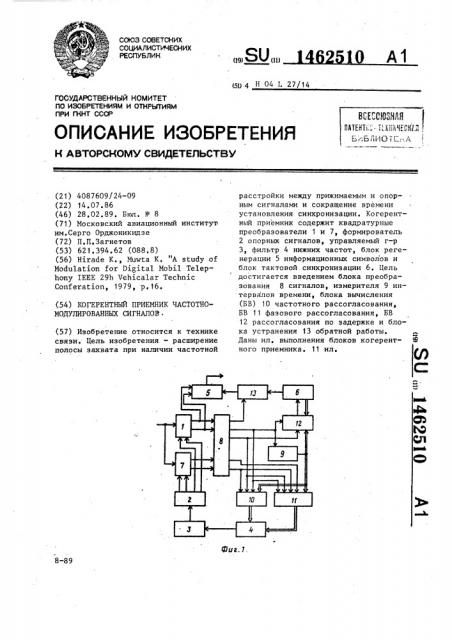

На фиг. 1 приведена структурная схема когерентного приемника ЧМ сигналов, на фиг.2 - функциональная схема блока тактовой синхронизации, на фиг.3 — функциональная схема блока (преобразования сигналов, на фиг.4-7схемы субблоков блока преобразования сигналов, на фиг.8 — функциональная схема измерителя интервалов времени, на фиг.9 — функциональная. схема блока вычисления частотного рассогласования, на фиг.10 — функциональная схема блока вычисления рассогласования .по задержке, на фиг.11 - функци-. ональная схема блока устранения об ратной работы.

Когерентный приемник содержит первый квадратурный преобразователь (КП) 1, формирователь 2 опорных сигналов, управляемый генератор (УГ) 3, фильтр 4 нижних частот (ФНЧ), блок 5 регенерации информационных символов,," блок 6 тактовой синхронизации (БТС), второй квадратурный преобразователь

7, блок 8 преобразования сигналов (БПС), измеритель 9 интервалов времени (ИИВ), блок 10 вычисления частотного рассогласования (БВЧР), блок 1 1 вычисления фазового рассогласования, блок 12 вычисления рассогласования по задержке -(БВРЗ), блок 13 устранения обратной работы.

Блок 6 тактовой сикхронизации содержит фильтр 14 нижних частот, блок

15 добавления-исключения (БДИ), опорный генератор (ОГ) 16 и счетчик-делитель 17. Блок 8 преобразования сигналов содержит субблоки 18-24. Каждый из субблоков 18-21 содержит инвертор ?5, элементы 26 и 2? задержки, элементы И 28 и 29.

Субблок 22 содержит два многовхо" довых элемента И-ИЛИ 30 и 31, а также

RS-триггер 32. Субблок 23 содержит два четырехвходовых элемента ИЛИ 33 и 34, элемент ИЛИ 35, RS-триггер 36, элементы И-ИЛИ 37 и 38, а также RS-триггер 39. Субблок 24 содержит четыре многовходовых элемента И-ИЛИ 40-43, два элемента ИЛИ 44 и 45, RS-триггер

46, D-триггер .47. Измеритель 9 интер5 валов времени содержит счетчик 48 и генератор 49 счетных импульсов.

Блок 10 вычисления частотного рассогласования содержит первую и вторую ячейки 50 и 51 памяти, вычитатель

52, инвертор 53, блок 54 сравнения, элемент И 55 и ключ 56. Блок 12 вычисления рассогласования по задержке содержит первую и вторую ячейки 57 и 58 памяти, вычитатель 59, блок 60 сравнения, инвертор 61, элемент И 62 и ключ 63. Блок 13 устранения обратной работы содержит IK-триггер 64, логический ключ 65, два элемента ИЛИ

66 и 67, реверсивный счетчик 68, генератор 69 счетных импульсов и RSтриггер 70.

Когерентный приемник работает следующим образом.

Входной сигнал Y(t) поступает на

25 первые входы первого и второго квадратурных преобразователей (КП) 1 и

7, которые формируют квадратурные составляющие Х, Y V и W:

30 Х=Б )Y(t) (ЯМ„t+Qу));

Y=Sgn jYCt) sin(u>„t+6>„)

V=Sgn PY(t) cos(Q>„t+И4+ г)

W=Sgn (Y(t) sin(u>, + ь/4+8>,)) где $8п(Х) - знаковая функция, принимающая значение "1" при

40 XR0 и "О" при Х О;

Ы„,и 9> соответственно частота и фаза опорного сигнала, формируемого УГ 3.

45 Черта над произведением входного и опорного сигналов означает операцию усреднения. Квадратурные составляющие входного сигнала V u W вычис" ляемые вторым КП 7, отличаются от составляющих Х и Y формируемых первым

КП 1, тем, что опорные сигналы второго КП 7 дополнительно сдвинуты по фазе на Т /4.

УГ 3 управляется напряжением, по55 ступающим на его вход с выхода ФНЧ 4.

Первый вход ФНЧ 4 является входом для сигнала частотного рассогласования, второй — входом сигнала фазового рассогласования. з

14

БТС 6 наиболее часто реализуется в цифровом виде (фиг.2). Сигнал рассогласования по задержке с выхода

БВРЗ 12 поступает в ФНЧ 14 БТС 6, который реализуется либо на реверсивном накопительном сумматоре, либо на реверсивном счетчике. Выходными сигналами фильтра являются сигналы добавления-исключения импульсов, которые в БДИ 15 либо исключают один из импульсов ОГ 16, либо добавляют импульс в последовательность импульсов, поступающую от генератора. Счетчикделитель 17 делит частоту входной по" следовательности импульсов так, что частота импульсов на выходе счетчика равна тактовой частоте. Сигнал тактовой частоты в виде меандра поступает на первый выход БТС 6, на второй выход которого поступает код числа импульсов, подсчитанных счетчиком делителем БТС 6.

Введенный второй КП 7 по выполняемым функциям и схемному решению идентичен первому КП 1. Единственным отличием является то, что опорные " сигналы, поступающие на первый и второй входы второго КП 7 смещены по отношению к опорным сигналам первого

КП 1, что приводит к формированию квадратурных составлянлуих V и W, сдвинутых по фазе несущей на 7/4 по отношению к квадратурным составляющим

Х иУ.

Выходные квадратурные сигналы первого и второго КП 1 и 7 поступают в

БПС 8, схема которого для удобства восприятия представлена в виде двух уровней декомпозиции. Первый уровень приведен на фиг.3, где БПС 8 представлен в виде субблоков, логическая структура которых раскрыта на схемах (фиг.4-7). На фиг.4 приведена схема субблоков 18-21, одинаковая для всех г этих субблоков. Вйходные сигналы 71 и 72 субблока 18 (фиг.4) представляют собой прямой и инвертированный входной сигнал. На выходе 73 формируется импульс, если входной сигнал меняется от низкого уровня (".О") к . высокому ("1"). Длительность импульса равна величине задержки сигнала в элементе задержки 27. На выходе 74 появляется импульс, если входной сигнал меняется от "1" к "О". Сформированные в субблоках 18-21 логические сигналы поступают в субблоки 22-24, Выход 75 БПС 8 соответствует первому

62510 выходу 75 субблока 23. Сигнал íà первом выходе описывается логической функцией

Ф= (X2+X4+Y6+YS) +(V10+V12+W14+W16) где + — знак логического ИЛИ;

Х2, Y6 — сигналы на вторых выходах субблоков 18 и 19 соответственно и т.д.

Сигнал Ф имеет следующий физический смысл. Гармонический сигнал, частота которого отличается от частоты опорных сигналов квадратурного преобразователя, представляется в виде вектора, проекции которого на ортогональные оси декартовых координат и есть квадратурные составляющие Х и Y. При вращении вектора точка, со" ответствующая его концу, пересекает поочередно оси Х и Y. При пересечении, например, положительной полуоси

25 X (X> О) квадратурная составляющая

Y меняется от низкого уровня ("О") к высокому. Поскольку сигнал Ф объединяет все импульсы, формирующиеся при смене знака квадратур Х, Y u V

И, то можно назвать сигнал Ф "фактом пересечения" одной из полуосей систем координат Х, Y u V W.

Логический сигнал, соответствующий первой скобке, представляет собой

"факт пересечения" одной из полуосей

Х, Y, сигнал, соответствующий второй скобке, — "факт пересечения" одной из полуосей Ч, W. Эти сигналы управляют

«состоянием первого КБ-триггера 36 (фиг.6), на выходе которого сигнал

Q,=1 означает, что последнее пересечение было пересечением одной из полуосей Х, Y.

В момент очередного пересечения полуосей Х, Y или V, W фиксируется

45 состояние второго RS-триггера 39, выходной сигнал 76 которого поступает на второй выход БПС 8. Установление состояния Q =0 означает, что пересечена полуось, которая, пересеклась

50 предыдущий раз, т.е. Я =О, соответст,вует пересечению одной и той же полуоси. Состояние Q =1 означает, что пересечена соседняя полуось. В этом же субблоке 23 формируется сигнал, поступающий на четвертый выход 77

БЛС 8. Этот сигнал при Q =1 соответствует пересечению одной из полуосей

V, W а при Q 0 — пересечению одной из полуосей Х, Y.

Сигнал, поступающий на S-вход

RS-триггера 46 субблока 24 описывается логическим выражением

14625

j(Y5" Х4)+(Х36Y8)+(Y7> X2)+(Xl х Y6)) +

+ ((W13 Ч12)+(Ч11»916)+(915»V10)+

+(V9x 014)j S, а сигнал, поступающий на вход R, — выражением

p(Y5xX2) +(ХЗ xY6) y(Y7>rX4) y(X1x Y8)) +

+ P(M13x V10)+(V11x %14) +(W15 х V12)+

+(V9»W16)) R» где х — знак логического умноже" ния И.

Состояние RS-триггера 46 Я =1 оз3 ачает, что полуось пересечена при движении вектора против часовой стрелки. Состояние RS-триггера 46 «переписывается в Э-триггер 47 сигналом Ф, поступающим с первого выхода 75 субблока 22. На выход 78 БПС 8 поступает состояние Я4.. Условно сигМал на выходе 78 БПС 8 можно назвать . знаком пересечения".

Логический сигнал, поступакиций на

КБ-триггера 32 субблока 22 (фиг.5), Описывается выражением

30 ((W13»V12)+(W15 Ч10)+(Ч9»916)+

+(Ч!1»>)14))»

I 35

4 сигнал, поступающий íà S-вход,фыражением ((79 w 014) +(V11« V10) +(815>: V12) +

+(W13« V10)j .

45

АИВ 9 (фиг.8) обеспечивает измерение интервала времени между двумя очередными пересечениями полуосей.

Сигнал "Факт пересечения" с первого выхода 75 БПС 8 поступае" на вход сброса счетчика 48, на счетный вход к)оторого поступают импульсы от генератора счетных импульсов 49. Число

Состояние (=1 КЯ-триггера 32 субблока 22 соответствует нахождению векто" ра входного сигнала в пределах сек" тора от ()/4.до 3«/4 и от 5«/4 до

71(/4. Если вектор располагается в пределах от - 7/4 до н /4 и от 3«/4 до 511 /4 то QD Состояние КЯ-тржтера 32 субблока 22 поступает на пятый выход 79 Бпс 8. 50

10 о импульсов, подсчитанное счетчиком к моменту очередного сброса, пропорционально длительности интервала времени между моментами пересечения полу.осей. Выходной сйгнал ИИВ 9 (число

М ) используется в блоках, вычисляющих рассогласование по частоте, фазе и задержке.

Функциональная схема БВЧР 10 показана на фиг.9. Сигнал с выхода 80

ИИВ 9, поступающий на второй вход

81 БВЧР 10, записывается в первую ячейку 50 памяти в момент поступления на первый вход 82 импульса Ф, соответствующего пересечению одной из полуосей. Вычитающий блок определяет разницу ЙМ=М -M/2, где M - число, подсчитанное счетчиком ИИВ 9, Мчисло импульсов, которое насчитывает счетчик ИИВ 9 за время, равное длительности такта Т.

Число M/2 хранится во второй ячейке 51 памяти. Разность а М поступает с выхода вычитателя 52:в инвертор 53, в котором знак числа ЬМ меняется на противоположный, если логический сигнал "Знак пересечения", поступающий на четвертый вход 83 БВЧР 10, имеет низкий уровень.("0"). Число

0М со скорректированным знаком поступает через ключ 56 на выход БВЧР 10, если сигнал, поступающий на третий вход 84 БВЧР 10, имеет высокий уровень ("1"), что соответствует пересечению двух соседних осей.При этомблок сравнения 54 выдает "1", что соответствует выполнению условия М„ сМ.

При наличии расстройки по частоте между несущим колебанием и опорными сигналами скорость вращения вектора будет отличаться от номинальной, при которой две смежные оси пересекаются через время, равное Т/2. Условие

Ми «М, разрешающее выдачу сигнала рассогласования при пересечении смежных осей, используется для того, чтобы исключить случаи, когда две соседние оси не пересекаются эа время, равное Т, что может происходить только при расстройках по частоте, сравнимых с F т/4, где P т=1/Т.

Функциональная схема блока 11 вычисления фазового рассогласования аналогична схеме БВЧР 10. Отличие заключается в том, что сигнал рассогласования на выход блока поступает только в том случае, если пересекается Одна и.та же Осьу и Ми«2М.

7 14625

Функциональная схема БВРЗ 12 приведена на фиг.10 ° Число М, поступаи ющее с выхода 85 ИИВ 9 на второй вход 86 БВРЗ 12, записывается в ячейку 57 памяти со сдвигом на разряд (т.е. как М„/2) в момент поступления сигнала Ф "Факт пересечения" на первый вход 87 блока. Одновременно в ячейку 58 памяти записывается число, поступающее на четвертый вход

88 с выхода 89 БТС 6. Разница этих чисел характеризует величину расстройки по задержке, если частота импульсов, поступающих в счетчик-делитель 17 БТС 6, равна частоте импульсов ГСИ 49 ИИВ 9. Прохождение сигна,ла рассогласования по задержке на выход 90 БВРЗ 12 разрешается только при пересечении одной и той же оси и при условии, что число М„/2 (М, Проверка условия Ми/2 M осуществляется в блоке 60 сравнения БВРЗ 12.

Для работы блока 5 регенерации информационных символов требуется сигнал полутактовой частоты. Однако при делении тактовой частоты, формируемой БТС 6, на два возникает неопределенность, которая может привести к неправильной работе блока 5.

Для устранения "обратной работы". служит блок 13 устранения обратной работы, в котором осуществляется вычисление корреляции сигнала, поступающего с выхода 79 БПС 8, с одним из" вариантов сформированной полутакто.вой частоты.

Тактовая частота делится в блоке 13 на два с помощью IK-триггера 64.

Если выход "0" этого триггера совпадает по уровням с выходным сигналом

БПС 8, то реверсивный счетчик 68 считает в "+" и при его переполнении устанавливается единичный сигнал на выходе R-триггера 70, который через 45 логический ключ 65 обеспечивает выдачу на выход 91 блока 13 правильного сигнала полутактовой частоты.

Формула изобретения

Когерентный приемник частотно-модулированных сигналов, содержащий блок тактовой синхронизации и первый квадратурный преобразователь> первый 55 вход которого является входом прием10 8 ника, а первый и второй выходы соединены соответственно с первым и вто" рым входами блока регенерации информационных символов, выход которого является выходом приемника, и последовательно соединенные фильтр нижних частот, управляемый генератор и формирователь опорных сигналов, первый и второй выходы которого соединены соответственно с вторым и третьим входами первого квадратурного преобразователя, отличающийся тем, что, с целью расширения полосы захвата при наличии частотной расстройкй между принимаемым и опорным сигналами и сокращения времени установления синхронизации, введены второй квадратурный преобразователь, измеритель интервалов времени, блок вычисления частотного рассогласования, блок вычисления фазового рассогласования, блок устранения обратной работы, блок вычисления рассогласования по задержке и блок преобразования сигналов, выходы которого подключены к сигнальному входу блока устранения обратной работы, тактовый вход которого соединен с выходом блока тактовой синхронизации, к одним входам блока вычисления рассогласования по задержке, который соединен с блоком тактовой синхронизации, к входу измерителя временных интервалов, выход которого соединен с другим входом блока вычисления рассогласования по задержке, и к одним входам блоков вычисления частотного и фазового рассогласования, другие входы и выходы которых соединены соответственно с .выходом измерителя временных интервалов и с входами фильтра нижних частот, при этом первый вход первого квадратурного преобразователя соединен с первым входом второго квадратурного преобразователя, второй и третий входы и выходы которого соединены соответственно с третьим и четвертым выходами формирователя опорных сигналов и с одними входами бло ка преобразования сигналов, к другим входам которого подключены выходы первого квадратурного преобразователя, а выход блока устранения обратной работы подключен к третьему входу блока регенерации информационных символов.

1462510

1462510

Фие.п

O Составитель Д.Куприйчук

Редактор И.Касарда Техред М Ходанич Корректор О.Кравцова

Заказ 738/57 Тираж 627 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат " Патент", г.ужгород, ул. Гагарина,101