Устройство кодирования видеосигнала изображения

Иллюстрации

Показать всеРеферат

Изобретение относится, к технике цифрового телевидения. Цель изобретения - повышение качества кодированного изображения. Устр-во кодирования видеосигнала изображения содержит блок 1 временных задержек, сумматоры 2, 4, 6 и 8, вычитатели 3., 5, 7 и 9, регистры 10, 13 и 14, преобразователь 11 кода, мультиплексор 12, коммутатор 15, блок эл-тов ИЛИ 16 и синхрогенератор 17. Цель достигается путем повьшения помехоустойчивости за счет выявления избыточности разрядов в кодах. Дана ил. выполнений преобразователя 11. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) А1 (51) 4 H 04 N 7/133

ВСЩ

ВПРЯГ - iI

БИБЛ И

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

8-89

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4132396/24-09 (22) 08.09.86 (46) 28.02.89. Бюл. )1 8 (72) С.А.Куликов и С,В.Сардыко (53) 621.397.3 (088.8) (56) Авторское свидетельство СССР

N 792609, кл. Н 04 N 7/12, 1980. (54) УСТРОЙСТВО КОДИРОВАНИЯ ВИДЕОСИГНАЛА ИЗОБРАЖЕНИЯ (57) Изобретение относится. к технике цифрового телевидения. Цель изобретения — повьппение качества кодированного изображения. Устр-во кодирования видеосигнала изображения содержит блок 1 временных задержек, сумматоры 2, 4, 6 и 8, вычитатели 3, 5, 7 и 9, регистры 10, 13 и 14, преобразователь 11 кода, мультиплексор

12, коммутатор 15, блок зл-тов ИЛИ . 16 и синхрогенератор 17. Цель достигается путем повышения помехоустойчивости за счет выявления избыточности разрядов в кодах. Дана ил. выполнения преобразователя 11. 2 ил.

1462515

Ь=ао

2 3

Ь = а+а-,а2 о

3 а,. (1) Ъ =аЭ 0 а — B. +

2 л 1 а

4 л л л (Ъ -Ь, +Ь

-b) 20

1 а и 4 л л и (Ь + Ъ, - Ь

Ъ») л 1 а

3 л h л (Ь, + з ) (2) где Ь, 55

Изобретение относитс» к технике цифрового телевидения и может быть использовано для кодирования видеосигнала изображения.

Цель изобретения — повышение качества кодированного изображения путем повышения помехоустойчивости устройства.

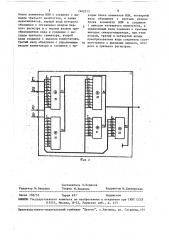

На фиг.1 представлена электрическая структурная схема устройства кодирования видеосигнала изображения, на фиг.2 — схема преобразователя кода °

Устройство кодирования видеосигнала иэображения (фиг.l) содержит блок 1 временных задержек, первый сумматор 2, первый вычитатель 3, второй сумматор 4, второй вычитатель 5, третий сумматор 6, третий вычитатель

У

7, четвертый сумматор 8, четвертый . вычитатель 9, первый регистр 10, пре обраэователь 11 кода, мультиплексор 12, второй и третий регистры 13, 14, коммутатор 15, блок 16 элементов

IHJIH синхрогенератор 17.

Преобразователь,11 кода (фиг.2) содержит сумматоры по модулю. два

18-22.

Устройство кодирования видеосигнала иэображения работает следующим образом.

На вход блока 1 временных задержек поступает видеосигнал в цифровом виде. В блоке 1 временных задержек (осуществляется преобразование четырех (,последовательно поступающих на вход отсчетов видеосигнала в параллельный четырехэлементнын сигнал, поступающий на входы первого и второго сумматоров 2, 4 и входы первого и второго вычитателей 3, 5. Первый, второй, третий, четвертый сумматоры

2, 4, 6, 8 и первый, второй, третий и четвертый вычитатели 3, 5, 7, 9 осуществляют преобразование четырех отсчетов сигнала, поступающего с выходов блока 1 временных задержек в соответствии с преобразованием Адамара. На выходах третьего, четвертого сумматоров 6,„8 и третьего и четвертого вычитателей 7, 9 образуются значения элементов трансформанты. Ес-, ли обозначить значения сигналов на выходах блока 1 временных задержек через a, a<, a ã, aì на выходах третьего и четвертого сумматоров б, 8 — через Ъ, Ь,, íà выходах третьего и четвертого вычитателей 7, 9 через Ь,, Ь,то а; иЪ; (i0123) будут связаны следующими соотношениями

Ь, =а+а+а+а

»Ъ

Л

На приемной стороне элементы а; (i = 0,3) декодируемой группы восстанавливаются по правилу л и а, =4 (Ь, +Ъ, +Ь +Ь) (i 0,3) — элементы трансформанты после огрубления.

30 Шесть передаваем разрядов Ь. . являются старшими разрядами десятиразрядного кода Ь, . Один из трех передаваемых разрядов b; (» . = 1,2,3) является знаковым.

Для каждой кодируемой группы из четырех элементов каждый из трех л элементов трансформанты Ъ, b,,b э 2 Ф сравнивается с нулем. Сравнение производится в блоке t6 элементов ИЛИ.

4 Если все три этих элемента равны нулю, то сигнал на выходе блока 16 будет равен нулю. Из (1) видно, что равенство Ь = b = b = О будет вы< 2 полняться тогда, когда все элементы кодируемой группы имеют одинаковую яркость. В случае Ь = 0 (i п

1,2 3) все элементы а; декодируемой группы равны Ь, /4, что вытекает из (2) . Следовательно, при Ъ = О (i = 1,2,3) передача Ь,, Ъ, Ъ не является необходимой и 9 разрядов, приходящихся на эти коды, являются избыточными. Эта выявленная избыточность используется для повышения помехоустойчивости следующим образом.

В преобразователе 1 1 (фиг,2) для шести разрядов Ь, группы с Ь, = b

О, шести разрядов b,, шести у Ф пу Ag

1»аэрядов в (в сумме) Ь,, Ь, пред1462515

20

35

50 выходом синхрогенератора, коммутатор, первый сигнальный вход которого соединен с выходом преобразователя кода, второй сигнальный вход объединен с сигнальным входом второго регистра

55 шествующей группы вычисляются пять контрольных символов линейного блокового помехоустойчивого кода с 18 информационными символами и 5 проверочл л< ными. Коды Ь, Ь, Ь формируются в первом, втором, третьем регистрах

10, 13, 14. В преобразователь 11 кода пятиразрядный проверочный код дополняется до шестиразрядного кода простым дополнением разряда, равного нулю. Сформированный таким образом шестиразрядный код поступает в коммутатор 15, на другой вход которого поступает другое шестиразрядное слово, состоящее из трех разрядов b, л и трех b

Коммутатор 15 управляется сигналом с выхода блока 16 элементов ИЛИ.

Если данный сигнал равен нулю, т.е. л л л когда b; = Ъ = Ь = О, к выходу коммутатора 15 подключается шестиразрядное слово, включающее пять контрольных символов. В противном случае на выход поступает слово,, составленное из трехразрядных кодов Ь,, которое поступает на вход мультиt плексора 12. Кроме него в мультиплексор 12 передаются шестиразрядный и код Ь, трехразрядный код Ь и сигнал с выхода блока 16 элемейтов ИЛИ.

На выходе мультиплексора 12 формируется выходное шестнадцатиразрядное кодовое слово. Входное слово состоит из четырех восьмиразрядных элементов, то достигается двухкратное сжатие цифрового потока видеоданных.

На приемной стороне анализируется служебная информация, т.е. бит, свидетельствующий о равенстве нулю Ь,, 4

И л

Ь, Ь каждого принимаемого кодового

2 Э слова. Если бит служебной информации л равен нулю, в этом случае Ь, = Ь

= b = О, все а; (i = 0,3) приравниваются Ь /4 и, кроме того, выполняются контрольные проверки. Как и на передающей стороне вычисляются пять контрольных символов для восемьнадцати информационных символов, состоящих из шести разрядов Ь,„и двенадцати разрядов (в сумме) Ь, bI, I 0 . Ь предшествующей группы. По вычисленным проверочным символам определя- ется код места ошибки, а затем производится исправление одиночной ошибки (если она имеется), пришедшейся на шесть разрядов b, группы Ь, = bc, =

= ЬЭ = О или на двенадцать разрядов

III л л

Ь,, Ъ,, Ъ предыдущей группы.

Из описания алгоритма адаптивного помехоустойчивого кодирования элементов трансформанты следует, что прове" рочные символы передаются только для групп равнояркостных элементов. Следствием значительной межэлементной корреляции изображений, с одной стороны, и малым размером кодируемой группы, с другой, является высокая вероятность таких групп. Глаз наиболее чувствителен к ошибкам канала, приходящихся на равнояркостные группы, т.е. на группы, для которых передаются контрольные символы и которые тем самым защищаются.

Формула изобретения

Устройство кодирования видеосигнала изображения, содержащее синхрогенератор и блок временньм задержек, управляющий вход которого соединен с первым выходом синхрогенератора, первый сумматор и первый вычитатель, первые и вторые входы которых соединены соответственно с первым и вторым выходами блока временных задержек, второй сумматор и второй вычитатель, первые и вторые входы которьм соединены соответственно с третьим и четверым выходами блока временных задержек, третий сумматор и третий вычитатель, первые входы ко" торых соединены с выходом первого сумматора, а вторые входы соединены с выходом второго сумматора, .четвертый сумматор и четвертый вычитатель, первые входы которых соединены с выходом первого вычитателя, а вторые входы соединены с выходом второго вычитателя, блок элементов ИЛИ и преобразователь кода, о т л и ч а ющ е е с я тем, что, с целью повышения качества кодированного изображения путем повышения помехоустойчивости устройства, введены первый, второй и третий регистры, управляющие входы которых соединены с вторым и с первым входом блока элементов

ИЛИ и соединен с выходом четвертого сумматора, а третий сигнальный вход объединен с сигнальным входом третьего регистра и с вторым входом

Фцв. 2

Составитель Э.Борисов

Техред М.Ходанич

Р

Редактор М. Бандура

Корректор М.Самборская

Заказ 738/57 Тираж 627 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина,101

5 1 блока элементов ИЛИ н соединен с выходом третьего нычитателя, а также мультиплексор, первый вход которого объединен с сигнальным входом первого регистра и с первым входом преобразователя кода и соединен с выходом третьего сумматора, второй вход соединен с выходом коммутатора, третий вход объединен с управляющим входом коммутатора и соединен с вы462515 6 ходом блока элементов ИЛИ, четвертый вход объединен с третьим входом блока элементов ИЛИ и соединен с выходом четвертого вычитателя, а управляющий вход соединен с третьим выходом синхрогенератора, при этом второй, третий и четвертый входы преобразователя кода соединены соот 10 ветственно с выходами первого, второго и третьего регистров.