Одноразрядный десятичный сумматор

Иллюстрации

Показать всеРеферат

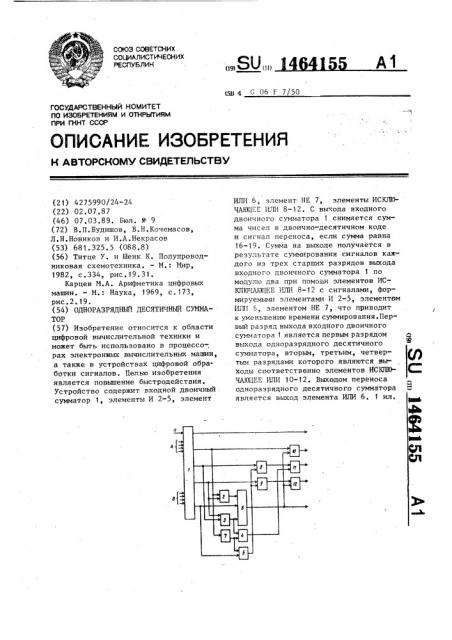

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессо-. pax электронных вычислительных машин, а также в устройствах цифровой обра ботки сигналов. Целью изобретения является повышение быстродействия. Устройство содержит входной двоичньй сумматор 1, элементы И 2-5, элемент ИЛИ 6, элемент НЕ 7, элементы ИСКЛЮ- ЧАКХЦЕЕ ИЛИ 8-12. С выхода входного двоичного сумматора 1 снимается сумма чисел в двоично-десятичном коде и сигнал переноса, если сумма равна 16-19. Сумма на выходе получается в результате суммирования сигналов каждого из трех старших разрядов выхода входного двоичного сумматора 1 по модулю два при помоаш элементов ИСКЛЮЧАЮЩЕЕ lOTi 8-12 с сигналами, формируемым11 элементами И 2-5, элементгм Ш11 5, элементом НЕ 7, что приводит к уменьшению времени суммирования,Первый разряд выхода входного двоичного сумматора 1 является первым разрядом выхода одноразрядного десятичного сумматора, вторым, третьим, четвертым разрядами которого являются вы- , ходы соответственно элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10-12. Выходом переноса одноразрядного десятичного сумматора является выход элемента ИЛИ 6. 1 ил. (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧКСНИХ

РБСПУБЛИН (19) (11) А1 (51) 4 С 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4275990/24-24 (22) 02,07,87 (46) 07.03.89. Бюл, № 9 (72) В.П.Будишов, В.Н.Кочемасов, Л.Н.Новиков и И,А,Некрасов (53) 681.325.5 (088.8) (56) Титце У. и Шенк К, Полупроводниковая схемотехника, — М,: Мир„

1982, с.334, рис.19.31.

Карцев М.А. Арифметика цифровых машин. — M. Наука, 1969, с, 173, рис.2.19. (54) ОДНОРАЗРЯДНЬП1 ДЕСЯТИЧНЬЙ СУММАТОР (57) Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорах электронных вычислительных машин, а также в устройствах цифровой обработки сигналов. Целью изобретения является повышение быстродействия.

Устройство содержит входной двоичный сумматор 1, элементы И 2-5, элемент

ИЛИ б, элемент НЕ 7, элементы HCKJFJЧАЮШЕЕ ИЛИ 8-12. С выхода входного двоичного сумматора 1 снимается сумма чисел в двоично-десятичном коде и сигнал переноса, если сумма равна

16-19. Сумма на выходе получается в результате суммирования сигналов каждого из трех старших разрядов выхода входного двоичного сумматора 1 по модулю два при помоши элементов ИСКЛЮЧАЮ(„)ЕЕ ИЛИ 8-12 с сигналами, формируемыми элементами И 2-5, элементам

ИЛИ б, элементом НЕ 7, что приводит к уменьшению времени суммирования.Первый разряд выхода входного двоичного, сумматора 1 является первым разрядом выхода одноразрядного десятичного сумматора, вторым, третьим, четвертым разрядами которого являются выходы соответственно элементов HCKJII0ЧАЮ1цЕЕ ИЛИ 10-12. Выходом переноса одноразрядного десятичного сумматора является выход элемента ИЛИ 6. 1 ил, 1464155

Изобретение относится к цифровой вычислительной технике и может быть использовано в процессорах электрон- ных вычислительных машин, а также в устройствах цифровой обработки сиг- „ налов.

Цель изобретения — повышение быстродействия, На чертеже представлена функцио- 10 нальная схема одноразрядного деся-тичного сумматора.

Одноразрядный десятичный сумматор содержит входной двоичный сумматор

1 (четырехразрядный), элементы И 2- 15

5, элемент ИЛИ 6, элемент НЕ 7 и элементы ИСКЛБЧА10ЦЕЕ ИЛИ 8-12.

Одноразрядный десятичный сумматор работает следующим образом.

На входы входного двоичного сум- 20 матара 1 поступают числа А и В в цвоично-десятичном коде и сигнал переноса П. С выхода входного двоичного сумматора 1 снимается сумма чисел в двоичном коде и сигнал переноса, если сумма равна 16-19. Выходные сигналы с трех старших разрядов выхода входного двоичного сумматора 1 поступают на входы элементов

И 4 и 5 которые формируют сигналы 30 переноса, если сумча равна 10-15.

Для получения суммы в двоичнодесятичном коде на вторые входы всех элементов ИСКЛЮЧАЮЦЕЕ ИЛИ 8-12 подается уровень логического нуля,, если сумма равна 0-9. При этом сумма на выходе входного двоичного сумматора

1 равна сумме на выходе одноразрядного десятичного сумматора.

Если сумма на выходе входного 0 двоичного сумматора равна 10 (1010)„

11 (1011), 14 (1110), 15 (1111), 18 (10010), 19 (10011) то на вторые входы элементов ИСКЛЮЧАЮЦЕЕ ИЛИ 10 и 12 подается логическая единица, . формируемая элементами И 2 и 3, а также элементом ИЛИ 6. На вторые входы всех остальных элементов ИСКПНИАЮЩЕЕ ИЛИ 8, 9 и 11 подается уровень логического нуля. При этом второй, третий и четвертый разряды вьгхода входного двоичного сумматора

1 складываются по модулю два соответственно с вторым, третьим, четвертым разрядами числа 10 (1010) эле- 5 ментами ИСКЛЮЧАЮЩЕЕ ИЛИ 10-12.;

Когда числа на выходе двоичного входного сумматора 1 равны 12 (11Oa), 13 (1101), на второй вход элемента

11СКЛЮЧАЮЦЕЕ И..П1 11 поступает уровень единицы, формируемый элементами И 4 и 5, а также элементом НЕ 7. На вторые входы элементов ИСКЛЮЧАЮЦЕЕ ИЛИ

10 и 12 подается также логическая единица. На вторых входах элементов

ИСКЛЮЧАНМЦЕЕ ИЛИ 8 и 9 уровень логической единицы, формируемый элементом И 5 и элементом НЕ 7, появляется, когда сумма на выходе входного двоичного сумматора 1 равна 16 (10000), 17 (ioooi) .

Ф о р м у л а и з обретения

Одноразрядный десятичный сумматор, содержащий входной двоичный сумматор, первый, второй, третий, четвертый элементы И, элемент ИЛИ и элемент НЕ, причем выход второго разряда входного двоичного сумматора подключен к первому входу первого элемента И и к входу элемента НЕ, выход третьего разряда входного двоичного сумматора подключен к первому входу второго элемента И, выход четвертого разряда входного двоичного сумматора подключен к вторым входам первого и второго элементов И, выход первого элемента И и выход второго элемента И подключены соответственно к первому и к второму входам элемента ИЛИ, выход переноса входного двоичного сумматора подключен к первому входу четвертого элемента И и к третьему входу элемента

ИЛИ, выход элемента НЕ подключен к первому входу третьего элемента И и к второму входу четвертого элемента

И, выход первого разряда входного двоичного сумматора является выходом первого разряда одноразрядного десятичного сумматора, входы переноса, разрядов первого и второго операндов одноразрядного десятичного сумматора соединены соответственно с входом переноса, входами первой и второй групп разрядов входного двоичного сумматора, выход элемента ИЛИ является выходом переноса одноразрядного десятичного сумматора, о т л и ч а— ю шийся тем, что, с целью повышения быстродействия, в него введены пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход второго разряда входного двоичного сумматора подключен к первому входу первого элемента ИСКЛЮЧАЮЦЕЕ ИЛИ, выходы третьего и четвертого разрядов входного двоичного сумматора подключены к первым входам

1464155

Составитель А.Клюев

Редактор Н.Яцола Техред Л.Олийнык Корректор М.Васильева

) Заказ 825/51 Тираж 667 Подписное

K L

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 соответственно второго и третьего элементов ИСКШОЧАКМЦЕЕ ИЛИ, выходы которых подключены к первым входам соответственно четвертого и пятого элементов ИСКЛЮЧАЮЦЕЕ ИЛИ, выход второго элемента И подключен к второму входу третьего элемента И, выход которого подключен к второму . входу четвертого элемента ИСКЛ10ЧАЮЩЕЕ ИЛИ, выход четвертого элемента

И подключен к вторым входам второго и третьего элементов ИСКПЮЧАКЗЦЕЕ ИЛИ, выход элемента ИЛИ подключен к вто5 рым входам первого и пятого элементов ИСКЛНЧАКМЦЕЕ ИЛИ, выходы первого, четвертого и пятого элементов ИСКЛЮЧАК3ЦЕЕ ИЛИ являются выходами соответственно второго, третьего и чет10 вертого разрядов одноразрядного де1сятичного сумматора,