Устройство для сопряжения вычислительной машины с каналами связи

Иллюстрации

Показать всеРеферат

Изобретение относится к области .вычислительной техники и может быть использовано в автоматизированных системах управления. Целью изобретения является сокращение аппаратурных затрат устройства и повышение достоверности контроля поступающей в ЭВМ информации. Устройство содержит коммутатор, преобразователь последовательного кода, два блока формирования задержки, счетчик числа сообщений, формирователь импульса, блок, памяти, триг.гер готовности, триггер ошибки. Устройство работает совместно с ЭВМ. Изобретение позволяет осуществлять контроль количества принимаемых ЭВМ сообщений (тактируемой информации) от каналов связи. При отклонении числа сообщений от заданного, например, под действием помехи в каналах связи устройство выдает сигнал ошибки. В зависимости от решаемых задач ЭВМ имеет возможность производить повторньм прием или или отбраковку получаемых сообщений. 5 ил. S

СВОЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН а) 4 G 06 F 13/00

ВСЕСОЯЯНЦ

047ИТ:- : Ы> йЫИ0

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГННТ СССР (21) 4216845/24-24 (22) 30.03.87 (46) 07.03.89, Бюл. М - 9 (72) В.А. Артемьев, В.П. Гусев и Л.И. Шабунин (53) 681.325 (088.8) (56) Авторское свидетельство СССР

У 433482, кл. С 06 F 13/00, 1974.

Авторское свидетельство СССР

У 703799, кл. С 06 F 13l00, 1977. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

ВЫЧИСЛИТЕЛЪНОЙ МАШИНЫ С КАНАЛАМИ

СВЯЗИ (57) Изобретение относится к области вычислительной техники и может быть использовано в автоматизированных системах управления. Целью изобретения является сокращение аппаратурных затрат устройства и повышение

Изобретение относится к вычислительной технике и может бцть использовано при создании устройств сопряжения вычислительных машин с каналами связи, например, в автоматизированных системах управления (АСУ).

Цель изобретения — сокращение аппаратурных затрат устройства и повы" шение достоверности контроля поступае ющей в ЭВМ информации.

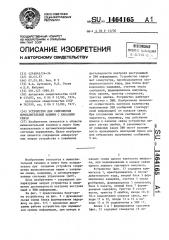

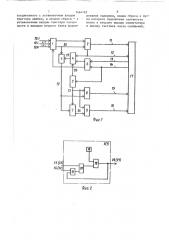

На фиг. 1 представлена блок-схема устройства; иа фиг. 2 - функциональная схема блока формирования задержки; на фиг. 3-5 — временные диаграммы работы устройства при нормальном приеме информации, при потере в

„SUÄÄ 1464165 А 3 достоверности контроля поступающей в ЭВМ информации. Устройство содержит коммутатор, преобразователь последовательного кода, два блока формирования задержки, счетчик числа сообщений, формирователь импульса, блок. памяти, триггер готовности, триггер ошибки. Устройство работает совместно с ЭВМ. Изобретение позволяет осуществлять контроль количества принимаемых ЭВМ сообщений (тактируемой информации) от каналов связи.

При отклонении числа сообщений от заданного, например, под действием помехи в каналах связи устройство выдает сигнал ошибки. В зависимости от решаемых задач ЭВМ имеет возможность производить повторный прием или или отбраковку получаемых сообщений.

5 ил. канале связи одного тактового импульса, при возникновении в канале связи одного лишнего тактового импульса.

Устройство (фиг. 1) содержит коммутатор 1, преобразователь 2 после- довательного кода, второй блок 3 формирования задержки, счетчик 4 числа сообщений, формирователь 5 импульсов, блок 6 памяти, первый блок 7 формирования задержки, триггер 8 готовности, триггер 9 ошибки, входы 10. 110.п подключения каналов связи, выходы 11 и 12, входы 13 и 14 и выходы 15 и 16 подключения к ЭВМ 17.

Блоки 3 и 7 формирования задержки (фиг. 2) содержат генератор 18 им3 146 пульсов„ счетчик 19,, триггер 20 и элемент ИЛИ 21. На чертежах показаны также линии 22-26 входов и выходов блоков и элементов устройства.

Временные диаграммы,фиг.3-5) составлены для следующих условий: в блок 6 памяти записывается код команды, состоящий из адреса соответствующего канала связи и кода числа сообщешяЪ, равного двум; длина одного сообщения равна двум четырехразрядным словам; заштрихованные области соответствуют неопределенному состоянию сигналов; буквой И обозначена область существования достоверной информации на выходе 11.

Устройство работает следующим образом„

ЭВМ 17 устанавливает на входе 13 . код команды и формирует сигнал на

1 входе 14. В состав команды входит код номера коммутируемого канала связи и код, определяющий сколько сообщений должно быть принято as данного канала связи (код числа сообщений). Код команды поступает на

Рход блока 6 памяти. Сигнал с azo1 да 14 поступает на блок 6 для записи кода команды в блоке 6 и на вход формирователя 5, который формирует по линии 23 стартовый сигнал начала цикла приема для блока 7 и установки в исходное состояние триггеров 8 и 9, а также сигнал записи кода числа сообщений н счетчик 4. Поступивший по информационному входу счетчика 4 код числа сообщений запоминается в этом счетчике. Поступивший на вход

23 блока 7 сигнал начала цикла приема устанавливает триггер 20 в состояние разрешения счета для счетчика

19. Последний разблокируется и начинает заполняться импульсами с генератору 18. Величину задержки блоков

3 и 7 определяет время заполнения счетчика 19. Для блока 7 величину задержки выбирают большей времени приема максимально возможного числа сообщений по любому из каналов связи на время, равное или большее величины периода следования тактовых сигналов. При заполнении счетчика 19 (т.е., после окончания формируемого блоком 7 времени задержки) на выходе этого счетчика вырабатывается сигнал который поступает через элемент ИЛИ

21 на вход сброса триг;;-ера 20. При этом сигнал с выхода последнего ус4165

4 танавливает счетчик 19 El исходное состояние и удерживает его в этом состоянии до начала следующего цикла

5 приема сообщений. Сигнал с выхода счетчика 19 блока 7, поступает на второй вход триггера 9.

Если во время формирования временной задержки на вход 22 блока 7 . поступает сигнал установки в исходное состояние, то формирование задержки прекращается, а счетчик 19 удерживается в исходном состоянии до следующего стартового сигнала.

15 Сигналы информации, сопровождаемые тактовыми сигналами, поступают из каналов связи через входы 10 устройства на входы коммутатора 1. Подключение того или иного канала свя20 зи к преобразователю 2 осуществляется кодом номера канаЛа связи, поступающим с выхода блока 6 памяти на вход коммутатора 1.

25 Информационные и тактовые сигналы с выходов коммутатора 1 поступают в преобразователь 2, где осуществляется преобразование последовательного кода в параллельный и пвре3g дача сообщений отдельными словами на выходы 11 в ЭВИ 17. После приема последнего слова каждого сообщения преобразователь 2 выдает на счетчик

4 и на выход 12 сигнал конца сообще35 ния что обеспечивает считывание очеC редного сообщения ЭВИ 17. Сигналы конца сообщения, поступающие на счетик 4, каждый раз уменьшают код в этом счетчике на 1. После приема пос40 леднего сообщения ЭВМ 17 и при совпадении количества принятых по данному каналу сообщений с числом, предварительно записанным в счетчик 4, последний выдает сигнал окончания сообщений на вход 25 блока 3, который работает аналогично блоку 7. Блок 3 задерживает сигнал со счетчика.4 на время, равное или большее периода следования тактовых сигналов, посту50 пающих на вход 26 блока 3. Если за время задержки, формируемое блоком

3, тактовый сигнал не поступает (число сообщений равно заданному), то после истечения этого времени блок

3 вырабатывает сигнал окончания сооб55 щений но данному каналу,, На выходе триггера 8 устанавливается сигнал окончания сообщений, который транслируется на выход 15 устройства.

5 14

Поступление сигнала окончания сообщений с блока 3 на вход 22 блока 7 прекращает формирование задержки блоком 7, и на выходе этого блока сигнал ошибки не вырабатывается.

ЭВМ 17 воспринимает сигнал с выхода

15, как сигнал нормального окончания сообщений, и переходит к приему информации с другого канала связи.

Триггер 20 блока 3 устанавливается в исходное состояние первым тактовым сигналом, поступившим с выхода коммутатора 1 с началом следующего цикла приема информации.

Циклы приема информации повторяются.

Если количество сообщений меньше или больше количества сообщений, соответствующего коду числа сообще ний, записанному в счетчик 4, сигнал окончания сообщений на выход 15 не транслируется. При этом формируется сигнал ошибки на выходе 16 сле дующим образом, Если количество принятых сообщений меньше числа сообщений, определяемого кодом, записанным в счетчик 4, счетчик 4 сигнал окончания сообщений не выдает. В этом случае на вход блока 7 сигнал прекращения формирования задержки с выхода 22 блока 3 не приходит. После окончания времени задержки, формируемой блоком 7, на . вход триггера 9 поступает сигнал, который изменяет состояние этого триггера. С выхода триггера 9 на-выход 16 устройства будет транслиро1 ваться сигнал, который воспринимается ЭВМ 17 как сигнал ошибки. На выход 15 сигнал окончания сообщений транслироваться не будет.

Если количество принятых сообщений больше числа сообщений, определяемого кодом, записанным в счетчик

4, то с поступлением числа сообщений соответствующего коду, записанному в счетчик 4, этот счетчик вырабатывает сигнал окончания сообщений, который поступает на вход 25 блока 3.

Последний формирует задержку этого сигнала. Очередным тактовым сигналом (сообщения еще не закончились) с выхода 26 коммутатора 1, который поступит на вход блока 3, прекращается формирование задержки этим блоком. Сигнал окончания сообщений на, выходе блока 3 не формируется и на входы 22 триггера 8 и блока 7 не

О поступает. Блок 7 не прекращает. формирование времени задержки, по окончании которой сигнал с выхода блока 7 изменяет состояние триггера 9. На выход 16 поступает сигнал ошибки. На выходе 15 сигнал окончания сообщений отсутствует.

Формула изобретения

Устройство для сопряжения вычислительной машины с каналами связи, содержащее преобразователь последовательного кода в параллельный, коммутатор, группа информационных входов которого является группой входов устройства для подключения к информационным линиям связи, а адресный вход соединен с первым выходом блока памяти, первый блок формирования задержки, триггер готовности, выход которого является выходом устройства для подключения к входу готовности вычислительной машины, о т л и ч аю щ е е с я тем, что, с целью сокра" щения аппаратурных затрат устройства, в него введены формирователь импульсов, счетчик числа сообщений, триггер ошибки и второй блок формиЗ0 рования задержки, причем информационный и тактовый входы преобразователя последовательного кода в параллельный соединены соответственно с первым и вторым выходами коммутатора, а информационный и синхронизи35 рующий выходы являются соответствующими выходами устройства для подключения к информационному и синхро низирующему входам вычислительной о

40 машины, информационный и синхронизирующий входы блока памяти и выход триггера ошибки являются соответствующими входами и выходом устройст-, ва для подключения к командному и синхрониэирующему выходам и входу

45 ошибки вычислительной машины, информационный, счетный входы и вход записи счетчика числа сообщений подключены соответственно к вторым выходам преобразователя последовательного кода в параллельный и блока памяти и первому выходу. формирователя импульсов, вход которого соединен с входом устройства для подключения к синхронизирующему выходу вычисли55 тельной машины, а второй выход — с входами сброса триггеров готовности и ошибки и входом пуска первого блока формирования задержки, выходом

7 1464365 8 соединенного с установочным входом рования задержки, входы сброса и пустриггера ошибки, а входом сброса — с ка которого подключены соответст= . установочным входом триггера готов. венно к второму выходу коммутатора ности и выходом второго блока форми- и выходу счетчика числа сообщений,.

Ш.г/Шипр)

Pi (emrnv8l

10ii(4U. о ф)

Qi (A moner и- каличестоа ражядод соодщежж, л - манто. ол-8о сообщений.

6Риг.4

1464165

Составитель В. Вертлиб

Техред A. Кравчук

Корректор С. Шекмар

Редактор Н. Яцола

Заказ 826/52 .Тираж 667 Подписное

ВЯИЖП Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1)3035, Москва, Ж-35, Рауаская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Уигород, ул. Гагарина,101