Конвейерный цифровой умножитель

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительньгх вычислительных систем, таких как суперкомпьютеры, цифровые. фильтрЕ т, процессоры быстрого преобразования Фурье. Цель изобретения - расширение функциональных возможностей за счет декодирования множителя в процессе умножения. Устройство содержит три регистра, комм: татор и сумматор-вычитатель. Новым в устройстве является введение в каждый К-й вычислительный блок цепочки из. К-1 субрегистров, работающей по принципу FIFO, благодаря чему обеспечивается временной сдвиг множителя для поддержки конвейерного режима работы устг ройства, а также декодирование час- . тичных множителей в процессе его функционирования. 1 ил. Ф

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

yg 4 G 06 F 15/332, 7/52

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4274174/24-24 (22) 01.07.87 (46) 07.03.89. Бюл. Р 9 (71) Ленинградский электротехнический институт им. В.И.Ульянова (Ленина) (72) А.И.Водяхо, В.В.Грушин и С.И.Запорожан (53) 681.325(088.8) (56) Коугли П.М. Архитектура конвейерных ЭВМ: Перев. с англ. — М.: Радио и связь, 1985, с. 64.

Авторское свидетельство СССР

N 1206800, кл. G 06 F 15/332, 1984 (54) КОНВЕЙЕРНЫЙ ЦИФРОВОЙ УМНОЖИТЕЛЬ (57) Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизвоИзобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем, таких как суперкомпьютеры, цифровые фильтры, процессоры быстрого преобра" зованиМ Фурье.

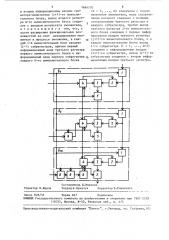

Цель изобретения — расширение функциональных возможностей за счет декодирования множителя в процессе умножения, На чертеже представлена функциональная схема конвейерного цифрового умножителя.

Умножитель содержит пт вычислительных блоков Б,, Б, ..., Б (где m = и

n — - количество разрядов множи„.,Я0„„1464170 А1 дительных вычислительных систем, таких как суперкомпьютеры, цифровые фильтры, процессоры быстрого преобразования Фурье ° Цель изобретения расширение функциональных возможностей за счет декодирования множителя в процессе умножения, Устройство содержит три регистра, коммутатор и сумматор-вычитатель. Новым в устрой- стве является введение в каждый К-й вычислительный блок цепочки иэ. К-1 субрегистров, работающей по принципу

FIFO, благодаря чему обеспечивается временной сдвиг множителя для поддержки конвейерного режима работы уст;. ройства, а также декодирование частичных множителей в процессе его функционирования. 1 ил. теля}, каждый из которых содержит О®®Ь первый регистр 1, коммутатор 2, сум- ф матор — вычитатель 3, второй регистр 4 и третий регистр 5. Кроме того, в каждый К-й (К = 2, ..., m) вычислительный блок входит цепочка из (К-1) субрегистров 6 °

Первый регистр 1 блоков служит для хранения и передачи множителя. Второй регистр 4 блоков служит для декодирования частичных множителей, поступающих на его входы согласно модифицированному алгоритму Бута. ТреЪ . тий регистр 5 блоков служит для хранения частичных произведений. Субрегистры 6 служат для хранения частичных множителей, разрядность которых в соответствии с модифицированным алгоритмом Бута равна 2. и (m = —, где п — разрядность множи2 теля), каждый из которых содержит три регистра, сумматор-вычитатель и коммутатор, причем вход множимого умножителя соединен с информационным вхо40 дом первого регистра первого вычислительного блока, вход синхронизаций умножителя соединен с входами синхронизации первого и второго регистров всех вычислительных блоков, а в кажо

4б дом х-м вычислительном блоке {х — 1, ..., m) выход первого регистра соединен с первым информационным входом коммутатора, выход которого соединен с первым информационным входом

gg сумматора-вычитателя, вьыод которого соединен с информационным входом второго регистра, первый и второй выходы третьего регистра соединены соответственно с управляющими входами 5 коммутатора и сумматора-зычитателя, выходы первого и второго регистров

j-ro вычислительного блока (j = 1, ...

m-1) соединены соответственно с информационным входом первого регистра

3 146417

Конвейерный умножитель работает следующим образом.

Пусть необходимо перемножитель операнды А,, А, ..., А„ и В,, В разрядностью, равной 4. Следовательно„ умножитель содержит два вычислительных блока. Каждый умножиI тель условно разбиваем на два частичHblx множителя ЬЗ H Ь (s = 1, . °, r), 1б причем младшая пара битов Ь постуI пает на регистр 4 блока Б, а стар, шая пара битов Ь29 подается на вход субрегистра б блока Б „ В общ6м случае цепочки субрегистров 6 работают

1 по принципу FIP0 первый вошел — пер(( вый вышел", благодаря чему в К-м вычислительном блоке организуется очередь частичных множителей с дисциплиной PIP0. Множимое поступает на 2О вход регистра 1 первого блока. Умно1 житель управляется синхронно от тактового генератора конвейерной системы.

В регистрах 4 блоков Б, и Б фик- 25

2 сируются инструкции f и f2, определяющие функционирование сумматоравычитателя 3 и коммутатора 2 блоков

Б„ и Б соответственно. При этом в формировании инструкции Л участвует ЗО

5 ( один бит частичного множителя Ь, который поступает на вход регистра 4 блока Б с выхода регистра 4 блока

Б,, в котором он фиксируется вместе ( с инструкцией f

В первом такте работы конвейера умножения в регистры 1 и 4 блока Б< загружаются операнд А.(и инструкция ( соответствующая частичному множителю Ь,, а в субрегистр 6 блока Б заносится частичный множитель Ь . (Таким образом, вычисление первой суммы частичных произведений, соответствующей умножению А, на В<, в первом блоке и декодирование b2 во вто< ром блоке происходит параллельно.

Во втором такте инструкция f операнд А и первая сумма частичных произведений заносятся соответственно в регистр 4 и регистры 1 и 5 блока Б1. Операнд А< пересылается в регистр множимого второго блока, в субрегистр б которого записывается частичный множитель Ь а в регист Ф ре 4 фиксируется инструкция f Следовательно, в первом блоке вычисляется первая сумма частичных произведений для операндов А и В, а во втором блоке вычисляется вторая сумО 4 ма частичных произведений для опер7Гндов А, и В(и формируется инструкция f2 и

В третьем такте операнд А заме-. з щает операнц А, которьм, в свою очередь, выталкивает A . В регистрах 5 блоков Б(и Б запоминаются суммы частичных произведений, полученные с во втором тактовом периоде, при этом на выход умножителя поступает произведение операндов A и В(, Кроме того, инструкции f и Р загружаются

2 в регистры 4 блоков Б и Б соответ< Я ственно, а субрегистр б фиксирует частичный множитель b .

В четвертом такте операнд А,(, очередная сумма частичных произведений

1 и инструкция f заносятся в соответ4 ствующие узлы первого блока. Операнд

А, полученная сумма частичных произведений частичный множитель Ь и ин(Ф струкция 1.2 запоминаются в соответ3 ствующих узлах блока Б,, при.этом на выходе конвейерного умножителя появляется произведение операндов А и В

Таким образом, умножитель выдает произведение двух операнцов в каждом тактовом периоде.

Формула изобретения

Конрейерный цифровой умножитель, содержащий ш вычислительных блоков

5 1464170 6 и вторым информационным входом сум- (К = 2, ..., m) соединены с в:ohio ; матора-вычитателя (j+1)-го вычисли- множителя умножителя, вход спнхронительного блока, выход второго регист- зации которого соединен с входами

pa m-ro вычислительного блока соеди- синхронизации третьего регистра и

5 нен с выходом результата умножителя, каждого субрегистра, третий выход отличающийся тем, что, с третьего регистра j-ro вычислитель-целью расширения функциональных воз- ного блока соединен с первым инфор-: можностей за счет .:декодирования мно- мационным входом третьего регистра жителя в процессе умножения, в каж- 10 (j+1)-ro вычислительного блока, а в дый -й вычислительный блок введено каждом вычислительном блоке выход (i — 1) субрегистров, причем первый 1-го субрегистра (1 = 1, ..., m-2) информационный вход третьего регистра соединен с информационным входом первого вычислительного блока и ин- (1+1)-га субрегистра, выход (i-1)- го формационный вход первого субрегистра 15 субрегистра соединен с вторым инфоркаждого К-го вычислительного блока мационным входом третьего регистра.

Составитель E.Èóðçèíà

Техред А.Кравчук Корректор В.Романенко

Pедактор Н.Яцола

Заказ 826/52 Тираж 667 Подписное

ВНИИПЙ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент". г.ужгород, ул. Гагарина,101