Усилитель считывания на полевых транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике более конкретно к. интегральным схемам памяти, и может быть использовано в интегральных схемах оперативных, буферных и постоянных запоминающих усфоиств статического типа для считывания информации записанной в выбранном элементе памяти . Целью изобретения является повышение быстродействия усилителя считывания. Усилитель считывания содержит шину 1 считывания являюшуюся входом усили1еля считывания , подключенную к первому выводу нагрузочного элемента 2 и к входу инвертора 3 второй вывод нагрузочного элемента и вы хот инвертора объединены и подключены к входу усилительного элемента 4, выход 5 усичительного элемента является выходом СИ1ителя считывания. Максимальный эффект достигается выполнением нагрузочного элемента в виде полевого транзистора. 2 ил. § (Л с:

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Ci 11 С 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСМОМУ СВИДЕТЕЛЬСТВУ

КГЯВРЦ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4284912)24-24 (22) 17.07.87 (46) 07.03,89. Бюл. № 9 (71) Московский институт электронной техники (?2) В. И. Старосельский. В. И. Суэтинов, В. A Братов, Л. H. Кравченко, Ю. Ф. Адамов и А. Н. Сапельников (53) 681.327.6 (088.8) (56) 1по М., Ohmori М., Hirayama M., CiaAs static RAM design and performanceRev. of Electrical Commun. Labs, 1985, v. 33, ¹ i, р. 105 — 114.

Тасимото Т. Монолитное статическое ЗУ с произвольной выборкой на арсениде галлия. — Дэнси гидзюцу, 1984, т. 26, № 13, с. 72- — 76.

„„SU„.„14642 О (54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ (57) Изобретение относится к микроэлектронике, более конкретно к интегральным схемам памяти, и может быть использовано в интегральных схемах оперативных, буферных и пос гоянных запоминающих устройств статического типа для считывания информации, записанной в выбранном элементе памяти. 1)елью изобретения является повышение быстродействия усилителя считывания. Усилитель считывания содержит шину 1 считывания, являющуюся входом усилителя считывания, подключенную к первому выводу нагрузочного элемента 2 и к входу инвертора

3, второй вывод нагрузочного элемента и выхо„l, инвертора объединены н подключены к входу усилительного элемента 4, выход 5 усилительного элемента является выходом усилителя считывания. Максимальный эффект достигается выполнением нагрузочного элемента в виде полевого транзистора.

2 ил.

1464210

Изобретение относится к микроэлектронике, более конкретно к интегральным схемам памяти, и может быть использовано в интегральных схемах оперативных, буферных и постоянных запоминающих устройств (ЗУ) статического типа для считывания информации, записанной в выбранном элементе памяти.

Целью изобретения является повышение быстродействия усилителя считывания.

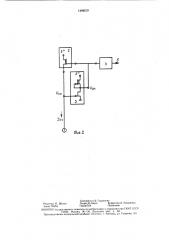

На фиг. 1 представлена структурная схема усилителя считывания ЗУ; на фиг. 2—

; электрическая схема усилителя считывания, выполненного на основе нормально закры1 тых и нормально открытых полевых транзисторов с затвором Шотки (ПТШ).

Усилитель считывания (фиг. 1) содержит шину 1 считывания, являюьцуюся входом усилителя считывания, подключенную к первому выводу нагрузочного элемента 2 и к входу инвертора 3, второй вывод нагрузочного элемента и выход инвертора объединены и подключены к входу усилительного элемен-! та 4, выход 5 усилительного элемента является выходом у силителя считывания.

Максимальный эффект достигается вы полнением нагрузочного элемента в виде, полевого. транзистора (фиг. 2) на примере усилителя считывания на основе нормально закрытых п-канальных ПТШ (напряжение отсечки положительно) и нормально открытых и-канальных ПТШ (напряжение отсечки отрицательно) . Нагрузочный элемент 2 выполнен в виде нормально открытого ПТШ, исток которого является вводом, затвор-выводом, а сток подключен к напряжению питания. Инвертор 3 содержит нормально закрытый инвертирующнй ПТШ, затвор которого является входом, исток подключен к общей шине, а сток является выходом и подключен и обьединенным электродам затвора и истока нагрузочного нормально откры гого ПТШ, сток которого подключен к напряжению питания.

Величина опорного напряжения Uo на выходе инвертора 3 автоматически устанавливается такой, чтобы обеспечить протекание тока считывания I« в цепи истока ПТШ нагрузочпого элемента 2, напряжение затвор- — исток которого составляет U 11„—

Ucai, 2»

Если транзисторы инвертора 3 (инвертирующий и нагрузочный), работающие в пологой области вольтамперной характеристи- 50 ки, являются идеальными источниками тока, не зависящего от напряжения сток — исток, то потенциал 1.;«шины 1 считывания не зависит от тока считывания 1, и определяется напряжением затвор — исток инвертирующего транзистора инвертора 3, соответствующим протеканию через него тока нагрузочного транзистора инвертора 3. В этом случае при изменении тока считывания 1«на величину й1«гютенциал U шины 1 считывания остается постоянным (DU« —— О), а величина опорного напряжения Б,„изменяется, обеспечивая переключение усилительного элемента 4. Изменение опорного напряжения 1 м при изменении тока считывания I« определяется вольтамперной характеристикой транзистора нагрузочного элемента 2

1=1 я (U u — -U, ) 2 =-,Р (Ugn — Ue„UM л(1., - (6 )1, „)/ф, где U,— напряжение отсечки ПТШ 2;

1и, — значения тока считывания, соответствующие состояниям логического нуля и единицы;

P — коэффициент, чропорциональный ширине канала транзистора нагрузочного элемента 2.

Таким образом, необходимая величина перепада напряжения hUon на входе усилительного элемента 4 может быть получена надлежащим выбором ширины канала инвертирующего транзистора инвертора 3. Реальные полевые транзисторы (инверторный и нагрузочный) инвертора 3 не являются идеальными источниками тока, поэтому перепад напряжения 11 на шине 1 считывания остается конечным, однако его величина может быть сделана достаточно малой по сравнению с перепадом опорного напряжения (например, Ь U:ч = 0,1 ALQ ). При заданной величине перепада напряжения на входе усилительного элемента 4 это обеспечивает существенное (например, десятикратное) уменьшение времени задержки между моментом изменения тока считыания 1«и моментом переключения усилительного элемента, так как это время задержки прямо пропорционально перепаду напряжения h L4

Следовательно, наблюдается существенное повышение быстродействия предлагаемого усилителя считывания по сравнению с известным.

Формула изобретения

Усилитель считывания на полевых транзисторах, содержащий нагрузочный элемент, один выход которого является входом усилителя считывания, и усилительный элемент, отличающийся тем, что, с целью повышения быстродействия усилителя считывания, в него введен инвертор, вход которого соединен с шиной считывания, а выход — с вторым выводом нагрузочного элемента и с входом усилительного элемента, выход которого является выходом усилителя считывания.

1464210

Составитель В. Гордонова

Редактор И. Шулла Техред И. Верес Корректор Л. Пилипенко

Заказ 724/54 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, )K — 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101