Формирователь адресных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам на цилиндрических магнитных пленках. Цель изобретения - снижение мощности , потребляемой формирователем. Поставленная цель достигается тем, что формирователь содержит первый и второй ключевые элементы на транзисторах 20. 21 и резисторах 22, 23, развязывающие элементы на диодах 8, 9, 10, 11, 13, 12, нагрузочные элементы на резисторах 16, 17 с соответствующими связями. Транзисторы 6 подключены к двум словарным тинам 1 с помощью развязывающих элементов на диодах 8, 10, 11, поэтому одним транзистором 6 можно задать ток в любую из двух словарных шин 1. В результате уменьщается в два раза количество ключевых элементов первой группы , а вместе с ними и потребляемая формирователем мощность. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„ЯО „„1464211

А1 д> 4 Ei 11 С 8(00

3ИЯЮЗУЯ

ИТИЕ. i .. ;-: -; .;-,,È: i З

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTGPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГНН1 СССР (21) 4276431(24-24 (22) 06.07.87 (46) 07.03.89. Бюл. Х 9 (72) IO. Г. 111агинян и Г. Э. Авакян (53) 681.327.6 (088.8) (56) Вопросы радиоэлектроники, Сер. ЭВТ, вып. 12, 1971, с. 82.

Вопросы радиоэлектроники. Сер. ЭВТ, вып. 9, 1981, с. 5 и б, (54) ФОРМИРОВАТЕЛЬ АДРЕСНЫХ СИГНАЛОВ (57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам на цилиндрических магнитных пленках. Цель изобретения — снижение мощности, потребляемой формирователем. Поставленная цель достигается тем, что формирователь содержит первый и второй ключевые элементы на транзисторах 20, 21 и резисторах 22, 23, развязывающие элементы на диодах 8, 9, 10, 11, 13, 12, нагрузочные элементы на резисторах 16, 17 с соответствующими связями. Транзисторы б подключены к двум словарным шинам 1 с помощью развязывающих элементов на диодах 8, 10, 11, поэтому одним транзистором 6 можно задать ток в любую из двух словарных шин

1, В результате уменьшается в два ра-:а количество ключевых элементов первой группы, а вместе с ними и потребляемая фсрмирователем мощность. 1 ил.

Изобретение относится к вычислительнои технике, в частности к запоминающим устройствам на цилиндрических магнитных пленках.

Цель изобретения -- снижение потребляе5 мой формирователем мощности.

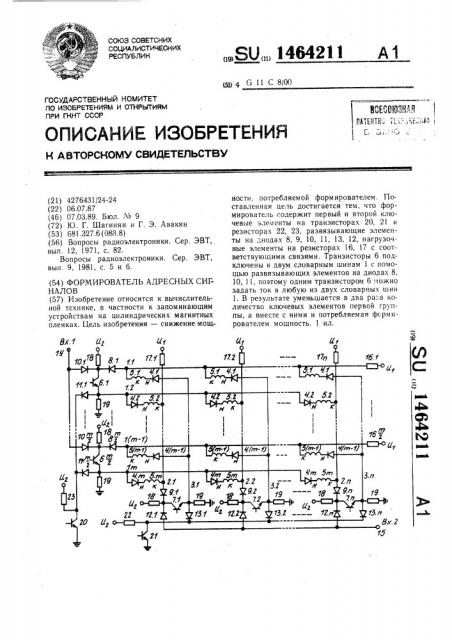

На чертеже представлена электрическая схема предлагаемого формирователя.

Формирователь содержит матрицу, состоящую из словарных шин 1, вторых 2 и первых 3 разрядных шин, элементы выборки, состоящие из развязывающего диода 4 и адресной обмотки 5, ключевые элементы первой и второй групп, выполненные на транзисторах 6 и 7, развязывающие элементы на диодах 8 — 13, второй !4 и первый 15 входы выборки формирователя, две группы нагрузочных элементов на резисторах 16 и 17, токоограничительные резисторы !8 н 19 ключевых элементов групп, первый и второй ключевые элементы на транзисторах 20 и 2! и нагрузочных резисторах 22 и 23.

Формирователь работает следуюпгнм об разом.

Для выоорки адресной обмотки 5, находящейся на пересечении нечетной словар- 25 ной шины 1.1 и первой разрядной шины 3.1, открывают транзистор 20, транзистор 6.1 в первой группе ключевых элементов и транзистор 7.1 во второй группе ключевых элементов, и на вход !5 подается импульс тока, который через диод 12.1, открытый транзистор 7.1, шину 3.1 и диод 4 поступает к адресной обмотке 5, протекая в ней от ее начала к концу, и через шину 1, диод 8.1, открыпгый транзистор 6.1, диод 11.1 и открытый транзистор 20 -à.ìûêàåòñÿ на шину нулевого потенциала.

Для выборки адресной обмотки 5, находящейся на пересечении четной словарной шины 1.2 и второй разрядной шины 2.1, открывают транзистор 21, транзисторы 7.1 во второй группе ключевых элементов и трав- 40 зисторы 6.1 в первой группе ключевых элементов, и на вход 14 подается импульс тока, который через диод 10.1, открытый транзистор 6.1, шину 1.2 и диод 4 поступает к адресной обмотке 5, протекая в ней от начала к 45 концу, и через шину 2.1, диод 9.1, открытый транзистор 7.1, диод !3.1 и открытый транзистор 21, замыкается на шину нулевого потенциала.

Для выборки остальных адресных обмоток 5, соединенных с теми же словарными 59 шинами 1.1 и 1.2, поступают также, открывая вместо транзистора 7.1, соответствую щие транзисторы.

Формула изобретения

Формирователь адресных сигналов, содержащий матрицу, состоящую из словарных и первых разрядных шин, в узлах пересечения которых расположены элементы выборки, каждый из которых состОит из адресной обмотки и развязывавшего диода, катод которого соединен с первым выводом адресной обмотки, вторые выводы адресных обмоток элементов выборки нечетных строк матрицы подключены к соответствующим словарным шинам матрицы формирователя, а аноды диодов элементов выборки нечетных строк матрицы подключены к соответствующим первым разрядным шинам матрицы формирователя, две группы ключевых элементов, каждый из которых состоит из транзистора и двух токоограничительных резисторов, первые выводы которых соединены с эмитгером и коллектором транзистора соответственно., а вторые выводы годключены к шине нулевого потенциала и к шине питанчя формировате ля соответственно, базы транзисторов ключевых элементов первой H второй групп являются адресными входами формирователя первой и второй групп соответственно, первые развязывакнцие элементы, выполненные на диодах, катоды которых соединены с коллекторами транзисторов соответствующи х ключевых элементов второй группы, а аноды объединены и являются первым входом выборки формирователя, эмиттеры транзисторов ключевых элементов первой группы подключены к соответствующим словарным шинам четных строк матрицы формирователя, а эмиттеры транзисторов ключевых элементов второй группы подключены к соответствующим первым разрядным шинам матрицы формирователя, orëè÷ñíâùèélñÿ тем, что, с целью снижения потребляемой формирователем мощности, он содержит вторые разрядные шины, первый и второй ключевые элементы, каждый из которых состоит из транзистора и нагрузочного резистора, первый вывод которого соединен с коллектором, транзистора, эмиттер которого подключен к шине нулевого потенциала формирователя, к шине питания которого подключен второй вывод нагрузочного резистора, две группы нагрузочных элементов на резисторах, первые выводы которых подключены к шине опорного потенциала формирователя, вторые выводы резисторов нагрузочных элементов первой группы соединены с соответствующими вторыми разрядными шинами матрицы формирователя, к которым подключены вторые выводы адресных обмоток соответствующих элементов выборки четных строк матрицы формирователя, аноды развязывающих диодов которых подключены к соответствующим словарным шинам матрицы формирователя, вторые выв !ды резисторов нагрузочных элементов второй группы подключены к соответствующим словарным шинам нечетных строк матрицы фор1464211

Составитель С. Королев

Редактор И. Шулла Техред И. Верес Корректор Н. Король

Заказ 724/54 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ CCCP

113035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский. комбинат «Патент», г. Ужгород, ул. Гагарина. 101 мирователя, с вторых по пятые развязывающие элементы на диодах, катоды диодов вторых развязывающих элементов соединены с коллекторами транзисторов соответствующих ключевых элементов первой группы, а аноды объединены и являются вторым входом выборки формирователя, аноды диодов третьих развязывающих элементов соединены с эмиттерами транзисторов соответствующих ключевых элементов первой группы, а О катоды соединены с коллектором транзистора первого ключевого элемента, база которого является первым адресным входом формирователя, вторым адресным входом которого является база транзистора второго ключевого элемента, коллектор которого соединен с катодами диодов четвертых развязывающих элементов, аноды которых соединены с эмиттерами транзисторов соответствующих ключевых элементов второй группы, коллекторы которых соединены с катодами диодов соответствующих пятых развязывающих элементов, аноды которых подключены к соответствующим вторым разрядным шинам матрицы формирователя, к словарным шинам нечетных строк которой подключены аноды диодов соответствующих шестых развязывающих элементов, катоды которых соединены с коллекторами транзисторов соответствующих ключевых элементов первой группы.