Асинхронный последовательный регистр

Иллюстрации

Показать всеРеферат

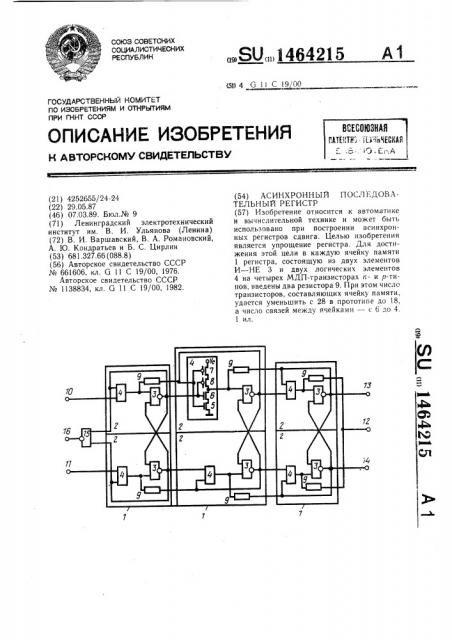

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении асинхронных регистров сдвига. Целью изобретения является упрощение регистра. Для достижения этой цели в каждую ячейку памяти 1 регистра, состоящую из двух элементов И-НЕ 3 и двух логических элементов 4 на четырех МДП-транзисторах пи р-типов, введены два резистора 9. При этом число транзисторов, составляющих ячейку памяти, удается уменьщить с 28 в прототипе до 18, а число связей между ячейками -- с 6 до 4. 1 ил.

COOS СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК,Л0 „„146421 5

А1 (5!! 4 G !! C !9Ц!О

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4252655/24-24 (22) 29.05.87 (46) 07.03.89. Бюл.№ 9 (71) Ленинградский электротехнический институт им. В. И. Ульянова (Ленина) (72) В. И. Варшавский, В. А. Романовский, А. Ю. Кондратьев и Б. С. Цирлин (53) 681,327.66 (088.8) (56) Авторское свидетельство СССР № 661606, кл. G ll С 19/00, 1976.

Авторское свидетельство СССР № 1138834, кл. G 11 С 19/00, 1982. (54) АСИНХРОННЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ РЕГИСТР (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении асинхронных регистров сдвига. Целью изобретения является упрощение регистра. Для достижения этой цели в каждую ячейку памяти

1 регистра, состоящую из двух элементов

И вЂ” HE 3 и двух логических элементов

4 на четырех МДП--ранзисторах r-- и р-типов, введены два резистора 9. При этом числа транзисторов, составляющих ячейку памяти, удается уменьшить с 28 в прототипе до 18, а число связей между ячейками -- c 6 „";о 4.

1 ил.

14642)

Изобретение о п!осит("I к !1 Втом атике

И ВЫ>П!СЛИТЕ>1ЬНО!1 Т("(fl !II<(и МОЖ(Т (><>IT!>

ИСЕ!ОЛЬЗОВИНО I IPH НОСTPO(">H И НСИ Н ХРО!> НЫХ вычислительных устроистн.

Li< JlI> изобрет< HHsl — — уг;рошени(.. асинхронного последовательного регистра.

На чертеже приведена схема асинхронного последовательного регистра.

Регистр содержит ячейки 1 памяти, каждая из KoTophfx состоит из двух симметричных цепочек 2, имею)цих .элемент 10

И---!!Е 3 и логический элемент 4 из МДП гранзисторов п типа 5 и 6 и !)-типа 7 и 8 и элемент связи на резисторе 9. Кроме того, показаны информационнь!е входы 10 или 11 регистра, управляющий вход 12 считывания регистр;., Информационные выходы 13 и 14.

Кроме того, регистр содержит элемент

И--11Е 1, .), I)I>fxo>l, KoTOpoiо являегся управлякнцим выходом 16 запи< .и регистра.

Асинхронный последовательный регистр работает следующим образом.

Состояние ячейки 1 памяти (значение на выходах <:е )лементов 3! соответствует

«10» — в > Icf)!(c 1 33i!HcHII ноль. «01» -- в ячейке 1 за !исаи: единица, «11» — — информация в ячейке 1 :терта, а состояние «00» п процессе работы регистра в ячейке 1 не возникает нз-за перекрестных связей между элементами 3 ее обеих цепочек 2.

Наборы значений на информационных входах 10 и l1 и выходах 13 и 14 регистра также cоответстну!От «10.. — - нулю, «01»вЂ” единице, «11» — отсутствию информации, ЗО а «00» — не используется.

Пусть в кач"..ëü.íîì состоянии информация в регистре отсутствует, т.е. На входах

10 и 11, выходах 13 и 14 и выходах элементов

3 всех ячеек 1 регистра имеется набор значений «11», а на входе l2 зафиксировано значение «)». При этом транзисторы 5 и 6 элеменгов 4 всех ячеек 1 памяти открыты, а транзисторы 7 и 8 -- закрыты, на входах элементов 3 имеется значение «О», что делает указанное состояние реги<. тра устойчивым. <10

На выходе элемента 15, т.е. на управляю- . шем выходе 16 регистра, при этом имеется значение «О».

Источник передает в ре-истр инфоомацию, устанавливая на его информационных

4» входах 10 и 11, например, набор значении

«01». В результате в элементе 4 ОдноЙ из цепочек 2 первой ячейки l памяти оказываются закрыты транзисторы 6 и 7 и на вход соответствую!цего элемента 3 этой цепочки

» >.1

2 II<. pf30H sl !ейки 1 fl3мнти Кре3 тор 9 поступает значение «1» с выходя элемеига 3 соответствун)щей цсг!Очк < 2 следуюшей (1)торой) ячейки 1, I To привод !т к появлению значения >О» (-,«1 элемента 3 д;)иной цепочки 2 первой ячейки памяти 1, которое закрывает транзистор 5 > и открывает транзистор 7 элемента 4 этой цепочки 2. После этого на выходе элемента

15, т.е. унравляюшем выходе 16 регистра, появляется значение « i », что свидетельствует о завер)пении записи информации в его nep8yfo sI>keÉfoi 1 памяти.

Запись информации в каждую следующую яч()йку 1 па is) I"и протекает аналогич-!

fo рассмотренной и завершается появлением значения <О» на выходе соответствующего элемента 3 одной из ее цепочек 2.

После появления на управлякпцем выходе

)6 регистра значения «i» источник может снять информацию с его информационных входов 10 и 11, т,е. установить на них набор значений «11». В результате в элементе

4 упомянутой цепочки 2 первой ячейки памяти оказываются закрыты транзисторы

5 и 8 и, если к этому моменту информация переписапаса из первой ячейки 1 во втору!о, то значение «О > с выхода элемента 3 соответствующей цепочки 2 второй ячейки памяти через резистор 9 поступает на вход элемента 3 данной цепочки 2 первой ячейки 1 и на выходе этого элемента появляется значение «1», которое открывает транзистор 5 и закрь(вает транзистор 7 элемента 4 этой цепочки 2. После этого на выходе элемента 15, т.е. управляюшем выходе

16 регистра, п(гявляется значение «О», что свидетельствует о завершении стирания информации в первой ячейке 1 памяти регистра.

Стирание информации в каждой следующей ячейке 1 памяти протекает аналогично рассмотрен!юму и завершается установкой набора значений «ll» на выходах элементов 3 обеих ее цепочек 2.

После появления на управляюшем выходе 16 регистра значения «О» источник может снова передать в регистр информацию, установив на его информационных входах 10 и 11 наборы значений «01» или

«10». При этом в первую ячейку памяти информация записывается либо после того, как во второй ячейке 1 памяти информация стерта, либо, если ранее записанная во вторую ячейку 1 информация противоположна информации, записываемой в nepI3yfo ячеЙк)> 1

После того, как на информационных выходах 13 и 14 установится набор значений «01» или «)G», т.е. информация записана в последнюю ячейку 1 регистра, приемник может установить на его управляющем входе 12 значение «0», разрешив тем самым стирание информации в последней ячейке 1 регистра.

После того, как в последней ячейке 1 памяти регистра информация будет стерта и на его информационных выходах 13 и 14 установится набор значений «1)», приемник может установить на его управляюшем входе 12 значение