Регистр сдвига

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в многоразрядных устройствах сдвига информации . Целью изобретения является упрощение регистра сдвига, которое позволяет уменьшить площадь, занимаемую регистром, a также снизить потребляемую регистром мощность при интегральном исполнении регистра . Поставленная цель достигается путем использования в регистре одноступенчатых Д-триггеров и последовательно-параллельно-последовательной организации регистра. Сдвиг информации в одноступенчатых D- триггерах осуществляется с частотой, в К раз меныией тактовой (A - разрядность регистра ). В состав регистра, помимо К групп одноступенчатых триггеров 7, по К триггеров в каждой группе, входят две группы 4 к 6 КЗ К двухступенчатых триггеров, каждая для последовательного приема (4) и выдачи (6) информации, К. коммутаторов 8 и группа из К двухступенчатых триггеров 5 для организации параллельного сдвига в группах одноступенчатых триггеров 7. Выигрыш в аппаратурных затратах может быть получен при /(7, a по потребляемой мощности - при /(4. 1 ил. (Л О5 4 o а

СО)ОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК 5ц 4 G 11 С 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

f10 ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4286121/24-24 (22) 17.07.87 (46) 07.03.89. Бюл, № 9 (72) М. В. Алюшин, А, В. Алюшин, В, Н. Филатов, С. И. Назаров и Я. Я. Петричкович (53) 681.327.66 (088.8) (56) Алексенко А. Г,, Шагурин И. И. Микросхемотехника. -- М.: Радио и связь, !982, с. 235, рис. 6.9.

Соловьев Г. Н. Арифметические устройства ЭВМ. — М.: Энергия, 978, с. 78, рис. 4.3. (54) РЕГИСТР СДВИГА (57) Изобретение относится к вычислительной технике и может быть использовано в многоразрядных устройствах сдвига информации. Целью изобретения является упрощение регистра сдвига, которое позволяет уменьшить площадь, занимаемую регистром,,SU„„1464216. A 1 а также снизить потребляемую регистром мощность при интегральном исполнении регистра. Поставленная цель достигается путем использования в регистре одноступенчатых

В-триггеров и последовательно-параллельно-последовательной организации регистра.

Сдвиг информации в одноступенчатых Dтриггерах осуществляется с частотой, и К раз меньшей тактовой (К вЂ” разрядность регистра). В состав регистра, помимо К групп одноступенчатых триггеров 7, по К триггеров в каждой группе, входят две группы 4 и 6 из К двухступенчатых триггеров, каждая для последовательного приема (4) и выдачи (6) информации, К коммутаторов 8 и группа из К двухступенчатых триггеров 5 для организации параллельного сдвига в группах одноступенчатых триггеров 7. Выигрыш в аппаратурных затратах может быть получен при К)7, а по потребляемой мощности — при K)4. 1 ил.

1464216

Изобретение относится к вычислительной технике и может быть использовано в многоразрядных устройствах сдвига информации.

Целью изобретения является упрощение регистра сдвига, которое позволяет уменьшить площадь, занимаемую регистром, а также снизить потребляемую регистром мощность при интегральном исполнении регистра.

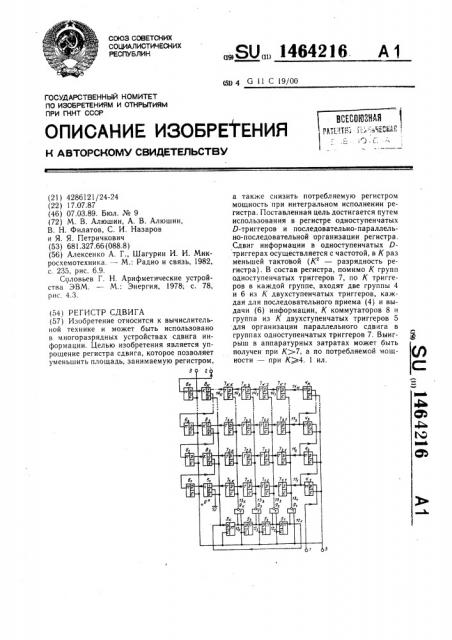

На чертеже показана схема 16-разрядного регистра.

На схеме обозначены информационные вход 1 и выход 2 регистра, вход 3 синхронизации регистра, первая 4, вторая 5 и третья 6 группы по К двухступенчатых D-триггеров в каждой (К=4, 5, 6 ..., i(— разрядность регистра) К групп 7 --7к по К одноступенчатых D-триггеров в каждой, К коммутаторов 8, К элементов ИЛИ-НЕ 9, шина 10 нулевого потенциала (источник сигнала логический О), выходы 11 трип еров 4, выходы 12 триггеров 5, выходы 13 элементов ИЛИНЕ 9, выходы 14 триггеров 7.

Регистр работает следующим образом (работа рассмотрена для случая К==4) .

В начальном состоянии триггеры 5 второй группы, которые образуют кольцевой регистр, устанавливаются в состояние «1», кроме первого триггера 5ь который устанавливается в состояние «О».

По первому тактовому сигналу (С) входные данные записываются в триггер 41 и появляются на его выходе 11i после окончания синхросигнала (по срезу) . В это время сигнал

«О» сдвигается в кольцевом регистре в триггер 5к и появляется на его выходе 12к.

По второму тактоьому сигналу второй разряд входных данных записывается в триггер 4i, информация из которого переписывается в триггер 42 и появляется на его выходе 11>. В это время сигнал «О» в кольцевом регистре появляется на выходе 12 .

Аналоги иным образом по третьему и четвертому тактовым импульсам входные данные записываются в триггеры первой группы и появляются на их выходах 11i, 112, 11,з н 11к.

За это время сигнал «О» в кольцевом регистре доходит до триггера 5i и появляется на его выходе 12, По сигналу с выхода 12 и синхроимпульсу (С) на выходе элемента 91 появляется сигнал записи, по которому информация с триггеров 4i — Кк переписывается в первые 0-триггеры каждой из

К групп — 7i,1, 72,i, 7;,:.i и 7„ i и появляется на их выходах.

За четыре следующие синхроимпульса в триггеры 4г — 4к записываются следующие четыре разряда информации. 3а эти такты (5 — 8) сигнал «0» проходит по кольцевому регистру и вновь формирует сигнал записи на элементе 9 .

Информация из триггеров 7 ..i — 7 . первой ступени переписывается во вторую ступень — триггеры 7» )— --- 7 по сигналу записи, который формируется элементом 9 по тактовому импульсу С (пауза между сигналами 7 и 8).

По,сигналу «О» с выхода триггера 5З и сигналу С формируется сигнал записи в третью ступень — триггеры 7i 3 — 7

10 Аналогичным образом по сигналу «О» с выхода триггера Б к с помощью элемента 9к формируется сигнал записи, по которому информация появляется на выходах триггеров четвертой ступени.

Параллельно входная информация записывается через каждые четыре такта в однотактные триггеры 7 первой ступени.

Когда сигнал «О» кольцевого регистра Воявляется на выходах 12 коммутаторы

81 — 8к соединяют выходы последнего яруса

20 триггеров 7ьк — 7к.к с входами D-триггеров

6 — бк. При этом первый разряд появляется на выходе 2 регистра по срезу синхроимпульса.

После этого триггеры 61 — бк пересоединяются последовательно и информация выводится на выход 2 последовательно.

Для уменьшения потребляемой мощности на вход триггера 6«подается сигнал «О», что позволяет исключить переключение триггеров третьей группы при отсутствии на них 0 полезной информации.

Таким образом, предлагаемый сдвиговый регистр осуществляет задержку входной информации на 16 тактов. Аналогичным образом реализуется регистр в случае разрядности К .

По сравнению с известным, для реализации которого требуется 2К одноступенчатых D-триггеров, предлагаемый регистр реализуется на основе ЗК двухступенчатых триггеров, К одноступенчатых триггеров, К коммутаторов и К элементов ИЛИ-НЕ (по слож40 ности две последние группы элементов эквиваленты К одноступенчатым триггерам), т. е, на К (К+7) одноступенчатых триггерах. Поэтому выигрыш в аппаратурных затратах составляет (при К)7) 2К/(К+7)

45 раз. Во столько же раз сокращается площадь БИС при интегральном исполнении регистра.

При работе с тактовой частотой F,мощность, потребляемая известным регистром (для КМДП реализации), Г=2си F K, где С вЂ” перезаряжаемая емкость при переключении одного простого D-тригегера;

U — напряжение питания.

Для предлагаемого регистра потребляе55 мая мощность равна 7KCU F, так как все

К одноступенчатых триггеров переключается с частотой FjK. Выигрыш в потребляемой мощности (при К)4) составляет 2К/7.

1464216 д

Формула изобретения

Составитель A. Дерюгин

Редактор Н. Бобкова Техред И. Верес Корректор И. Муска

Заказ 724/54 Тираж 558 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, ж — 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 10!

Регистр сдвига, содержащий три группы по К двухступенчатых D-триггеров, К=4, 5, 6, ..., К вЂ” разрядность регистра, причем в первой группе D axîoä i-го двухступенчатого

В-триггера, 1=2, К соединен с выходом (i — 1) -го двухступенчатого триггера, а

D-вход первого двухступенчатого D-триггера является информационным входом регистра, в второй группе D-вход /-ro двухступенчатого D-триггера, г =Г тт — Г, соединен с выходом (i+1)-го двухступенчатого 0триггера, выход К-го двухступенчатого D. триггера третьей группы является информационным выходом регистра, С-входы каждого двухступенчатого D-триггера каждой группы являются синхронизирую1цим входом регистра, отличающийся тем, что, с целью упрощения регистра, он содержит К групп по К одноступенчатых D-триггеров, К коммутаторов и К элементов ИЛИ-НЕ, выходы которых соединены с С-входами соответствующих одноступенчатых D-триггеров каждой группы, а первые и вторые входы—

4 с выходами и С-входами соответствующих двухступенчатых D-триггеров второй группы, выход 1-ro одноступенчатого D-триггера, i=1, К вЂ” Г в каждой группе соединены с

D-входами (i+1) -ro одноступенчатого 0триггера, D-вход первого одноступенчатого

D-триггера каждой группы соединен с выходом соответствующего двухступенчатого

D-триггера первой группы, а выход последнего одноступенчатого D-триггера каждой группы соединен с первым информационным входом соответствующего коммутатора, второй информационный вход i-fo коммутатора, 1=2,К соединен с выходом (/ — 1)-го двухступенчатого D-триггера третьей группы, второй информационный вход первого коммутатора соединен с шиной нулевого потенциала регистра сдвига, а выходы коммутаторов соединены с D-входами соответствующих двухступенчатых D-триггеров третьей группы, выход первого двулступенча

20 того D-триггера второй группы i. динен

D-входом К-го двухступенчатого -триггс ра данной группы и с управляю.!i! Mè вхс дами коммутаторов.