Следящий частотомер

Иллюстрации

Показать всеРеферат

Изобретение относится к технике автоматического измерения частоты. Цель изобретения - повьппение быстродействия . Для достижения цели в следяший частотомер введены первьй и второй регистры 5, 6, сумматор кодов 7, третий регистр 8 и элемент задержки 9, Следящий частотомер также содержит генератор 1 эталонной частоты , делитель 2 частоты, формирователь 3. адпульх1ов и управляемый делитель 4 частоты. Частотомер может быть использован в быстродействуюпи« измерительных системах. 2 ил.

СОЮЗ СОВЕТСКИХ

СОМИАЛИСТИЧЕСНИХ

РЕС(1УБЛИН (191 (111 (511 4 С 01 К 23/10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ HOMHTET

ПО ИЗОБРЕТЕНИЯМ И ОП<РЫТИЯМ

ПРИ ГННТ СССР (21) 4230737/24-21 (22) 15, 04. 87 (46) l 5. 03. 89. Бюл. М 1 0 (72) Ф,N.Андреев и В.В.Райда (53) 621.317.75(088.8) (56) Авторское свидетельство СССР

У 940082, кл. G 01 R 23/02, 1982.

Авторское свидетельство СССР

Р 1210104, кл. С 01 R 23/10, 1986, (54) СЛЕДЯЩИЙ ЧАСТОТОМЕР (57) Изобретение относится к технике автоматического измерения частоты.

Цель изобретения — говышение быстродействия. Для достижения цели в следящий частотомер введены первый и второй регистры 5, 6, сумматор кодов 7, третий регистр 8 и элемент sa. держки 9. Следящий частотомер также содержит генератор 1 эталонной частоты, делитель 2 частоты, формирователь .3 импульсов и управляемый делитель 4 частоты. Частотомер может быть использован в быстродействующих измерительных системах. 2 ил.

1465804

Изобретение относится к измерительной технике и предназначено для автоматического измерения частоты с выдачей результата измерения в цифровом коде.

Цель изобретения — повышение быстродействия.

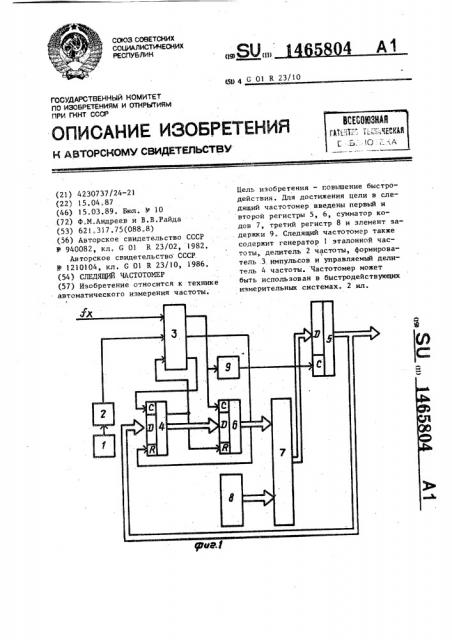

На фиг.1 приведена функциональная схема следящего частотомера; на фиг.2 приведены эпюры, поясняющие работу устройства при различных значениях измеряемых частот.

Следящий частотомер содержит генератор 1 эталонной частоты, делитель 2 частоты, формирователь 3 импульсов, управляемый делитель 4 час тоты, первый 5 и второй 6 регистры, сумматор 7 кодов, третий регистр 8 и элемент 9 задержки.

Выход генератора 1 эталонной частоты соединен с входом делителя 2 частоты, выход которого .соединен с третьим входом формирователя 3 импульсов, первый вход которого явля- 25 ется входом устройства, второй вход формирователя 3 импульсов соединен с первым выходом управляемого делителя 4 частоты, вход сброса которого соединен с третьим выходом формирователя 3 импульсов, первый выход которого соединен через элемент 9 задержки с тактовыми входами регистров 5 и 6. Выходы регистра 5 являются выходом устройства и соединены соответственно с информационными входами управляемого делителя 4 частоты, второй выход которого соединен с ин, формационными входами второго регистра 6, вход сброса которого соединен с первым выходом управляемого делителя 4 частоты. Выход регистра 6 соединен с первым входом сумматора

7"кодов, второй вход которого соединен с выходом регистра 8, выходы сумматора 7 кодов соединены с информационными входами регистра 5.

Устройство работает следующим образом.

В исходном состоянии код на вы- 50 ходе регистра 5 М„ = 00...0. Двоичный код на выходах регистра 6 в исходном состоянии N =011...1. На втором выходе управляемого делителя 4 частоты код L,=00...0. В третьем ре- 55 гистре 8 записан двоичный код М, десятичный эквивалент которого М

=(2 +1), где R — разрядность регистра 5. Так при R = 3; 4; 5 числовое значение двоичного кода М = 9; 17;

31. Сумматор 7 кодов суммирует два двоичных кода N, и М, в результате в исходном состоянии на его выходах сформирован код М . Данный сигнал поступает на вход переноса в младшем разряде первого слагаемого сумматора 7 кодов. Когда R 3, значение кода М „ = N, (+) M=0111+1001=0001, где Š— означает операцию суммирования двоичных кодов.

Генератор 1 эталонной частоты формирует последовательность импульсов высокостабильной эталонной частоты f, которая поступает на вход делителя 2 частоты (фиг.2а).

Частота:E т на выходе делителя 2 частоты соответствует номинальному зна-. чению измеряемой частоты f„ последовательности импульсов, поступающих на вход устройства. Последовательность импульсов частоты следования и . (фиг.2а) с выхода делителя 2 частоты поступает на третий вход формирователя 3 импульсов, который до прихода первого импульса измеряемой частоты К блокирует прохождение импульсов частоты Й на его второй выход и далее на счетный вход управляемого делителя 4 частоты. При этом на 9-входы управляемого делителя 4 частоты подан двоичный код N =М с выходов регистра 5. Управляемйй делитель 4 частоты с переменным коэффициентом деления выполняет функ1 цию деления частоты f следования импульсов, поступающих на его тактовый вход (фиг.2в,е,и), а двоичный код на его втором выходе характеризует текущее значение отношения двух

1 частот Е. и f„s момент прихода импульсного сигнала на вход установки в "0" управляемого делителя 4 частоты. В фиксированные моменты времени коэффициент деления

К управляемого делителя 4 частоты определяется его разрядностью и двоPl ичным кодом íà его D-входах, К;=2—

N, .где и — разрядность управляемого.

1 1 делителя 4 частоты; NÄ вЂ” двоичный

h код на В-входах; 1=1,2,..., (2 -1) номер периода T измеряемой частоты /4

При поступлении первого импульса

1измеряемой частоты f„ в момент вре мени и (фиг,2б,д,з) формирователь

1465804

С поступлением на вход устройства второго импульса последовательности измеряемой частоты f â момент (фиг 2r,ж,к) по импульсному сигналу с первого выхода формирователя

3 импульсов, поступающему на такто« вый вход регистра 6, двоичный код с второго выхода управляемого

1 делителя 4 частоты устанавливается во втором регистре 6, а по импульсному сигналу, поступающему с третьего выхода формирователя 3 импульсов с задержкой на вход установки в состояние "0" управляемого делителя 4 частоты, происходит установка в исходное состояние управляемого делителя 4 частоты. Десятичный эквивалент двоичного кода L< определяет ,отношение частот f и f„ двух им пульсный последовательностей, т.е.

1., = f> /fz, откуда следует, что значение измеряемой частоты f„ может быть выражено как к т /1 ° (2) 3 импульсов на первом и третьем выходах формирует импульсные сигналы заданной длительности. Снимается запрет на прохождение импульсной по5 следовательности с третьего входа на второй выход формирователя 3 импульсов. Импульсный сигнал с первого выхода поступает на вход элемента 9 задержки. и на тактовый вход второго 10 регистра 6, в котором записывается двоичный код L с вторых выходов управляемого делителя 4 частоты. При этом значение двоичного кода N на выходах регистра 6 не изменяется, 16 так как значение двоичного кода L, на входах регистра 6 соответствует его исходному состоянию. Через временной интервал Г, равный времени формирования результата суммирования . 20 кодов в сумматоре 7 кодов, импульсный сигнал с выхода элемента 9 задержки поступает на тактовый вход регистра 5, в котором устанавливается двоичный код M с выходов суммаз.о тора 7 кодов. Импульсный сигнал с третьего выхода формирователя 3 импульсов поступает на вход установки в "0" управляемого делителя 4 частоты, который находится в исходном З0 состоянии. Последовательность импульI сов частоты следования Й поступает на тактовый вход управляемого делителя 4 частоты, на D-входы которого подается двоичный код N =М =00...01.

На первом выходе управляемого делителя 4 частоты формируются импульсные сигналы, частота следования которых f11 определяется выражением й„ =-Х N,/2". Если .значение измеря- 40 емой частоты Е„ входной импульсной последовательности больше значения частоты следования импульсов Е, то " момент прихода очередного импульса частоты Й„ на первый вход формирова- 45

rests 3 импульсов наступит раньше,чем момент появления импульсного сигнала иа первом выходе управляемого делителя 4 частоты. В этом случае с мо- . мента прихода первого импульса из- 50 . меряемой частоты f управляемый де.литель 4 частоты подсчитывает число периодов следования импульсов часто-! ты f > за первый период Т„ следования импульсов частоты й„, т.е. Т„ =

= К,Т .„, где N, — число импульсов чаI стоты Е, подсчитанное за период Т„;

Т вЂ” период следования импульсов на втором выходе формирователя 3 импульсов. Число N< также характеризует отношение двух частот следования импульсов Й„и f т.е, Ы, Г /f „.

Так как изменение состояния:iBpBp ляемого делителя 4 частоты происходит при начальном значении коэффициента деления К 1, а не при К = О, то выражение коэффициента деления управляемого делителя 4 частоты К -1

4;

= M — N о или

% %. Ф Ф

К = (М. +1)N; КM, — N где 11 - десятичный эквивалент текущего значения двоичного кода на выходах регистра 5;

М,:= L, — емкость регистра 5 или управляемого делителя 4 частоты, М

L = 2

R = и, .

R — разрядность управляемого делителя 4 частоты и регистра 5 соответственно.

Десятичный эквивалент двоичного кода N„на выходах первого регистра

5 соответствует измеряемой частоте только в том случае, когда выполняется равенство измеряемой частоты входной последовательности и частоты следования импульсов f с первого выхода управляемого делителя 4

1465804, частоты. При этом значение частоты

f следования импульсов может быть о1Рределено как f Е . /К„, где К " установленный коэффициент деления управляемого делителя 4 частоты в случае равенства f> =f . Учитывая выражение (j) коэффициент деления К„ может быть выражен как К„ = М, — NÄ, Ма значение частоты f следования импульсов на первом выходе управляе( мого делителя 4 частоты как Учитывая условие, прч котором f„= (1

=f+ из выражений (2) и (3) f „/?, эт /(М1 » )

Откуда

К„= (М, — т. ;). (4)

Из выражения (4) следует, что для установки соответствия между значением измеряемой частоты f„ входной ( ймпульсной последовательности и зна-! чением двоичного кода N» на выходах регистра 5 необходимо за период измеряемой частоты f.> определить значение двоичного кода L и полученное значение вычесть из значения

1 двоичного кода М<, В устройстве операция вычитания заменена операцией сложения прямого кода М,, установленного постоянно в регистре 8, значение которого определяется выбранной для устройства разрядностью регистра 5, и обратного кода 1., поступающего на сумматор 7 кодов с инверсных выходов триггеров, входящих в состав регистра 6. Суммирование ( кодов в сумматоре 7 кодов производится с учетом сигнала переполнения ( результата суммирования. Сигнал переполнения поступает на вход переноса в младшем разряде первого слагаемого сумматора 7 кодов. Двоичный код на выходе сумматора кодов 7.равен

И„= М - М,97.,, Через временной интервал, l.lc< Ä с выхода элемента 9 задержки импульс ный сигнал поступает на тактовый вход первого регистра 5 и последний

; устанавливается в состояние, при котором на его выходах устанавливает= ся двоичный код N значение которого соответствует измеряемой частоте fÄ входной импульсной после довательности.

20

40

Если значение измеряемой частоты входной последовательности ока» жется меньше частоты следования

1 импульсных сигналов на первом выходе управляемого делителя 4 частоты, т.е. f » (f в момент времени (фиг.2з-к}, то на второй вход формирователя 3 импульсов импульсный сигнал поступает реньше, чем очередной импульсный сигнал на первом входе формирователя 3 импульсов. В этом случае импульсный сигнал с первого выхода управляемого делителя 4 частоты поступает на вход установки в состояние "0" регистра 6 и устанавливает его в исходное состояние. Одновременно с этим данный импульсный сигнал поступает на второй вход формирователя 3 импульсов, в котором при этом запрещается прохождение импульсов последовательности частоты

f,,на второй выход формирователя 3 зт импульсов. В момент формирования импульсного сигнала на первом выходе управляемого делителя 4 частоты значение двоичного кода L< на его вторых выходах равно нулю, т.е. Ь, =

= 00...0. В результате этого до прихода очередного импульса измеряемой частоты Г значение двоичного кода х на выходах регистра 6, а следовательно, и на D-входах первого регистра 5, соответствует исходному состоянию. Первый импульс последовательности измеряемой частоты f„, момент времени t (фиг.2 з-к), с перваго выхода формйрователя 3 импульсов поступает на тактовый вход второго регистра б и на вход элемента

9 задержки. Одновременно с этим импульсный сигнал с третьего выхода формирователя 3 импульсов подтверждает исходное состояние управляемого делителя 4 частоты. Через с> значение двоичного кода на выходах сумматора кодов 7 устанавливается в первом регистре 5. При этом в формирователе 3 импульсов снимается запрет на поступление импульсов поI следовательности частоты Е на его второй выход и далее на тактовый вход управляемого делителя 4 частоты. Управляемый делитель 4 частоты, 5 как и в предыдущем случае, подсчитывает число периодов Т последоваI тельности импульсов частоты Х до момента .прихода очередного импульса

7 14658 последовательности f.„, по которому двоичный код с вторым выходов управ- ляемого делителя 4 частоты устанавливается во втором регистре 6 в

5 момент времени t< - t> (фиг.2и). В .результате суммирования с учетом сигнала переполнения на выходах сумматора кодов 7 устанавливается двоичный код N„, характеризующий величи- 10 ну измеряемой частоты f<. Двоичный код в регистре 5 определяет коэффициент деления управляемого делителя

4 частоты, при котором выполняется условие f„ = f (момент времени 15 фиг. 2к).

Таким образом, в обоих случаях за период входного сигнала определяется отношение между опорной и изме 20 ряемой частотами, а повышение быстродействия обусловлено тем, что общее время переходного процесса до вхож- . дения в режим слежения не превышает двух периодов входного сигнала. - 25

Формула и э о б р е т е н и я

Следящий частотомер, содержащий генератор эталонной частоты, выход которого соединен с входом делителя частоты, формирователь импульсов, Гпервый вход которого является входом следящего частотомера, второй вход

04 8 формирователя импульсов соединен с первым выходом управляемого делителя частоты, а третий выход соединен с входом сброса управляемого делителя частоты, отличающийся тем, что, с целью повышения быстродействия, в него дополнительно введены первый и второй регистры, сумматор кодов, третий регистр.и элемент задержки, вход которого .соединен с первым выходом формирователя импульсов, а выход - с тактовьм входом первого регистра, выходы которого являются выходом устройства и соединены соответственно с информационными входами управляемого делителя частоты, второй выход которого соединен с информационными входами второго ре. гистра, тактовый вход и вход сброса которого соединены с первым выходом формирователя импульсов и первым выходом управляемого делителя частоты, при этом выход второго регистра соединен с первым входом сумматора ко дов, второй вход которого соединен с выходом третьего регистра, а выходы. . сумматора кодов соединены с информационными входами первого регистра, 39 причем выход делителя частоты соединен с третьим входщн формирователя импуЛьсов, второй выход которого соединен с тактовым входом управляемого делителя частоты.

1465804

Я

Составитель E.Ìèíêèí

Редакто р Л.Пчолинская Техред А. Кравчук Коррек тор С, Черни

Заказ 941/46 Тираж 711 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГЕНТ СС и ГЕНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент,, r. Укг р и, у

It

У о о л. Гагарина, 101