Устройство для измерения серии временных интервалов

Иллюстрации

Показать всеРеферат

Изобретение относится к измери тельной технике и позволяет уменьИНф . Синхро шить фпюктуационную погрешность.Устройство содержит запоминающее устройство 9 и счетчик 10 адреса. Введение бинарного квантователя 3, блока 4 управления , D-триггера 5, преобразователя 6 код-временной интервал, корректора 7 кода, блока 8 формирования приращения и блока 11 регистрации позволяет измерение проводить в следящем режиме в N каналах измерения. Кроме того, наличие анализа кодов позволяет восстановить работу устройства при наличии сбоя/В описании приведены примеры реализации блока 4 управления , корректора 7 кода и блока 8 формирования приращения. 3 з.п. ф-лы, 5 ил. с б (Л 4 О5 СП 00

СОЮЗ COBETCHHX

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБ ЛИН

„,SU„„14658

1Я1 с1 G 04 F 1О/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ЮИ,/303

И".Л"

Г.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flQ ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ .СССР (21) 4191902/24-21 (22) 26.11.86 (46) 15.03.89. Вюл. № 10 (71.) Новгородский политехнический институт (72) И.О.Ларин, С,A .Гурьянов, П.В.Шарапов и А.Н.Маров (53) 681;325,3(088.8) (56) Авторское свидетель ство СССР № 546845, кл. G 04 F 10/04, 1977.

Авторское свидетельство. СССР

¹ 699485, кл С 04 F 10/04, 1.979. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СЕРИИ

ВРЕМЕННЫХ ИНТЕРВАЛОВ (57) Изобретение относится к измерительной технике и позволяет уменьшить флюктуационную погрешность.Устройство содержит з апоминающее устройство 9 и счетчик 10 адреса. Введение бинарного квантователя 3, блока 4 управления, D-триггера 5, преобразователя 6 код-временной интервал, корректора 7 кода, блока 8 формирования приращения и блока 1I регистрации позволяет измерение проводить в следяшем режиме в Н каналах измерения.

Кроме того, наличие анализа кодов позволяет восстановить работу устройс1ва при наличии сбоя. В описании приведены примеры реализации блока 4 управления, корректора 7 кода и блока . 8 формирования приращения. 3 з.п. ф-лы, 5 ил.

1465870 .

Изобретение относится к измерительной технике.

Цель изобретения — уменьшение флюктуационной погрешности.

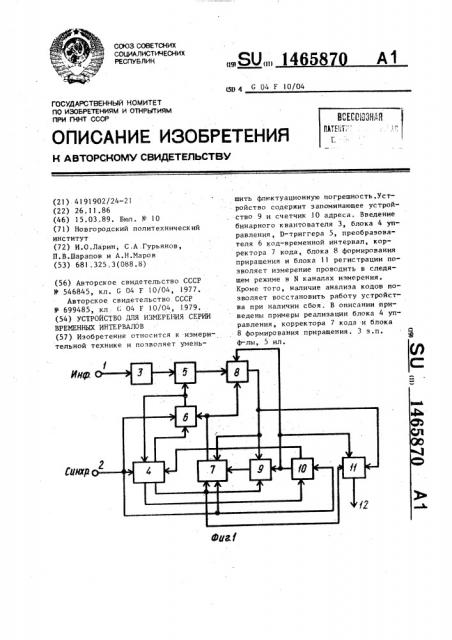

На фиг.1 приведена структурная схема устройства, на фиг.2 — схема блока управления; на фиг.3 †схема корректора кода; на фиг.4 — схема блока формирования приращения; на фиг.5 — временная диаграмма работы устройства.

Устройство содержит информационный вход 1, вход 2 синхронизации, бинарный квантователь 3,, блок 4 управления, D-триггер 5, преобразователь код — временной интервал 6, корректор кода 7, блок формирования приращения 8, запоминающее устройство

9, счетчик адреса 10, блок регистрации 11 и выходную информационную шину 12 устройства.

1О

Вход синхронизации 2 устройства соединен с входом "Запуск блока управлен ения 4 входом "Сброс" счетчика адреса 10, входом "Сброс" преобр;— зователя код-временной интервал 6 и с входом "Сброс" корректора кода 7.

Информационный вход 1 устройства подключен ко входу бинарного квантователя 3, выход которого соединен с информационным входом D-триггера 5, прямой выход которого подключен к первому входу управления блока формирования приращения 8, выход которого соединен с первым входом корректора кода 7, с информационным входом блока регистрации 11 и с информационным входом запоминающего устройства 9, выход которого подключен ко второму входу корректора кода 7, выход которого соединен с информационными входами блока формирования приращений 8 и преобразователя код-интервал 6, вы- 45 ход которого подключен к входу синхронизации Р-триггера 5 и входу

"Строб" блока управления 4, первый выход которого соединен со счетным адреса 10, выходы всех разрядов которого подключены к адресным входам блока регистрации 11 и запоминающего устройства 9, вход

" 3àïèñü" которого соединен со входом

"Запись" корректора кода 7, входом

"Запись" блока регистрации 11 и вторым выходом блока управления 4, третий выход которого подключен ко входу "Запись" преобразователя код— временной интервал 6, а второй вход управления блока формирования прира щения 8 соединен с выходом младшего разряда счетчика адреса 10 выход переполнения которого подключен ко входу "Сброс" блока управления 4, а выход блока регистрации 11 является выходом устройства.

Блок управления 4 содержит триггер 13, элемент И 14, элементы задержки 15 и 1 6,,элемент ИЛИ 17 и элемент задержки 18. Вход "Сброс" блока управления соединен с входом установки в ноль триггера 13 вход установки в. единицу которого подключен к входу Запуск" блока управления и входу элемента. ИЛИ 17, второй вход которого соединен с первым выходом блока управления и через элемент задержки 16 подключен ко второму выходу блока управления, который через элемент задержки 15 соединен с выходом элемента И 14, первый вход которого подключен к прямому выходу триггера 13, а второй вход соединен с входом Строб" блока управления, третий выход которого через элемент задержки 18 подключен к выходу элемента ИЛИ 17.

Коррек.тор кода 7 содержит вычитатель 19, регистр 20, блоки сравнения кодов 21 и 22, сумматоры 23 и

24 и коммутатор 25, Первый информационный вход корректора кодов соединен с информационными входами регистра 20, входы записи информации и обнуления которого подключены соответственно к входам "Запись" и "Сброс" корректора кодов, второй информационный вход которого соединен с первым информационным входом первого числа коммутатора 25 и входом первого числа вычитателя 19, вход второго числа которого подключен к информационному выходу регистра 20 и первым информационным входам сумматоров 23 и 24, на вторые входы которых поданы соответственно коды первой Кl и второй К2 констант, а выходы сумматоров 23 и 24 подключены соответственно ко второму и третьему информационным входам второго и третьего чисел коммутатора

25, первый и второй адресные входы которого соединены с выходами блока сравнения 21 и 22 cooòíåòñòâåíío, первые информационные входы которых объединены и подключены к информа1465870 ционным выходам вычитателя 19, а на вторые входы блоков сравнения 21 и

22 поданы соответственно коды первой Kl и второй К2 констант

Блок формирования приращения 8 содержит элемент ИСКЛЮЧАЮШЕЕ ИЛИ 26 и сумматор — вычитатель 27.

Первый вход управления блока формирования приращений соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

26, второй вход которого подключен к второму управляющему входу блока формирования прирашения, а выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 соединен с входом управления операцией сумматора-вычитателя 27, информационный вход которого подключен к информационному входу блока формирования приращения, информационный выход которого соединен с информационным выходом сумматора — вычитателя 27, на второй информационный вход которого подключен код, эквивалентный единице.

Устройство работает следующим образом .

Для обеспечения измерения серии временных интервалов между переходами высокочастотного заполнения радиоимпульса на вход устройства подается последовательность радиоимпульсов и запускающих синхроимпульсав Входной радиоимпулъс с высокочастотным заполнением поступает и на информационный вход устройства, (фиг.5а).

Необходимым условием для осущест-. вления измерения является известность диапазона изменения мгновенной частоты BE ñîêo÷àñòîòíñãо заполнения от f, no

Величины констант K и К определяются как отношение длительностей полупериодов Т, и Т сигнала высокочастотного заполнения f, и f и дискрета квантования ht временного интервала в преобразователе код — временной интервал 6:

Т< Т=

К= — -иК„

1 ht

При этом, возможны три ppзульта55 та сравнения разности с выхода вычитателя 19, 1. Выходной код больше значения

К, и меньше К .

На выходе бинарного квантователя

3 формируется последовательность импульсов (фиг 5б).

В качестве запускающих импульсов используются импульсы синхронизации (фиг.5в), сопроваждаюшие каждый радиоимпульс и поступающие на вход синхронизации 2.

По импульсу синхронизации (фиг.5в) осуществляется установка в исходное состояние по входам Сброс" преобразователя код-временной интервал 6, корректора кода 7 и счетчика адреса

10.

В блоке управления 4 по синхроимпульсу, поступающему на вход "3a10 пуск", триггер 13 устанавливается в единичное состояние, отпирая элемент И 14 для прохождения импульсов, поступающих на вход "Строб с выхода преобразователя код — временной

15 интервал 6, Этот же импульс, проходящий через элемент ИЛИ 17 и элемент задержки 18, поступает на третий выход блока управления 4 (фиг,5г). С третьего выхода блока управления им20 пульс поступает на вход управления запиеью преобразователя код — временной интервал 6, Считываемая информация i-1 результата измерения временного положе25 ния нулевого перехода через 0 сигнала высокочастотного заполнения с выхода запоминающего устройства 9 (с нулевого адреса, так как счетчик адреса 10 обнулен) поступает на второй

30 информационный вход корректора ко-: да 7.

Корректор кода функционирует следующим образом. Из кода, поступившего на второй информационный вход корректора кода вычитывается код, хранящийся в регистре 20.

Запись кода в регистр 20 осущести и вляется по импульсу Запись, поступающему со второго выхода блока уп40 равления 4.

Код на вход регистра 20 поступает с выхода блока формирования приращения 8 через первый информационный вход корректора кода 7. Вычитание

45 кодов со второго информационного входа корректора кода и выхода регистра

20 осуществляется с вычитателя 19.

Полученная разность кодов поступает на первые входы блоков сравнения ко50 дов 21 H 22 и сравнивается с кодами, эквивалентными значениям величин кокстант К, и К .

1465870

В блоке управления 4 импульс с выхода элемента задержки 15 задерживается в элементе задержки 16 и через первый выход блока управления 4 поступает на счетный põ«ll <четчика ад55

В этом случае на выходах блоков сравнения кодов 21 и 22 формируется код адреса, который обеспечивает прохождение на информационный выход корректора кода 7 первого числа— со второго информационного входа.

Прн этом, на выходе корректора кода 7 формируется код результата предыдущего цикла измерения, поступившего с выхода запоминающего устройства 9.

2. Выходной код с выхода вычитателя 19 меньше значения К или имеет отрицательное значение. При этом, на выходах блоков сравнения 21 и 22 формируется код адреса, который обеспечивает формирование на выходе корректора кода 7 кода второго числа, т.е. выходного кода сумматора 23, Сумматор 23 осуществляет суммирование значения кода с выхода регистра 20 (для нулевого номера перехода высокочастотного заполнения через "0" значение регистра 20 равно нулю за счет обнуления) с величиной константы К<, На выходе корректора кода формируется код нижней границы диапазона.

3. Выходной код с выхода вычитателя 19 больше величны У« (верхней границы диапазона) в этом случае на выходах блоков сравнения кодов 21 и

22 формируется код адреса, который обеспечивает поступление на выход корректора кода 7 кода с выхода сумматора 24, Сумматор 24 обеспечивает суммирование значения кода с выхода регистра 20 с значением константы К, Откорректированный в корректоре кода 7 код поступает на информационный вход преобразователя код — временной интервал 6 и на информационный вход блока формирования приращения 8.

В преобразователь код — временной интервал 6, код с выхода корректора кода 7, записывается rro импульсу с третьего выхода блока управления 4 (фиг.5I") и начинается преобразование записанного кода в длительность временного интервала.

По окончании преобразования на выходе преобразователя код — временной интервал 6 формируется строб-импульс (фиг.5д), поступающий на вход синхронизации D-триггера 5, по которому записывается значение уровня

50 сигнала на выходе бинарного квантователя 3 (фиг 5б) в D-триггер 5.

Сигнал на выходе D-триггера 5 управляет блоком формирования приращения 8.

Для нулевого адреса на выходе счетчика адреса !О (и для всех четных адресов) младший разряд адреса равен нулю.

Нулевой уровень сигнала на втором управляющем входе блока формирования приращения 8 и соответственно на одном из входов элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 26 приводит к тому, что сигнал с выхода D-триггера 5 управляет сумматором-вычитателем 27 без инверсии.

При этом, если уровень сигнала на выходе Э-триггера 5 нулевой, то к коду, соответствующему временному положению нулевого перехода сигнала высокочастотного заполнения через ноль, поступившему с выхода корректора кода

7, прибавляется единица (значение временного ин гервала увеличивается).

Если уровень сигнала с выхода 0триггера 5 равен единице, то из кода вычитается единица (значенне временного интервала уменьшается). Сформированный код с выхода сумматора-вычитателя 27 блока формирования приращения 8 импульсом со второго выхода блока управления 4 (фиг.5e) записывается в запоминающее устройство 9, блок регистрации 11 и в регистр 20 корректора кода 7. Импульс записи (фиг.5e) формируется путем задержки строба-импульса с выхода преобразователя код-временной интервал 6 (фиг.5д) в элементе задержки 15 блока управления 4, который поступает на элемент задержки )5 через элемент И 14.

Результат i-го измерения нулевого перехода высокочастотного заполнения через ноль записывается в запоминающее устройство 9 по нулевому адресу,.

В регистр 20 корректора кода 7 информация записывается для вычисления следующих границ диапазона измерения первого перехода через ноль сигнала высокочастотного заполнения.

7 1465 реса 10, устанавливая на его выходе код первого адреса.

Емкость счетчика адреса 10 определяется числом измеряемых времен- 5 ных интервалов., Это же число определяет и количество адресов запоминающего устройства 9.и блока регистрации 11.

Далее устройство осуществляет 10

i-oe измерение первого перехода сигнала высокочастотного заполнения через ноль.

Измерение i-го интервала отличается тем, что в регистре 20 корректора кода 7 записан код временного интервала нулевого перехода сигнала высокочастотного заполнения через ноль.

Результат (i-1)-го измерения первого перехода сигнала высокочастотного заполнения через ноль с выхода запоминающего устройства 9 поступает на второй информационный вход корректора кода 7..

В корректоре кода 7 этот код сравнивается с границами диапазона временного положения нулевого перехода через ноль сигнала высокочастотного заполнения плюс величина константы

К 4 (to+K,) и временного положения нулевого перехода через ноль сигнала высокочастотного заполнения плюс константа К (t +Ê ). ! 3.

Формирование приращения в блоке формирования приращения 8 в первой точке измерения (как и во всех нечетных) отличается от формирования приращения в нулевой точке измерения (как и во всех четных).

Поступающий младший разряд счетчика адреса 10 в нечетных интервалах измерения имеет единичное состояние.

Это единичное состояние на входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 обеспечивает инвертирование выходного сигнала

D-триггера 5, т.е. сигнал управления на входе сумматора — вычитателя 27

5 инвертируется.

Таким образом, если сигнал на выходе D-триггера 5 имеет единичное со, стояние — значение записываемого в запоминающее устройство 9 и корректор код 7 временного интервала увеличивается„ Если же уровень сигнала на выходе D-триггера 5 имеет нулевое значение, то величина кода временного интервала уменьшается, 5

Использование элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 в блоке формирования приращения 8 позволяет организовать слежение как за положительными, так и за отрицательными переходами через ноль сигнала высокочастотного заполнения радиоимпульса.

По окончании измерения всех N пе.реходов сигнала высокочастотного saполнения через ноль на выходе счет" чика адреса 10 формируется сигнал переполнения, который поступает на вход

"Сбросп блока управления 4 и устанавливает триггер ll в нулевое состояние.

При этом, запрещается поступление строб-импульса (фиг, 5д) с выхода преобразователя код — временной интервал в блок управления 4, т.е. прекращается формирование импу IbcoB управляюших записью запоминающего устройства 9, блока регистрации 11, корректора кода 7, преобразователя код — временной интервал 6 и с.четчиНа вычитателе 19, на входе кода второго числа, устанавливается код, записанный в регистр 20 в результате

i-го измерения нулевого перехода через ноль сигнала высокочастотного заполнения, Это обеспечивает проверку новых границ диапазона измерения.

Скорректированный код с выхода корректора кода 7 поступает на вход преобразователя код — временной интервал 6 и записывается сигналом с тре-ьего выхода блока управления 4 (фиг.5г) -, На третьем выходе блока управления 4 формируется импульс, задержанный в элементе задержки 18 и поступивший через элемент ИЛИ 17 с выхода элемента задержки 16.

Временной интервал, формируемый для измерения первого перехода отсчитывается от импульса "Сброс" преобразователя код — временной интервал 6 до момента появления первого строба (фиг.5д), так как после формирования

870 8 нулевого временного интервала преобразователь код - временной интервал 6 не обнуляется.

После окончания первого временного интервала повторяется формирование импульсов записи корректора кода

7, запоминающего устройства 9 и блока регистрации 11.

65870

9 14 ка адреса 10, Иа этом режим i-го цик.ла измерения заканчивается.

При этом, в запоминающем устройстве 9 и блоке регистрации 11 хранятся значения измеренных временных интервалов. Информация может быть считана из устройства по выходным шинам блока регистрации 11, являющихся выходными шинами 12 устройства.

В переходном режиме т.е. íà riepвом цикле измерения, значение кодан, хранящихся в запоминающем устройстве

9, — произвольное

Во время первого цикла измерения эти коды корректируются, как указано: последующий кад больше предыдущего на величину не меньше константы

К, и не больше константы К, а значение кода, хранящегося па нулевому адресу, не меньше константы К, и не больше константы К Затем продолжается переходный процесс, т,е, значения кодов временных интервалов уточняются в каждом цикле, измерения до достижения установившегося значения, Введение констант К, и К обеспечивает также временную селекцию страбон, что обеспечивает возврат страбон при случайном сбое устройства при воздействии помехи.

Таким образом, изобретение позволяет уменьшить величину флюктуацианной погрешности при измерении в условиях .помех. Это обеспечивается тем, что измерение ведется в следящем режиме в N каналах измерения, Кроме того, наличие анализа кодов позволяет восстановить работу устройства при наличии сбоя.

Формула иэ обретения входом "Сброс" корректора кода и с входом синхронизации устройства,сигнальный вход которого соединен с вха5 дам бинарного квантавателя, выход которага подключен к информационному входу D-триггера, прямой выход котарага соединен с первым входом управления блока формирования прира10 щений, выход которого подключен к перному входу корректора кода, к информационному входу блока регистрации и информационному входу запоминающего устройства, выход которого !

5 соединен с вторым входом корректора кода, выход которого подключен к информационному входу блока формирования приращений и к информационному входу преобразователя кад †времен20 ной интервал, выход которого соединен с входом "Строб блока управления и с входом синхронизации D-триггера, а первый выход блока управления подключен к счетному входу. счетчика адреса, выходы всех разрядов которого соединены с адресным входом блока регистрации и с адресными входами запоминающего устройства, вход

Запись которого подключен к входу

Запись корректора кода, к входу

"Запись" блока регистрации, к второму выходу блока управления, третий

И выход которого соединен с входом Запись преобразователя кад — времен35 ной интервал, а второй вход управления блока формирования приращений подключен к выходу младшего разряда счетчика адреса, выход переполнения

11 !I которого соединен с входом Сброс

40 блока управления, а выход блока регистрации является выходом устройства.

1. Устройство для измерения серии временных интервалов, содержащее счетчик адреса, запоминающее устройство и информационный вход, а т л ич а ю щ е е с я тем, что, с целью уменьшения флюктуационной погрешности измерения, в него введены преобраэонатель код - временной интервал, бинарный квантователь, D-триггер, блок формирования приращения, корректор кода, блок регистрации, блок управления, вход Запуск которого соединен с входом "Сброс" счетчика адреса, входом "Сброс" преобразователя код - временной интервал, с

2. Устройство па п. 1, а т л ич а ю щ е е с я тем, чта блок управ45 ления содержит триггер, элемент И, элемент ИЛИ и три элемента задержки причем выход первого элемента задерж-. ки является вторым выходом блока управления и подключен к вхоДу второго

50 элемента задержки, выход которого является первым выходом блока управления и подключен к первому входу элемента ИЛИ, выход которого соединен с входом третьего элемента за55 держки, выход которого является третьим выходом блока управления, вход нЭапускп которого подключен к второму нходу элемента ИЛИ и к входу

1465870

Стр улус установки триггера в единичное состояние, а вход первого элемента эадержки соединен с выходом элемента

И, первый вход которого является вхо}} }!

5 дом Строб блока управления, вход

}! }1

Сброс которого подключен к входу установки в нулевое состояние триггера, прямой выход которого подключен к второму входу элемента И. 10

3. Устройство по и. l, о т л и— ,ч а ю щ е е с я тем, что корректор кода содержит два блока сравнения кодов, два сумматора, вычитатель, регистр и коммутатор, информационный выход которого является выходом корректора кодов, первый информационный вход которого соединен с информационными входами регистра, входы записи информации и обнуления кото- 2р рого подключены соответственно к входам "Запись}} и "Сброс" корректора кода, второй информационный вход которого соединен с первым информационным входом первого числа коммутатора 25 и входом первого числа вычитателя, вход второго числа которого подключен к информационному выходу регистра и первым информационным входам первого и второго сумматоров, на вто- ЗО рые входы которых поданы соответственно коды первой и второй констант, а выходы первого и второго сумматоров подключены соответственно к второму и третьему информационным входам второго и третьего чисел коммутатора, первый и второй адресные входы которого соединены с выходами соответственно первого и второго блоков сравнения, первые информационные входы которых объединены и подключены к информационным выходам. Вычитателя, а на вторые входы первого и второго блоков сравнения поданы соответственно коды первой и второй констант.!

4, Устройство по и, 1, о т л и ч аю щ е е с я тем, что блок формирова-ния приращения содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор-вычитатель} вход управления операцией которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с первым входом управления блока формирования приращения, второй вход управления которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, а информационный вход блока формирования приращений соединен с входом кода первого числа сумматора-вычитателя, на входе второго числа которого установлен код 1, а выход сумматора-вычитателя является выходом блока формирования приращений.

)465870 ими дх.

Со с тани тель Ю. Шишк ин

Редактор И.Сегляник Техред Л.Олийнык Корректор М.Шароши

Закаэ 946/49 Тираж 364 Подписное

ВИИИПИ Государственного комитета по изобретениям и открытиям прн ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбина.. Патент", r. жгород, у и °

Ф! у л. Гага ина 101 р р