Устройство для нормализации и округления чисел с плавающей запятой

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительнор1 технике и может - быть использовано при построении арифметических устройств вычислительных машин, а также в устройствах цифровой обработки сигналов. Цель изобретения - повышение быстродействия . Поставленная цель достигается тем, что в устройство, содержащее . Шифратор 3 приоритета, мультиплексоры 6,7, блок 8 формирования порядка и кода нормализации и сумматор 9 округления, введена схема 10 .сравне- , ния с константой с соответствующими связями. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1 (191 (Н) (5ц 4 С 06 F 7 38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМ

ПРИ ГКНТ СССР (21) 4193253/24-24

,22) 09.02.87

,46) 15,02.87. Был. Ф 10

,72) О.Н. Галченков, А.М. Кузьминский и Н.M. Лауберг ,(53) 681.325,088.8) (56) Авторское свидетельство СССР

1056181, кл. G 06 F 7/38, 1982.

Авторское свидетельство СССР

Ф 1418704, кл. G 06 F 7/38, 1987. (54) УСТРОЙСТВО ЛЛЯ НОРМАЛИЗАЦИИ

И ОК?УГЛЕНИЯ ЧИСЕЛ С Г1ЛАВАЮЩЕЙ ЗАПЯ—

ТОЙ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин, а также в устройствах цифровой обработки сигналов. Цель изобретения — повышение быстродействия. Поставленная цель достигается тем, что в устройство, содержащее шифратор 5 приоритета, мультиплексоры 6,7, блок 8 формирования порядка и кода нормализации и сумматор 9 округления, введена схема 10 .сравне- ния с константой с соответствукщими связями. 2 ил.

879

1 1465

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин, а также в устройствах цифровой обработки сигналов„ работающих в системе счисления с плавающей запятой.

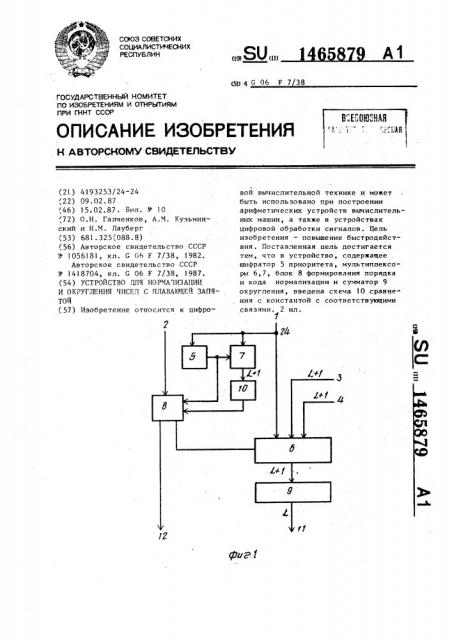

Цель изобретения — повышение бы10 стродействия, На фиг, 1 представлена схема устройства для нормализации и округления чисел с плавающей запятой; на фиг. 2 — схема первого мультиплексора.

Устройство,(фиг.1) содержит вход

1 мантиссы числа устройства, вход 2 порядка числа устройства, вход 3 максимального значения мантиссы устройства, вход 4 контакты устройства, .шифратор 5 приоритета, первый и второй мультиплексоры 6 и 7, блок .8 формирования порядка и кода нормализации, сумматор 9 округления, схему 10 25 сравнения с константой, выход 11 мантиссы результата устройства, выход

12 иэ порядка результата устройства.

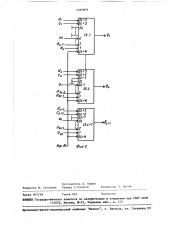

Первый мультиплексор 6 (фиг. 2) содержит одноразрядные мультиплексо- . ры 13.1-13,L+1 (L - разрядность мантиссы результата, каждый из которых имеет 2Ь+3 информационных входа и управляюций 2L+4 вход). Управляющие входы одноразрядных мультиплексоров соединены между собой и представляют собой управляющий вход первого мультиплексора б. Разрядность сигналов, поступающих по этому входу, равна наименьшему целому числу, кото40 рае больше или равно 1og < (2L+3)

Воспользуемся следующими обозначениями: а,,а,,,...,а, — разряды входа 1 устройства; c « с, — разряды входа 3 устройства; dory(с1,— разряды входа 4 устройства. На первые информационные входы мультиплексоров 13.L+1 13.1 поданы соответственно разряды а,,...,а,. На вторые информационные входы мультиплексоров

13.L+1,...,13.1 поданы соответственно разряды а,,,...,а, . И так далее да 2L входа со сдвигом на один разряд, при условии, что если на -вход

J мультиплексора 13Ь подан разряд а.„, то (i+1),...,2Ь входы этого мульти. плексора соединяются со входом нулевого уровня. 2L+1-е входы мультиплексоров 13.L+1 13.1 соединены со входом нулевого уровня, На 2L+2-å информационные входы мультиплексоров 13.1.+1,...,13.1 поданы соответственна разряды с,...,ст. А на +1

2L+3-е соответственно разряды d

l+t ...,di В зависимости от уттравляючих сигналов, каждый из мультиплексоров

13.L+1 — 13.1, пропускает на выход по одному из разрядов, из того набора, что поступают на их входы. Разряды на их выходах b L+,,...,Ü, сасставляют выходной сигнал первого мультиплексора 6, Блок 8 реализован на постоянном запоминающем устройстве (ПЗУ), принцип кодировки которого следующий.

Устройство (фиг.!) работает следующим образом.

2L-разрядная мантисса числа са входа I устройства поступает на пер- вый информационный вход мультиплексора 6, на информационный вход мультиплексора 7 "и на вход шифратора 5 приоритета. На выходе шифратора 5 приоритета получается кад, равный числу нулевых разрядов, считая со старшего, разряда входного кода до первого ненулевого разрчда. Этот код . поступает на первый управляющий вход блока 8 и на управляющий вход второго мультиплексора 7; Второй мультиплексор 7 сдвигает влево в соответствии с этим управляющим сигналом код, поступающий на его информационный вход и пропускает на свой выход

Ь+! старших разрядов сдвинутого кода.

Выходной сигнал второго мультиплек-. сора 7 поступает на вход схемы 10 сравнения, выход которой является вторым управляющим входом блока 8.

Если в старших Ь разрядах входного кода схемы 10 сравнения максимально возможные значения, а в младшем

Ь+1-м разряде код больше половины максимально возможного (например, при двоичной системе счисления в L+l-м разряде кад "1", или при шестнадцатиричной системе счисления в L+1-м разряде код от "8" до "F ), та на выходе схемы !О сравнения единичный уровень, в противном случае — нулевой. Порядок числа со входа 2 устройства постуттает на информационный вход блока S, который формирует на своем втором выходе порядок результата, а на первом выходе — значение, поступающее на управляюций вход муль14658

50 типлексора 6. При этом, во зможны следующие случаи.

1. Если порядок числа при вычете числа разрядов, на которое нужно

5 сдвинуть мантиссу при нормализации, обозначим его через S), превышает максимально допустимый порядок, т.е. имеет место ситуация "переполнение порядков", то блок 8 выдает на втором 10 выходе максимально допустимый код порядка, а на первом выходе такой управляющий сигнал для первого мультиплексора 6, по которому он пропус-. кает на свой выход L+1 разрядов, по- 15 ступающие на его второй вход со входа 3 устройства старшие L разрядов представляют собой максимально возможный код мантиссы, L+1-й разряднулевой). 20

2. Если нет предыдущей ситуации, S не меньше минимально допустимого порядка и меньше максимально допустимого порядка и на втором управляющем входе блока 8 единичный уровень, то 25 блок 8 выдает на втором выходе порядок, равный S+1 а на первом выходе — управляющий сигнал, по которому первый мультиплексор 6 пропускает на свой выход Ь+1 разрядов, поступающих 30 на его третий вход со входа 4 устройства,первый старший разряд — единица, остальные нули).

3. Если S равно максимально допустимому порядку и на втором управляющем входе блока 8 — единичный уровень, то блок 8 выдает на входах также сигналы, как и в первой ситуации.

4. Если S меньше минимально допус- 40 тимого порядка, а поряцок (обозначим его Р) больше минимально допустимого порядка, то блок 8 на втором выходе выдает минимально допустимый порядок, а на первом выходе — код, 45 по которому первый мультиплексор 6 пропускает на выход L+1 старших разрядов кода входа 1 устройства, сдвинутого влево на число разрядов, равное разности P и минимально допустимого порядка, 5. Если нет предыдущих ситуаций и S-P равно 2L, то на втором выходе блока 8 выдается код, соответствующий минимально допустимому порядку, а на первом выходе — код, по которо- . му первый мультиплексор 6 пропускает на выход значение входа 1, сдви79 4 нутое на 2L разрядов влево, т.е. нулевой код.

6. Если нет предыдущих ситуаций, то на втором выходе блок 8 выдает код S а на первом выходе — код, по которому первый мультиплексор 6 пропускает на выход L+1 разрядов кода со входа 1 устройства, сдвинутого влево на S-P разрядов. L+1 разрядов с выхода первого мультиплексора 6 поступают на вход сумматора 9 округления, осуществляющего округление до Ь разрядов, Переполнение в сумматоре 9 округления исключено, с выхода сумматора 9 округления мантисса результата поступает на вход 11 уст-ройства.

Формула изобретения

Устройство для нормализации и округления чисел с плавающей запятой, содержащее шифратор приоритета, два мультиплексора, блок формирования порядка и кода нормализации и сумматор округления, причем вход мантиссы числа устройства соединен с первым информационным входом первого мультиплексора, с информационным входом второго мультиплексора и с входом шифратора приоритета, выход которого соединен с управляющим входом второго мультиплексора и с первым управляющим входом блока формирования порядка и кода нормализации, информационный вход которого соединен с входом порядка числа устройства, вход максимального значения мантиссы и вход константы контроля соединены соответственно с вторым и третьим информационными входами первого мультиплексора, управляющий вход которого соединен с первым выходом блока формирования порядка и кода нормализации, второй выход которого является выходом порядка результата устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит схему сравнения с константой, причем выход второго мультиплексора соединен с входом схемы сравнения с константой, выход которой соединен с вторым управляющим входам блока формирования порядка и кода нормализации, выход первогс мультиплексора соединен с входом слагаемого сумматора округления, выход которого является выходом мантиссы результата устройства.

1465879

Or

Су

Составитель А. Клюев

Редактор И. Сегляник Техред . t.Îëèéíûê

Корректор Л. !1атай

Заказ 947/49 Тираж 667 Подписное

ВНИИПИ Государственного комитета по изобретениям н открытиям при ГКНТ СССР

113035, Москва, K-35, Рауаская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101