Интерполятор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для аппаратной сплайн-аппроксимации функции. Цель изобретения - noBbmeime быстродействия и точности интерполятора. С этой целью в интерполятор дополнительно введен умножитель . Интерполятор производит аппроксимацию функции класса С (первая и вторая производные сплайна непрерьшны). 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (дд 4 G 06 F 15/353

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (61) 1405076 (21) 4155349/24-24 (22) 02. 1 2, 86 (46) 15.03.89. Бюп. Р 10 (71) Ленинградский электротехнический институт им. Б.И. Ульянова (Ленина) (72) А.С.Просочкин, А.АеДокучаев и Е.А;Колесников (53) 681.325 (088.8) (56) Авторское свидетельство СССР

N - 1405076, кл. G 06 F 15/353, 27.10.86.,Изобретение относится к вычислительной технике, является дополнительным к авт. св N - 1405076 и может быть использовано для аппаратной сплайн-аппроксимации функций.

Цель изобретения — повышение быстродействия и точности интерполятора.

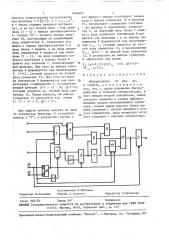

На чертеже приведена функциональная схема интерполятора.

Интерполятор содержит счетчик 1, регистры 2, 3, преобразователь 4 в дополнительный код, коммутатор 5,блоки 6, 7 памяти, умножители 8, 9, триггер 10, элемент НЕ 11 и накапливающий сумматор, содержащий сумматор

12 и регистр 13, входы 14 и 15 запуска и сброса.

Устройство работает следующим образом.

В исходном состоянии на входы l4 и 15 запуска и сброса устройства подаются сигналы "1".

Код номера j функции Г (х) (j

1,...,2, где m - разрядность кода

„„SU,, >46589 А2 (54) ИНТЕРПОЛЯТОР (57) Изобретение относится к вычислительной технике и может быть использовано для аппаратной сплайн-аппроксимации функции. Цель изобретения— повышение быстродействия и точности интерполятора. С этой целью в интерполятор дополнительно введен умножитель. Интерполятор производит аппроксимацию функции класса С (первая и вторая производные сплайна непрерывны). 1 ил, номера функции) определяет j-É мас- g сив ячеек блока 6 памяти, отводимый для хранения коэффициентов аппрокси- С мации данной функции. Группа старших ,разрядов аргумента, определяющих номер участка аппроксимации воспроизводимой функции, подается на информационный вход счетчика 1, а группа @, младших разрядов аргумента, опреде- ® „ ляющих его положение внутри участка аппроксимации, поступает на вход регистра 2. Работа устройства начинается с подачи на вход 5 сброса сигнала

<©

"0", который переводит счетчик 1 в режим приема старших разрядов аргумента, сбрасывает триггер 10, регистр 13, при этом сигнал с выхода элемента НЕ 11 стробирует зались младших разрядов аргумента в регистр

2. На первый вход коммутатора 5 с выхода регистра 2 поступает код группы младших разрядов аргумента, определяющий величину t = (х — х„) (где h = (х;, — х, ) — длина i-ro

Г;, (x)=f, (1-t)+f t+D, q(1-t)+

+D;Ä. q (t) Формула из обр ет ения

Составитель Н.Матвеев

Редактор M.Êeneìåø Техред А.Кравчук Корректор О.Кравцова Заказ 948/50 Тираж 667 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035„ Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент"„ г.ужгород, ул. Гагарина,101.

3 14658 у астка аппроксимации воспроизводимРи функцииу t E (0,1); i = 1 р ° ° в,2 у р — число старших разрядов аргументй), а на его второй вход — код вели- 5 чйны (1 — t) с выхода преобразователя

4, Сигнал "0" с прямого выхода тригг ера 10, поступающий на управляющий в!ход коммутатора 5, подключает его

ыход к выходу преобразователя 4 и ход блока 7 памяти, и на вход множнеля умножителя 8 подается код велиHHbl (1 -- t)> на вход множнмого коорого поступает с выхода блока 6 амяти код значения 1.„ воспроизводи- 1В ой функции. При этом на выходе умнотеля 8 формируется код произведения (t-t), который подается на второй ход сумматора 12. При этом на выхое умножителя 9 формируется код про- 20 зведения коэффициента D; и корректиующей функции g (" ") D „ (1 ) оторый подается на первый вход суматора 12. Таким образом, на выходе умматора 12 образуется код суммы 26 (1 - t) + D,. (1 — t). (При подаче сигнала запуска на вход, 14 устройства триггера 10 устанавли- вается в "1", в результате сигнал с

93 4

его прямого выхода стробирует запись кода с выхода сумматора 12 в регистр

13, увеличивает содержание счетчика

1 на единицу и переключает коммутатор 5, на адресный вход блока 7 памяти и вход множителя умножителя 8 подается код величины t и на выходе умножителя 8 формируется код произведения f., t, который подается ла вто" рой вход сумматора 12, а произведение

D, ((t) — на первый вход сумматора

12. В результате на выходе сумматора

6 образуется код суммы

Интерполятор по авт. св.

11 - 1405076, о тлич ающий ся тем, что, с целью повышения быстродействия и точности интерполятора, в него введен второй умножитель, выход которого соединен с вторым информационным входом накапливающего сумматора, второй выход первого блока памяти соединен с входом множимого второго умножителя, вход множителя которого соединен с выходом коммутатора.