Триггер на дополняющих мдп-транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в цифровых интегральных схемах, к которьЫ предъявляются требования установки триггеров и триггерных устройств в определенное исходное состояние в процессе нарастания напряжения питания. Цель изобретения - снижение потребляемой триггером мощности в статическом режиме и повышение надежности его установки в определенное исходное состояние в процессе нарастания напряжения питания. Устройство содержит два инвертора 1 и 2 с перекрестными связями, цепь установки триггера в определенное исходное состояние , состоящую из первого, второго , третьего и четвертого транзисторов 9, 10, 11, 14. За счет введения первого и второго дополнительных транзисторов 12, 13 обеспечивается форсированный заряд выхода инвертора 1 в момент нарастанця напряжения питания. Размеры транзисторов 12, 13 выбираются равными, что обеспечивает симметрию емкостной нагрузки на плечи триггера. Размеры первого и второго транзисторов 9, 10 выбираются такими , чтобы время заряда емкости внутреннего узла триггера, связанной со стоком транзистора 9, до уровня порогового напряжения транзисторов 11, 14 и напряжения запирания транзистора 12 превьшало время установления в определенное исходное состояние потенциалов на выходах инверторов 1 и 2. 1 ил. (Л О) ел о со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ш 4 H 03 К 3/2869 17/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHQMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ rHHT СССР (21) 4201034/24-21 (22) 27.02.87 (46) 15.03.89. Бюл. Ф 10 (72) Д.И.Барановский и С.В.Проворов (53) 621.374(088.8) (56) Авторское свидетельство СССР

11 921052, кл. Н 03 К 3/286, 1980. (54) ТРИГГЕР НА ДОПОЛНЯЮЩИХ МДП-ТРАНЗИСТОРАХ (57) Изобретение относится к импульсной технике и может быть использовано в цифровых интегральных схемах, к коTopblM предъявляются требования установки триггеров и триггерных устройств в определенное исходное состояние в процессе нарастания напряжения питания. Цель изобретения — снижение потребляемой триггером мощности в статическом режиме и повышение надежности его установки в определенное исходное состояние в процессе нарастания напряжения питания. устройствО

ÄÄSUÄÄ 1465939 А1 содержит два инвертора 1 и 2 с пере= крестными связями, цепь установки триггера в определенное исходное состояние, состоящую из первого, второго третьего и четвертого транзисторов 9, 10, 11, 14. За счет введения первого и второго дополнительных транзисторов 12, 13 обеспечивается форсированный заряд выхода инвертора 1 в момент нарастания напряжения питания. Размеры транзисторов 12, 13 выбираются равными, что обеспечивает симметрию емкостной нагрузки на плечи триггера. Размеры первого и второго транзисторов 9, 10 выбираются такими, чтобы время заряда емкости внутреннего узла триггера, связанной а со стоком транзистора 9, до уровня порогового напряжения транзисторов

11, 14 и напряжения запирания транзистора 12 превышало время установления в определенное исходное состояние потенциалов на выходах инверторов 1 и 2. 1 ил.

1 1465939 2

Изобретение от:|осится к импульсной технике и может быть использовано в цифровых интегральпьгх. схемах, к которым предъявля|: тся требования уста5 новки триггеров и триггерных устройств в бпределенное исходное состояние в процессе нараста.ния напряжения питания.

Цель изобретения — снижение пот1 ! .ребляемой триггером мощности в стати-! ческом режиме и повьш|ение надежности его устBHQBKH в определенное исходное, состояние в процессе нарастания нап-! ряжения питания. 15.

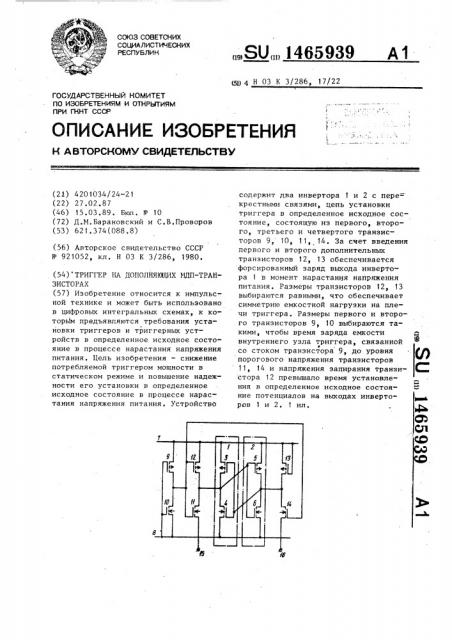

На чертеже представлена электрическая принципиальная схема описываемого триггера.

Триггер состоит из инверт оров 1 и 2 с перекрестными связями, каждый 20 ! из которых содержит два .комплемен| тарных транзистора 3, 4 и 5, 6 соот-! ветственно, последовательно включенных между шиной 7 питания и общей шиной 8, первого тра;|зистора 9 первого 25 типа проводимости, исток кототорого подключен к шине 7, затвор -- к шине

8, сток — к стоку и затвору соответственна второго 10-и тр тьего 11 транзисторов второго типа проводимос- 30 ти, истоки которых подклкчены х шине 8 и выходу инвертора 1 соответственно.- Истоки двух дополнительно введенных транзисторов !2 и 13 первоГО типа проводимости подключены к ши-35

1 не 7. При этом сток транзистора 12 подключен к выходу инвертора 1, а его затвор — к затвору четвертого тран( зистора 14 и стоку транзистора I0, затвор которого поцключен к истоку 40 и шине 8, затвор транэи< тора 13 подключен к шине 7, сток — к выходу инвертора 2 и истоку транзистора 14.

Прямым 15 и инверсным 16 выходами триггера являются стоки транзисторов

11 и 14 соответственно.

Триггер на дополнительных МДПтранзисторах работаег следующим образом.

В процессе нарастания. напряжения питания вначале открываются транзис-, 50 торы 3, 5, 9, 12, что приводит к постоянному заряду внутренних узлов триггера, Размеры транзисторов 3, 4, 11 и 12 выбираются равными размерам транзисторов 5, 6, 14 и 13 соответственно, что обеспечиваь т симметрию емкостной нагрузки на плечи триггера, при этом суммарная ширина канала транзисторов 3 и 12 больше ширины канала транзистора 5, что приводит в процессе нарастания напряжения питания к более быстрому заряду выхода . первого инвертора по сравнению с выходом второго инвертора. Размеры . транзисторов 9 и 10 выбираются такими, чтобы время заряда емкости внутреннего узла триггера, связанной со стоком транзистора 9, до уровня порогового напряжения транзисторов 11, 14 и напряжения эапирания транзистора 12 превышало как время установления в определенное исходное состояние потенциалов на вьгходах инверторов 1 и 2 с перекрестными связями, так и время переходных процессов во внешних устройствах, подключенных к выходам t5 и 16 триггера, Таким образом, после заряда внут— реннего узла триггера, связанного со стоком транзистора 9, до уровня напряжения питания транзистор 12 оказывается закрытым, а транзисторы 11 и

14 открытыми по затвору, на прямом 15 и инверсном 16 выходах триггера устанавливаются потенциалы питания и общей шины . соответственно. В дальнейшем триггер по выходам 15 и 16 может управляться внешними логическими сигналами, Формула изобретения

Триггер на дополняющих МДП-транзисторах, содержащий два инвертора с перекрестными связями, первый тран» зистор первого типа проводимости, исток которого подключен к шине питания, затвор — к общей шине, сток к стоку и затвору соответственно второго и третьего транзисторов второго типа проводимости, истоки которых подключены соответственно к общей шине и к выходу первого инвертора, четвертый транзистор второго типа проводимости, отличающийся тем„ что, с целью снижения потребляемой триггером мощности в статическом режиме и повышения надежности его установки в определенное исходное состояние в процессе нарастания напряжения питания, в триггер введены два дополнительных транзистора первого типа проводимости, истоки которых подключены к шине питания, сток первого допопнительного транзистора подключен к выходу первого инвертора, Составитель А.Цехановский

Техред Л. Сердюкова Корректор O.Кравцова

Редактор А.Маковская

Заказ 953/52 Тираж 879 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035) Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина,101

1465939

4 а его затвор — к затвору четвертого ственно, причем, размеры первого и транзистора и стоку второго транзис- второго транзисторов выбираются из тора, затвор которого подключен к об- условия, >7 », где, — врещей шине, при этом затвор второго мя заряда емкости, связанной со стодополнительного транзистора подключен ком первого транзистора, — время к шине питания, сток — к выходу вто- заряда емкости, связанной со стоком рого инвертора и истоку четвертого второго дополнительного транзистора, транзистора, стоки третьего и четвер- c — время заряда емкости, связанной

Ф того транзисторов являются прямым и 10 со стоком первого дополнительного инверсным выходами триггера соответ- транзистора °