Асинхронный распределитель

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах i формирования последовательности сигналов. Целью изобретения является упрощение устройства и повышение его быстродействия за счет использования в цепи обратной связи разрядной ячейки МДП-транзисторов и асинхронного режима его переключения. Цель достигается путем введения в устройство, содержащее в каждой разрядной ячейке 1 элемент ШЖ-НЕ 2 и инвертор 3, дополнительно НЦП-транзистора 4, включенного между информационной шиной 6 разрядной ячейки 1 и входной управляющей шиной 7, которая в свою очередь соединена с выходной управляющей шиной 5 последующей разрядной ячейки. 1 ил. а S (Л

СОЮЗ СОНЕТСИИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

f19) (И) 4 5997 А1

CSV 4 Н 03 К 17/62 17 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4263983/24-21 (22) 16.06.87 (46) 15.03.89. Бюп. У 10 (71) Ленинградский электротехнический институт им.В.И.Ульянова (Ленина) (72) В.И.Варшавский, А.Ю.Кондратьев, Н.И.Кравченко и В.С.Цирлин (53) 531. 71 (088. 8) (56) Авторское свидетельство СССР

Р 416868, кл. Н 03 К 17/62, 21.08.72.

Ав тор ск ое с виде т ель с тво СССР

У 1064461, кл. Н 03 К 17/00, 19.05.82. (54) АСИНХРОННЬЙ РАСИРЕДЕЛИХЕЛЬ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах формирования последовательности сиг- налов. Целью изобретения является упрощение устройства и повышение его быстродействия за счет использования в цепи обратной связи разрядной ячейки NgH-транзисторов и асинхронного режима его переключения. Цель достигается путем введения в устройство, содержащее в каждой разрядной ячейке 1 элемент ИЛИ-НЕ 2 и инвертор 3, дополнительно 1ЩП-транзистора 4, включенного между информационной шиной 6 разрядной ячейки 1 и входной управляющей шиной 7, которая в свою очередь соединена с выходной управ- а ляющей шиной 5 последующей разрядной ячейки. 1 ил.

146599 1 г

Изобретение относится к автоматиl ке и вычислительной технике и может ( быть использовано в устройствах формирования последовательностей сигналов.

Цель изобретения — упрощение устройства и повышение его быстродействия за счет использования в цепи обратной связи разрядной ячейки,1О выполненной на логических элементах ИЛИ-НЕ, МДП-транзистора и асинхронного режима его переключения.

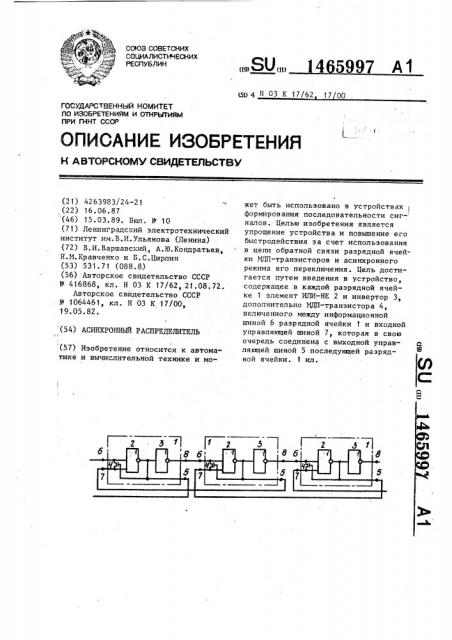

На чертеже приведена принципиальная схема асинхронного распредели.теля на три разряда.

Устройство содержит в каждой разрядной ячейке 1 два инвертирующих ( логических элемента: элемент ИЛИ-НЕ 2 и инвертор 3, а также МЦП-транзис,:ор 4.

2О (Выход элемента ИЛИ-НЕ 2 соединен с входом инвертора 3, затвором МДПтранзистора 4 и с вцходной управляю-,щей шиной 5. 25

Первый вход элемента ИЛИ-НЕ 2 сое динен с входной информационной ши ной 6 и со стоком МДП-транзистора 4, исток которого соединен с входной управляющей шиной 7 той же ячейки и с вторым входом элемента ИЛИ-НЕ 2.

Выход инвертора 3 поцключен к выходной информационной шине 8 .разрядной ячейки 1.

Выходная информационная шина 8 разрядной ячейки 1 соединена с входной информационной шиной 6 последую(,щей разрядной ячейки, а входная управляющая шина 7 соединена с выходной управляющей шиной 5 той же последующей разрядной ячейки, Асинхронный распределитель работает следующим образом.

В исходном состоянии разрядной ячейки 1 на выходе элемента ИЛИ-НЕ

2 имеется нулевой логический уровень, а на выходе инвертора 3 — единичный, МДП-транзистор 4 находится в закрытом состоянии. В асинхронном распределителе установка (L 1)-й разрядной ячейки 1 производится подачей нулевого логического уровня на;информационную входную шину 6 ° При этом на выходе элемента ИЛИ-НЕ 2 появится еди1 ничный логический уровень, который открывает МДП-транзистор 4 этой разрядной ячейки и вызывает появление нулевого логического уровня на выходе инвертора 3. Открытий МДП-транзис\ тор 4 закооачивает входные шины 6 и

7 (i-1)-й разрядной ячейки 1 и поэтому на шинах 6 и 7 нулевой логический уровень сохранится до тех пор, пока хотя бы на одной иэ.выходных шин: 8 (1. 2)-й разрядной ячейки или

5 i-й разрядной ячейки имеется нулевой логический уровень. Если в результате установки 1 и разрядной ячейки и сброса (i-2)-й разрядной ячейки на шинах 8 (i-2)-й и 5 i-й разрядньгх ячеек появится единичный логический уровень, то происходит сброс (i-1)-й разрядной ячейки: на выходе элемента ИЛИ-НЕ 2 появляется нулевой логический уровень, МДП"транзистор 4 переходит в закрытое состояние, на выходе инвертора 3 появляется единичный логический уровень.

При этом до тех пор, пока в i-й ячейке на шине 5 имеется единичный логический уровеньр (1 1) я разряд ная ячейка не может быть установлена: на выходе элемента ИЛИ-НЕ 2 этой разрядной ячейки нулевой логический уровень будет сохраняться вне зависимости от значения сигнала на шине 6.

Таким образом, повторная установка (i-1)-й разрядной ячейки .1 осуществляется лишь после того, KRK

i-я разрядная ячейка 1 окажется в. исходном состоянии. Следовательно, 1 при повторной инициации работы асинхронного рапределителя до того, как завершится предыдущий цикл его работы, последующая волна установок ячеек не достигнет предыдущей, так как между ними всегда будет находиться одна .ячейка в исходном состоянии, что обеспечивает правильное функционирование распределителя в мультипрограммном режиме.

Положительный эффект в устройстве достигается за счет использования всего лишь двух простейших логических элементов и одного МДП-транзистора на разряд и сокращения числа связей между ячейками, При этом повышение быстродействия обусловлено уменьшением числа логических элементов в цепях переключения и упрощением самих логических элементов.

Формула.изобретения

Асинхронный распределитель, со- держащий разрядные ячейки, каждая из которых содержит два инвертируюСоставитель В.Лементуев

Техред М.Дидык Корректор С.Шекмар

Редактор Н,Киштулинец

Заказ 956/55

Тираж 879

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4!5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101

3 14659 щих логических элемента, причем Bbl ход первого подключен к входу второго, а информационная выходная шина и управляющая входная шина разрядной

1 ячейки подключены соответственно к информационной входной и управляющей выходной шинам последующей разрядной ячейки, отличающийся тем, что, с целью упрощения и повы- 1п шения быстродействия, в каждую разрядную ячейку введен МДП-транзистор, первый инвертирующий логический эле97 4 мент выполнен в виде элемента ИЛИ-НЕ, а второй — в виде инвертора, причем входы элемента ИЛИ-НЕ, между которыми включен МЦП-транзистор, соединены соответственно с входной информационной и входной управляющей шинами разрядной ячейки, выход элемента

ИЛИ-НЕ соединен с затвором МДП-транзистора и с управляющей выходной шиной разрядной ячейки, а выход инвертора соединен с информационной выходной шиной разрядной ячейки.