Устройство для измерения части интерференционной полосы

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике. Цель изобретения - повышение точности измерения части интерференционной полосы йутем обеспечения цифровой обработки сигналов двух интерферометров. При перемещении объекта 25 измеряется часть периода выходного гармонического сигнала фотоприемиика 4, преобразующего в электрический ток выходные, световые сигналы интерферометра 2. Текущее значение амплитуды сигнала преобразуется в код К 1 А1Щ 6. В регистре 9 памяти запоминается код, соответствующий амплитуде сигнала интерферометра 3 в момент начала цикла измерений. Блок 12 сравнения сравнивает текущее значение кода с кодом, записанным в регистре 9 памяти. При совпадении кодов на выходе коммутатора 14 формируется импульс. В этот момент в блоке 18 вычитания происходит сравнение кода К 1 и кода, соответствующего определенной амплитуде сигнала. Их разность & сравнивается с заранее установленной величиной ,(, и при Д d к блок 11 сравнения вырабатывает импульс, приводящий систему в исходное состояние. При блок 22 умножения осуществляет перемножение числа импульсов, подсчитанных счетчиком 21 за цикл измерения, и константы , равной разности цен полос интерферометров 2, 3. Результат отображается индикатором 23. 5 ил. fi &0 ел .l

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

fO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4314404/24-28 (22) 09.10.87 (46) 23.03.89. Бюл. Р 11 (7 1) Институт электроники AH БССР (72) Ю.Г.Буров и И.М.Лакоза (53) 531.7.717(088.8) (56) Авторское свидетельство СССР

1Ф 1165884, кл. G 01 В 21/00, 1984. (54) УСТРОЙСТВО ДЛЯ ИЗИЕРЕИИЛ ЧАСТИ

ИНТЕРФЕРЕНЦИОННОЙ ПОЛОСИ (57) Изобретение относится к измерительной технике. Цель изобретения— повьппение точности измерения части интерференционной полосы йутем обеспечения цифровой обработки сигналов двух интерферометров. При перемещении объекта 25 измеряется часть периода выходного гармонического сигнала фотоприемника 4, преобразующего в электрический ток выходные, световые сигналы интерферометра 2. Текущее значение амплитуды сигнала преобра„„SU„„1467395 ц 4 G 01 В 21/00 зуется в код К 1 АЦП 6. В регистре 9 памяти запоминается код, соответствующий амплитуде сигнала интерферометра

3 в момент начала цикла измерений.

Блок 12 сравнения сравнивает текущее значение кода с кодом, записанным в регистре 9 памяти. При совпадении кодов на выходе коммутатора 14 формируется импульс, В этот момент в блоке 18 вычитания происходит сравнение кода К 1 и кода, соответствующего определенной амплитуде сигнала. Их разность р сравнивается с заранее установленной величиной Д», и при а (а „ блок 11 сравнения вырабатывает импульс, приводящий систему в исходное состояние. При этой блок 22 ум-. ножения осуществляет перемножение числа импульсов, подсчитанных счетчиком 21 за цикл измерения, и константы, равной разности цен полос интерферометров 2, 3. Результат отображается индикатором 23. 5 ил .

1467395

Изобретение относится к измерительной технике и может быть использовано для измерения в динамическом режиме (т.е. в процессе движения) части периода выходного электрического гармонического сигнала интерференционного преобразователя линейных перемещений.

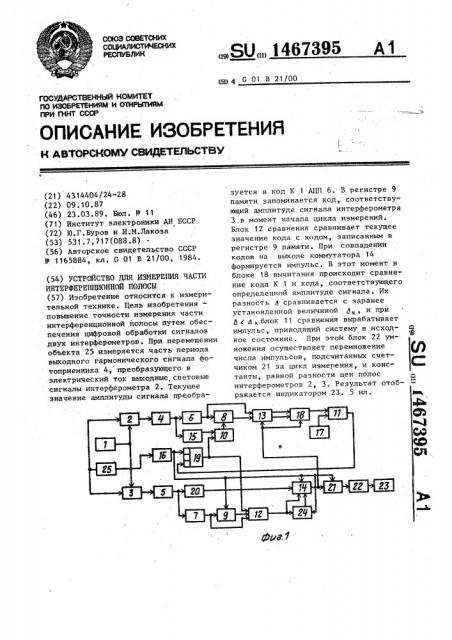

Цель изобретения — повышение точ- 10 ности измерения части интерференционной полосы путем обеспечения цифровой обработки сигналов двух интерферометров. йа фиг. 1 приведена структурная 15

I схема устройства для измерения части интерференционной полосыу на фиг. 2диаграммы сигналов, поясняющие его работу; на фиг. 3 — функциональная схема второго формирователя; на 20 фиг. 4 — функциональная схема второго

| коммутатора; на фиг. 5 — временные диаграммы его работы.

Устройство содержит источник 1 монохроматического излучения, интерферометр 2, интерферометр 3 с регулируемой ценой полосы, фотоприемники

4 и 5, аналого-цифровые преобразователи 6 и .7, регистры 8 и 9 памяти, логический элемент И 10 блоки 11 и 12 сравнения, коммутаторы 13 и 14, формирователи 15 и 16, шифратор 17, блок 18 вычитания, триггер 19, блок 20 определения экстремума, счетчик

21, блок 22 умножения, индикатор 23 и делитель 24 частоты, объект 25.

Формирователь 15 (фиг. 3) состоит из индикатора 26 нуля, D-триггера 27, включенного по счетному входу, логического элемента ИЛИ 28, включенного 40 таким образом, что сигнал на его выходе повторяет сигнал на его входе (т.е. выполняющего роль линии задержки) и логического элемента И 29.

Триггер 27, логический элемент ИЛИ 2845 и элемент И 29 выполняют функцию делителя 30 частоты.

Коммутатор 14 (фиг. 4), построенный в предположении, что длительность импульсов, поступающих на его входы

Упр.вх., Вх.1 и Вх.2, одинакова, содержит логический элемент 3 1

ИСКЛЮЧАЮЩЕЕ ИПИ, триггер 32, два логических элемента И 33 и 34, логический элемент ИЛИ 35 и выполняющий роль линии задержки логический элемент ИЛИ 36.

С перемещающимся объектом 25 свя- заны подвижные части интерферометра

2 и интерферометра 3 с регулируемой ценой полосы. На оптическом выходе интерферометра 2 установлен первый фотоприемник 4, а на оптическом выходе интерферометра 3 — второй фотоприемник 5. К первому фотоприемнику 4 подключен первый аналого-цифровой ,преобразователь 6, выход которого связан с информационными входами первого регистра 8 памяти и первого коммутатора 13. Второй информацион/ ный вход коммутатора 13 связан с выходом регистра 8 памяти, а его выходы — с информационными входами блока 18 вычитания. Выход блока 18 вычитания соединен с первым информа- ционным входом первого блока 11 сравнения, выход шифратора 17 — с вторым информационным входом первого блока 11 сравнения, а его выход подключен к входу Установка нуля триггера 19. Вход "Установка нуля" этого триггера связан с выходом первого формирователя 16, входами "Установка п нуля счетчика 21, второго коммутатора 14 и делителя 24 частоты и управляющим входом регистра 9 памяти. Вы" ход триггера 19 подключен к первому входу логического элемента И 10 и первому входу блока 12 сравнения..

Вторые входы элемента И 10 и блока 12 сравнения соединены соответственно с выходами формирователя 15 и регистра

9 памяти, а третий вход блока 12 связан с выходом аналого-цифрового преобразователя 7 и информационным входом регистра 9 памяти. Выход блока 12 соединен с первым информационным входом коммутатора 14 и входом делителя 24.частоты, выход которого связан с вторым информационным входом коммутатора 14. Выход этого каммутатора подключен к управляющим входам коммутатора 13 и блока 18 вычитания и информационному входу счетчика 21 последовательно с которым включены блок 22 умножения и индикатор 23 .

Управляющий вход коммутатора 14 соединен с выходом блока 20 определения экстремума, а вход этого блока — с выходом фотоприемника 5 и входом аналого-фицрового преобразователя

Вход формирователя 15 подключен к выходу фотоприемника 4, а формирователь 16 своим входом связан с перемещающимся объектом 25.

Устройство работает следующим образом, 1467395

Перед измерением оно приводится в исходное состояние, при котором на выходе триггера 19 находится уро1 вень логического нуля. На структурной схеме устройства (фиг. I} шина уста5 новки триггера в исходное состояние не обозначена.

Интерферометр 3 регулируется таким образом, что цена 1 z его интерференционной полосы незначительно меньше цены 1 интерференционной полосы интерферометра 2.. На выходе шифратора 17 устанавливается определенный постоянный код, который определяется 15 величиной погрешности, допустимой при данном измерении.

В процессе линейного перемещения объекта 25 одновременно с ним перемещаются подвижные части интерферометра 20

2 и интерферометра 3 с регулируемой ценой полосы. Фотоприемники 4 и 5 преобразуют световые сигналы с соответствующих интерферометров 2 и 3 в гармонические электрические сигналы 25 (диаграммы 4 и 5 на фиг. 2), периоды следования которых соответствуют ценам 1.„ и 1 интерференционных полос,указанных интерферометров.

Аналого-цифровые преобразователи 30

6 и 7 осуществляют постоянное преобразование поступающих на их входы синусоидально изменяющихся напряжений .в цифровые коды,.

Блок 20 определения экстремума формирует короткие прямоугольные импульсы при достижении электрическими сигналами, поступающими на его вход, максимальных и минимальных значений. а

Формирователь 15 предназначен для формирования коротких прямоугольных масштабных импульсов (ИИ), период следования которых соответствует периоду следования интерференционных 45 полос интерферометра 2, причем их появление свидетельствует об бкончании этого периода (диаграмма 15 на фиг. 2). Формирование ИИ может быть привязано к произвольному уровню 50 электрического сигнала фотоприемника

4, например, максимальному и минимальному значениям, моменту пересечения нулевого значения и т,д. В данной реализации формирователь 15 вы- 55 дает ИИ при прохождении гармонического сигнала на его входе через нулевое значение, хотя это может быть и любой его уровень.

Формирователь 15 работает следующим образом. Индикатор 26 нуля формирует короткие импульсы всякий раз при прохождении гармонического сигнала на его входе через нулевое значение, Однако на одном периоде гармонического сигнала есть две точки с нулевой амплитудой. Делитель 3Q частоты с емкостью два из каждых двух импульсов, поступающих на его вход, формирует один импульс, совпадающий по времени с вторым импульсом на его входе. Пусть при включении питания устройства триггер 27 приводится в исходное нулевое состояние (подачей соответствующего сигнала по шине установки в исходное состояние; подключенной к его К-входу). Тогда ,на его инверсном выходе будет уровень логической единицы. При поступлении первого импульса на его счетный вход триггер 27 переключится и на его инверсном выходе станет уровень логического нуля. Поэтому первый импульс, пройдя через логический элемент ИЛИ 28 с задержкой, превышающей время переключения триггера 27, не пройдет через логический элемент И 29 на выход формирователя. Второй импульс индикатора 26 нуля снова переключит триггер

27, который разрешит работу логического элемента И 29, вследствие чего. этот импульс пройдет на выход формирователя 15.

Ф

Первый коммутатор 13 предназначен для управления прохождением информа.= ции в виде кодов с его двух информационных входов на два информационных выхода. Управление осуществляется подачей короткого прямоугольного синхроимпульса на его управляющий вход, при этом в течение длительности, 1 этого импульса информация в цифровых кодах, присутствующая на двух его информационных входах, передается на его соответствующие информационные выходы.

Коммутатор 14 осуществляет управление прохождением на его выход коротких прямоугольных импульсов, поступающих на два его информационных входа. Если моменты проходов сигналов с выхода второго блока 12 сравнения на его первый информационный вход совпадают с моментами поступления сигналов блока 20 определения экстремума на его управляющий вход, то на выход коммутатора 14 проходят сигналы

1467395 с его первого информационного входа. в противном случае на выход коммутатора 13 проходят сигналы с второго

его информационного входа (с выхода

;делителя 24 частоты). Перед каждым

1 циклом работы коммутатора 15 он приводится в исходное состояние подачей короткого импульса на его вход установки (Вх.уст. нуля) . При этом триггер 32 устанавливается в такое состояние, при котором на его прямом вы1 ходе — уровень логического нуля, а на инверсном — уровень логической

1 единицы. При совпадении во времени

1 ,,:сигналов на входах-Упр.вх. и Вх.t ( (первая часть диаграмм Упр.вх. и

iBx.1 на фиг. 5) сигналы на выходе логического элемента 31 ИСКЛЮЧАЮП ЕЕ

ИЛИ отсутствуют (диаграмма 31), триг- 2о гер 32 остается в исходном состоянии (диаграмма 32 иллюстрирует уровень сигнала на erо прямом выходе, а 32 на инверсном). В этом случае управляемый триггером 32 логический элемент 25 ..И 37 открыт, а элемент И 34 закрыт; ,поэтому на выход коммутатора через элемент ИЛИ 35 проходят. сигналы с E первого входа Вх. 1 коммутатора (диаграмма 35). Если же сигналы на входах д0

Упр.вх. и Вх.1 не совпадают во време.ни (вторая часть диаграммы Упр,вх. .и Вх. 1), логический элемент 31

ИСКЛЮЧАЮЩЕЕ ИЛИ формирует импульсы в те же моменты, когда только на одном из его входов присутствует уровень логической единицы. Первым же выходным импульсом этого элемента триггер 32 переключится в состояние, противоположное исходному, и запретит работу логического элемента И 33, одновременно разрешив работу элемента

И 34. При этом на выход коммутатора через элементы И 34 и ИЛИ 35 пойдут сигналы с его входа Вх.2. Линия Зб 45 задержки необхолима для задержания прохождения сигналов с входа Вх.1 на элемент И 33 на время переключения триггера 32 в том случае, когда сигналы на вход Вх.1 приходят раньше 50 сигналов на вход Упр.вх.

Блок 18 вычитания осуществляет вычисление разности кодов, поступающих на два его информационных входа.

Операция вычитания осуществляется под управлением синхроимпульса, поступающего на его управляющий вход.

В течение длительности этого импульса на его выходной шине формируется код разности кодов, поступающих в это время на два его информационнык входа, все же остальное время на его выходе постоянно удерживается код максимально большого числа, реализуемого при данном используемом числе разрядов выходной шины блока 18 вычитания (такой режим работы реализуется стандартным включением микросхем арифметико-логического устройст- ва К155 ИПЗ, на которых построен блок 1.8).

Шифратор 17 предназначен для постоянного формирования на своем выходе константы, выраженной в цифровом коде.

Первый блок 11 сравнения предназначен для получения информации о сравнительной величине кодов, поступающих на два его информационных входа . Он осуществляет проверку условия того, что код на первом его входе меньше или равен коду на втором его информационном входе. При выполнении этого условия он формирует короткий прямоугольный импульс.

Делитель 24 частоты аналогичен делителю 30, представленному на фиг. 3. Вход установки нуля делителя

24 — это R-вход триггера 27.

Формирователь 16 осуществляет формирование короткого прямоугольного командного импульса, по которому начинается цикл измерения части периора гармонического сигнала интерферометра 2.

Момент подачи командного импульса формирователем 16 может быть любым.

Например, он может определяться оператором вручную подачей соответствующего управляющего сигнала на его вход. Этот управляющий сигнал может формироваться и каким-либо внешним устройством. В данной реализации устройства измерения части интерференционной полосы момент фор.- . мирования командного импульса формирователем 16 привязан к моменту прохождения объектом 25 определенной точки вдоль траектории его перемещения, при этом формирователь 16 реализован по схеме, представленной на фиг. 3, и связан с перемещающимся объектом 25, Этот командный импульс (диаграмма 16 на фиг, 2) поступает на входы установки нуля счетчика 21, записывая в него нуль; коммутатора

14 и делителя 24 частоты, подготав1467395 !О

5 !

45 ние. Уровень логического нуля, формируемый при этом триггером 19, запрещает дальнейшую работу логического элемента И 10 и блока 12 сравнения, Выполнение указанного условия означает нониусное сопряжение кодов

К1(А1,.) и К1(А1(МИ)). До момента этого нониусного сопряжения на. информационный вход счетчика поступит и импульсов коммутатора 14 (диаграмма

14). Информация об измеренной величине D части гармоничного сигнала интерферометра 2, отсчитываемой от предыдущего по отношению к командному импульсу МИ до командного им пульса (т.е. об измеренной части интерференционно." полосы), формируется а выходе блока 22 умножения, который осуществляет умножение этого числа на KQHcTBHTy равную (1 1 <) ° Полученный результат отображается индикатором 23.

Выполнение условия К1 (А1 )

= Ы! (А1(МИ)) при измерении части D интерференционной полосы нониусным методом возможно лишь в том случае, если она кратна целому числу разностей цен 1, и 1 интерференционных полос интерферометров 2 и 3.

Вследствие случайного характера момента формирования командного им.пульса действительный размер части интерференционной полосы может быть не равен целому числу разностей цен полос интерферометров. Тогда при нониусном сопряжении условие К1 (A1.)

= К1 (А1(МИ)) в моменты появления кода К2 выполняется не точно, а приближенно. Оценим величину этого приближения.

При первом появлении на выходе коммутатора 14 сигнала, ооответствующего коду К2 (А2), точка A1 на выходном сигнале фотоприемника 4 сдвинута во времени от точки А1 (МИ) ,на величину, пропорциональную

D-(1„- 1 ), при следующем — на величину, пропорциональную D-2(1, — 1g), при следующем — на D-3(1, — 1 ) и т.д. Это обусловлено тем, что период выходного сигнала фотоприемника 5 меньше периода выходного сигнала фотоприемника 4 на величину, пропорциональную (1„- 1 ) и равную (1z-1 ) /V, где V — скорость перемещения объекта 25.

При неточном выполнении равенства

D = пТ,1 -1 ), где и = 1, 2, 3..., нониусное сопряжение кодов К1(А1 ) и (К1 (А1 (МИ) ) должно фиксироваться тогда, когда разность (D-nd) будет минимальна (Л = 1 — 1 ) . Наихудшим случаем будет тот случай, когда (D — n Ь) = (D — (п+1)) = Л/2. Значит, можно утверждать, что нониусное сопряжение кодов К1(А1;) и К1(А1(МИ)) должно быть зафиксировано тогда, когда (D — n 8.) 4 8 /2.

Величина, соответствующая абсолютному значению разности К1(А1(МИ)) и кода, определяющего амплитуду сигнала фотоприемника 4, проекция которой на ось абсцисс удалена от проекции амплитуды А1(МИ) на ту же ось на

Д/2 V, равна Д . При различных значениях уровня А1(МИ) величина Д „ может быть разной, но она,однозначно соответствует тому значению А1(МИ), которое выбрано в конкретной реализации устройства, и не зависит от Ч.

Необходимое для данной реализации устройства значение d к формируется шифратором 17 и устанавливается на нем перед измерениями. Тогда совершенно ясно, что момент наступления неравенства (и — n 4) /? аналогичен наступлению такого момента времени, когда при появлении на выходе коммутатора 14 импульса, соответствующего наличию на выходе фотоприемника 5 амплитуды А2 гармонического сигнала, текущее значение кода К1(А1;), формируемого аналого-цифровым преобразователем 6, отличается от кода

К1(А1(МИ)) MH на величину, не превышающую Д к, т.е.

К1(А1 ) C К1(А1(МИ)) + йк, откуда и вытекает неравенство, выполнение юоторого проверяется блоком 11 сравнения, Устройство может измерять как часть интерференционной полосы, так и дробную часть интерференционной полосы. Во втором случае число и в блоке 22 умножения необходимо умножать на константу а /1

После того, как выходным сигналом блока !1 триггер 19 сбрасывается в исходное состояние и блок 22 умножения осуществляет арифметическую операцию умножения накопленного в

1467395 ливая их к работе, и на управляющий

1 вход регистра памяти. По нему в, указанный регистр заносится цифровой код К2, находящийся в этот момент времени на выходе аналого-цифрового преобразователя 7 и соответствующий мгновенной амплитуде А2 выходного сигнала интерферометра 3. Одновременно этот импульс переключает триггер

19, в результате чего на его выходе появляется уровень логической единицы. Он поступает на первые входы логического элемента И 10 и блока 12 сравнения, являясь для них сигналом разрешения их работы. После прихода этого уровня элемент И 10 формируе-. короткий импульс всякий раз при приходе на другой его вход 1È с формирователя 15 )диаграмма 10, фиг. 2), 20 а блок 12 сравнения формирует короткий импульс всякий раз, когда цифровой код на выходе аналого-цифрового преобразователя 7 совпадает с кодом

К2 (А2), хранящимся в регистре 9 25 памяти (диаграмма 12). На одном периоде сигналов интерферометра 3 может быть два или одно значение амплитуды

А2 (в зависимости от того, совпадает оно с экстремальными значениями 30 амплитуды или нет) . Поэтому коммутатор 14, управляемый сигналами блока

20 определения экстремума, формирует прямоугольный выходной сигнал каждый раз при формировании сигнала блоком

12 сравнения или через раз. Если моменты прихода на первый информационный вход коммутатора 14 сигналов с блока 12 сравнения совпадают с моментами поступления на его управляющий 40 вход выходных импульсов блока 20 определения экстремума (т.е. значение

А2 совпадает с экстремальным значением амплитуды выходного сигнала фотоприемника 5), то на выход этого коммутатора 14 проходят сигналы с его первого информационного входа (т.е. выходные сигналы блока 12 сравнения).

Если же моменты прихода на первый информационный вход коммутатора 14 сиг-5 налов с блока 12 сравнения не совпадают с. моментами поступления на его управляющий вход выходных импульсов блока 20 определения экстремума, на выход этого коммутатора 14 проходят сигналы с второго его информационного входа,- т.е. выходные сигналы делителя

24 частоты, осуществляющего деление частоты на 2, так как зафиксированное в регистре 9 памяти значение

А2 амплитуды не совпадает с экстремальным значением амплитуды выходного сигнала фотоприемника 5.

В данном случае выполняется второе условие, поэтому на выход коммутатора 14 поступают сигналы с выхода ,делителя 24 частоты (диаграмма 14

1на фиг. 2).

Первый же ИИ, появившийся на на выходе элемента И tO, поступает на управляющий вход регистра 8 памяти и переписывает в него код К 1, соответствующий амплитуде А 1.(ИИ), т.е. амплитуде, при которой формирователем 15 формируется МИ. Постоянный код К 1 (А 1 (ИИ)) и переменный код соответствующий мгновенному значению амплитуды выходного сигнала фотоприемника 4, поступают на два информационных входа коммутатора 13. В момент прихода на вход управления этого коммутатора 13 синхроимпульса с выхода коммутатора 14 и в течение времени, равного длительности этого синхроимпульса, коды с информационных входов коммутатора 13 проходят на его выходы и поступают в блок 18 вычитания. Таким образом, на информационных входах блока 18 вычитания в моменты времени, соответствующие появлению один раз в период на выходном гармоническом сигнале фотоприемника 5 запомненной под действием командного импульса амплитуды А2, появляются коды К1 (А1) и K1(A1 (ГЯ) ) .

Вследствие разницы величин периодов сигналов интеферометров 2 и 3

К1)А1о) + К1(А1 ) + Ki (Aig) + . . ° .

Блок 18 осуществляет их вычитание, в результате чего на первый информационный вход первого блока 11 сравнения в течение длительности синхроимпульса на управляющем входе блока 18 поступает код разности К1(А1;)-К1(А1(ИИ)), а на другой вход — код постоянного числа d, формируемый, шифратором 17. Блок 11 сравнения анализирует относительную величину кодов на его информационных входах.

При выполнении условия

К1(А1;) — К1 (А1(ИИ) ) < 3 g он формирует короткий импульс (диаграмма 11 на фиг. 2), поступающий на вход "Установка нуля" триггера 19 и сбрасывающий его в исходное состоя14673 счетчике 21 числа на константу, устройство заканчивает один цикл измерения и готово к следующему циклу, началом которого служит выработка

5 формирователем 16 следующего командного импульса. Результат измерения отображается индикатором 23.

Формула изобретения 1р

Устройство для измерения части интерференционной полосы, содержащее оптически связанные источник монохроматического излучения, первый 15 интерферометр и первый фотоприемник, оптически связанные с источником излучения второй интерферометр с регулируемой ценой полосы и второй фотоприемник, первый и второй анало- 2р го-цифровые преобразователи,.входы которых связаны соответственно с выходами первого и второго фотоприемников, первый и второй блоки сравнения, первый и второй коммутаторы, 25 первый и второй регистры памяти, первый и второй формирователи, блок определения экстремума, логический элемент И, триггер, делитель частоты, последовательно соединенные счетчик, 3р блок умножения и индикатор, второй аналого-цифровой преобразователь, . второй регистр памяти, второй блок сравнения и второй коммутатор.соединены последовательно, вход счетчика

I соединен с выходом второго коммутатора, второй вход второго блока сравнения соединен с выходом второго аналого-цифрового преобразователя, первый вход делителя частоты соединен 4р с выходом блока сравнения, а выход—

95 12 с вторым входом второго коммутатора, второй формирователь соединен с вторым входом счетчика, .выход блока выделения экстремума соединен с третьим входом второго коммутатора, выход второго фотоприемника соединен с входом блока выделения экстремума, о тл и ч а ю щ е е с я тем, что, с целью повышения точности, оно снабжено блоком вычитания и шифратором, первый аналого-цифровой преобразователь, первый регистр памяти, первый коммутатор, блок вычитания и первый блок сравнения соединены последовательно, выход первого аналого-цифрового преобразователя соединен с вторым входом первого коммутатора, второй выход которого соединен с вторым входом блока вычитания; третий вход которого соединен с третьим входом первого коммутатора и выходом второго коммутатора, выход первого фотоприемника соединен с входом первого формирователя, выход которого соединен с первым входом логическбго элемента И, второй вход которого соединен с выходом триггера и третьим входом второго блока сравнения, а выход элемента И - с вторым входом первого регистра памяти, второй вход первого блока сравнения соединен с выходом шифратора, а выход — с

К-. входом триггера, выход второго формирователя соединен с S-входом триггера, вторым входом второго регистра памяти, вторым входом делителя частоты и четвертым входом второго коммутатора, а вход второго формирователя предназначен дпя связи с объектом измерения.

1467395

Упр.

Вх.

Вх!

Фиг. 5

Составитель В. Козлов

Редактор Л. Гратилло Техред М.Дидык Корректор M. Шароши

Заказ 1184/37 Тираж б83 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГЕНТ СССР

)13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101