Одноразрядный комбинационный двоичный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для построения сумматоров с последовательнь1М переносом. Цель изобретения - упрощение сумматора. Он содержит элементы ИЛИ 1,2,3, входы которых попарно соединены с входами 9, 10, 11 двух операндов и переноса сумматора. Новым в сумматоре является то, что выходы элементов ИЛИ 1,2,3 объединены монтажно в элемент И 7 и соединены с выходом 13 переноса сумматора. Сумматор содердит. элементы И-НЕ 4, И-НЕ 5, ИЛИ 6, причем выходы элементов И-НЕ 5 и ИЛИ 6 также объединены монтажно в элемент И 8 и соединены с выходом 12 суммы сумматора. 1 ил. 1 табл. i (Л сд СП со и

Ъ

5 Д1 сооз советсних социАлистичесних

РЕСПУ1ЬЛИН

П9) (И) 15 4 G 06 F.7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ дО изоиетениям и отнРытиям

АрН Гннт сссР (21) 4249025/24-24. (22). 25.05.87 (46) 23.03.89, Бюл, У 11 (71) Одесский электротехнический институт связи им.А.С.Попова (72) А.А.Полянский и О.М.Зощенко (53) 681.325.5 (088.8) (56) Авторское свидетельство СССР

У 1105887, кл. С 06 F 7/50, 1982.

Пучко А.Н. и др. Электронные цифровые вычислительные машины; М.:

Машиностроение, 1979, с.105, рис.37. (54) ОДНОРАЗРЯДНЫЙ КОМБИНАЦИОННЫЙ

ДВОИЧНЫЙ СУММАТОР (57) Изобретение относится к вычислительной технике и может быть использовано для построения сумматоров с последовательным переносом. Цель изобретения — упрощение сумматора.

Он содержит элементы ИЛИ 1,2,3, входы,соторых попарно соединены с входами 9, 10 11 двух операндов и переноса сумматора. Новым в сумматоре является то, что выходы элементов

ИЛИ 1,2,3 объединены монтажно в элемент И 7 и соединены с выходом 13 переноса сумматора. Сумматор содержит. элементы И-НЕ 4, И-НЕ 5, ИЛИ 6, причем выходы элементов И-HE 5 и

ИЛИ 6 также объединены монтажно в элемент И 8 и соединены с выходом

12 суммы сумматора. 1 ил. 1 табл. 1467553

Изобретение относится к вычислительной технике и может быть использовано для построения сумматоров с последовательным переносом.

Цель изобретения — упрощение сумматора.

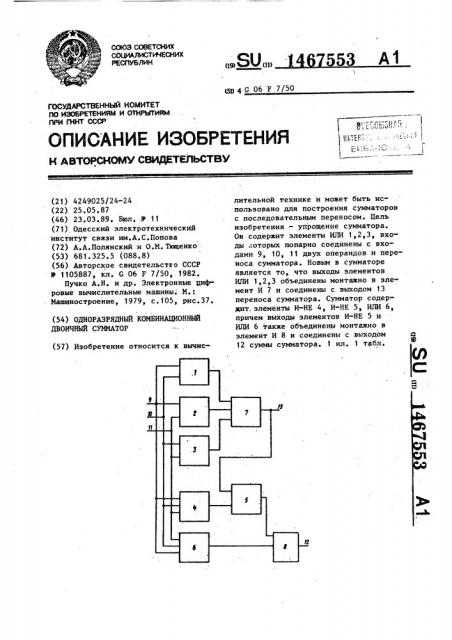

На чертеже представлена функциональная схема сумматора.

Сумматор содержит три элемента

ИЛИ 1-3, элемент И-НЕ 4„ элемент

И-НЕ 5, элемент ИЛИ 6, элементы И 7, 8 (выполненные монтажно)., входы 9 и 10 операндов х, у сумматора, вход

11 переноса с, выход l2 суммы S u выход 13 переноса с сумматора.

Формула. изобретения

Одноразрядный комбинационный двоичный сумматор, содержащий четых у с 1 2 3 4 5 б с S

О О

О 1

О 1

1 О

О 1

1 0

1 1

О О О О 1 1 О

О, 1 1 О 1 1 1

О 1 0 1 1 1

О 1 1 1 1 О 1

1 0 1 1 1 1

1 1 1 1 1 О 1

1 1 1 1 1 О- 1

1 1 1 1 О 1 1

О О

1 О

О, 1

1 1

О О

1 О

О 1

1 1

Составитель А.Клюев

Техред А.Кравчук Корректор М.Пожо

Редактор В.Данко

Заказ 1196/45 Тираж 667 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101

В таблице представлены состояния на выходах элементов и на выходах переноса с и суммы S сумматора в

1 зависимости от состояния íà его входах: первого операнда х, второго операнда у и переноса с.

Сумматор может быть реализован на элементах логических серий, объединение по выходу которых реализует функцию монтажного И, т.е. на объе.-., диненном выходе логических элементов ,логическая единица устанавливается только в том случае, если на выходе каждого из логических элементов в отдельности должна установиться логическая единица. ре элемента ИЛИ, два элемента И, причем первый вход первого элемента

ИЛИ соединен с SxopoM первого one5 ранда сумматора второй вход первого

Э элемента ИЛИ соединен с входом второго операнда сумматора, первый вход второго элемента ИЛИ соединен с входом первого операнда сумматора, второй вход второго элемента ИЛИ соеди нен с входом переноса сумматора, первый вход третьего элемента ИЛИ соединен с входом второго операнда, сумматора, второй вход третьего элемента ИЛИ соединен с входом переноса сумматора, выходы первого, вто рого и третьего элементов ИЛИ подключены к входам первого элемента

И, выход которого соединен с выходом переноса сумматора, входы четверто о элемента ИЛИ соединены с входами, первого и второго операндов и переноса сумматора, выход четвертого элемента ИЛИ соединен с первым входом .второго элемента И, выход которого соединен с выходом суммы сумматора, отличающийся тем, что, с целью упрощения, в сумматор введены . два элемента И-НЕ, а элементы И выполнены монтажными, причем входы первого элемента И-НЕ подключены к входам первого и второго операндов и переноса сумматора, а выход подключен к первому входу второго элемента И-НЕ, второй вход которого соединен с выходом первого элемента И, а выход, — с вторым входом второго элемента И.