Резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

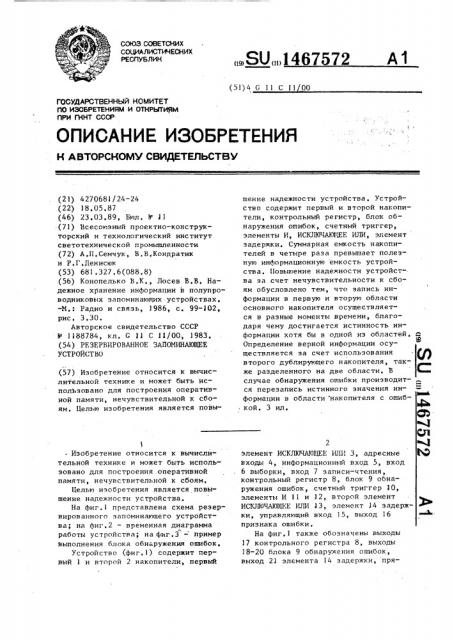

Изобретение относится к вычислительной технике и может быть исполЬзовано для построения оперативной памяти, нечувствительной к сбоям . Целью изобретения является повы - Изобретение относится к вычислительной технике и может быть использовано для построения.оперативной памяти, нечувствительной к сбоям. Целью изобретения является повышение надежности устройства. На фиг,1 представлена схема резервированного запоминающего устройства; на фиг.2 - временная диаграмма работы устройства; на фиг.3 - пример Выполнения блока обнаружения ошибок. Устройство (фиг.1) содержит первый 1 и второй 2 накопители, первый шение надежности устройства. Устройство содержит первый и второй накопители , контрольный регистр, блок обнаружения ошибок, счетный триггер, элементы И, ИСКЛЮЧАЮ1ЦЕЕ ИЛИ, элемент задержки. Суммарная емкость накопителей в четыре раза превышает полезную информационную емкость устройства . Цовыв ение надежности устройства за счет нечувствительности к сбоям обусловлено тем, что запись информации в первую и вторую области основного накопителя осуществляется в разные моменты времени, благодаря чему достигается истинность информации хотя бы в одной из областей. Определение верной информации осуществляется за счет использования второго дублирующего накопителя, также разделенного на две области. В случае обнаружения ошибки производится перезапись истинного значения информации в области накопителя с ошибкой . 3 ил. i элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, адресные входы 4, информационный вход 5, вход 6 выборки, вход 7 записи-чтения, контрольный регистр 8, блок 9 обнаружения ошибок, счетный триггер 10, элементы И 11 и .12, второй элемент ИСКЛЮЧАЮВЩЕ ИЛИ 13, элемент 14 задержки , управляющий вход 15, выход 16 признака ошибки. На фиг.1 также обозначены выходы 17 контрольного регистра 8, выходы 18-20 блока 9 обнаружения ошибок, выход 21 элемента 14 задержки, пря (Л 4 О М ел - to

СОВХОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1467572

А1 (51)4 G 11 С ll 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3, адресные Ь ) входы 4, информационный вход 5, вход

6 выборки, вход 7 записи-чтения, контрольный регистр 8, блок 9 обнаружения ошибок, счетный триггер 10, элементы И 11 и 12, второй элемент

ИСКЛЮЧАЮЩЕЕ ИЛИ l 3,,элемент 14 задержки, управляющий вход 15, выход 16 признака ошибки, На фиг.1 также обозначены выходы

17 контрольного регистра 8, выходы

18-20 блока 9 обнаружения ошибок, выход 21 элемента 14 задержки, пряГОСУДАРСТ8ЕННЫЙ ХОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4270681/24-24 (22) 18,05.87 (46) 23,03,89, Бюл. М )l (71) Всесоюзный проектно-конструкторский и технологический институт светотехнической промышленности (72) А.П.Семчук, В ° В,Кондратик и Р.Г,Денисюк (53) 681,327.6(088.8) (56) Конопелько В.К., Лосев В.В. Надежное хранение информации в полупроводниковых запоминающих устройствах.

-M. Радио и связь, 1986, с. 99-102, рис. 3.30.

Авторское свидетельство СССР

М 1188784, кл. С ll С 11/00, 1983. (54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть исполЬзовано для построения оперативной памяти, нечувствительной к сбоям. Целью изобретения является повы1

- Изобретение относится к вычислительной технике и может быть использовано для построения оперативной памяти, нечувствительной к сбоям, Целью изобретения является повышение надежности устройства.

На фиг,l представлена схема резервированного запоминающего устройства; на фиг.2 — временная диаграмма

I работы устройства; на фиг,3 - пример выполнения блока обнаружения ошибок, Устройство (фиг,l) содержит первый 1 и второй 2 накопители, первый шение надежности устройства. Устройс тво содержит первый и в торой накопители, контрольный регистр, блок обнаружения ошибок, счетный триггер, элементы И, ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент задержки, Суммарная емкость накопителей в четыре раза превышает полезную информационную емкость устройства, Повышение надежности устройства за счет нечувствительности к сбоям обусловлено тем, что запись информации в первую и вторую области основного накопителя осуществляется в разные моменты времени, благодаря чему достигается истинность информации хотя бы в одной из областей. с

<0

Определение верной информации осуществляется за счет использования второго дублирующего накопителя, также разделенного на две области. В случае обнаружения ошибки производится перезапись истинного значения ин3®ае4 формации в области накопителя с ошибкой. 3 ил.

1467572 мой выход 22 счетного триггера 10.

Контрольный регистор 8 состоит из триггеров 23.

Блок 9 обнаружения ошибок (фиг.3) содержит программируемую логическую матрицу 24 и ключ 25 с тремя состояниями, Резервированное запоминающее устройство работает следующим образом. 10

Режим записи. На адресные входы

4, информационный вход 5, вход 6 выборки, вход 7 запись-чтение, управляющий вход 15 поступают логические уровни (фиг.2). При этом уровень ло- 15 гического нуля на первом входе второго элемента ИСКЛЮЧА10ЩЕЕ ИЛИ 13 приводит его в режим повторения логических уровней, поступающих на его второй вход 22, После смены адреса на 20 адресных входах 4 и установления данных на информационном входе 5 уровнем логического нуля на входе 6 выборки производится запись информации в первый 1 и второй 2 накопители. Положительным перепадом напряжения на входе 6 выборки триггер 10 переводится в другое устойчивое состояние и уровнем логического нуля на входе 6 выборки производится повторная запись информации, установленной на информационном входе 5, во второй квадрат первого 1 и второго 2 накопителей, При этом на этом выходе 20 блока 9 обнаружения ошибок установлен уровень логического нуля.

Блок 9 реализует следующие функции (фиг.3):

Y 1 = X2,ХЭ,Г5.Х6; Y 2 = (X2 X3+X? ХЗ ) . Х5. Х6. =Х2. Х5. Х6; 40

Y 3 = Х2,ХЗ.Х5,Х6;

Y 4 = (Х1,X3+X2.ХЗ.Х4).X5 ° X6=0;

Y 4 — третье состояние;

Y 5 = Х6+(Х2,Х3+ХХ.X3),Х5.Х6, 45

Таким образом, н режиме записи обеспечивается разнесенная по времени запись информации, устанавливаемой на информационном входе 5, в две области памяти первого 1 и второ-50 го 2 накопителей для каждого адреса, устанавливаемого на адресных входах

4. Уровень погического нуля, устанавливаемый на входе 7 записи-чтения, блокирует первый 16, второй 19, третий 18 выходы блока 9 обнаруже-! ния ошибок, а на информационном выходе 5 блока 9 устанавливает высокоимпедансное состояние.

Режим чтения, На адресные входы

4, вход 6 выборки, вход 7 записи1 чтения управляющий вход 15 поступают логические уровни (фиг.2) . При этом уровень логической единицы на входе 7 записи-чтения переводит второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13 в ре" жим инвертирования логических уровней, поступающих на его второй вход.

Следовательно, при считывании проис ходит обработка информации, записанной в разные моменты времени. После установки адреса на адресных входах

4 высокий логический уровень, установленный на. входах 15, устанавливает на третьей l8 и втором 19 выходах блока 9 обнаружения ошибок нулевые логические уровни, разрешающие триггеру 1 0 счет импульсов, поступаю- ° щих на его синхронизирующий вход.

На пятом выходе 20 блока 9 устанавливается уронень логической единицы, устанавливающий первый l и второй

2 накопители в режим чтения. По приходу отрицательного импульса на входы выборки первого 1 и второго 2 накопителей на их выходах устанавливается информация, записанная в одну из областей памяти (в зависимости от состояния триггера )0) по адресу, установленному на адресных входах 4, Элемент 14 задержки задерживает передний фронт отрицательного импульса (фиг.?), поступающего на его вход на время, достаточное для окончания переходных процессов н первом 1 и втором 2 накопителях, и инвертирует импульс.

На первый и четвертый информационные входы контрольного регистра 8 поступает информация с выходов первого 1 и второго 2 накопителей .

С выхода первого элемента ИСКЛЮЧАЮП1ЕЕ ИЛИ 3 признак совпадения (уронень логического нуля) или несовпадения (уровень логической единицы) информации в первом 1 и втором 2 накопителях поступает на второй и третий информационные входы контрольного регистра 8.

Положительный импульс с выхода 21 элемента 14 задержки н зависимости от состояния триггера 10 ÷åðåç ïåðвый 11 или второй 12 элементы И поступает на первый или второй синхронизирующие входы контрольного регистра 8, производя запись поступающей на его соответствующий информацион5 1 ный вход информации, Положительным перепадом импульса на вход 6 выборки триггер 10 переводится в другое устойчивое состояние и логический уровень с его прямого выхода 22 подготавливает адрес информации, записанной в других областях памяти первого 1 и второго 2 накопителей, Следующим отрицательным импульсом на входе 6 выборки аналогично производится запись информации и признака во вторую полонину контрольного регистра 8. При установке нулевого логического уровня на входе 15 блоком

9 в соответствии с реализуемыми им функциями производится анализ содержащейся в контрольном регистре 8 информации и ныдача соответствующих уп равляющих воздействий. При пранильном считывании информации из обеих областей памяти (нулевые логические уровни на выходах 17< и 17э контроль ного регистра 8) на информационном входе 5 устанавливается логический уровень с выхода 1/, контрольного регистра 8.,Одновременно единичный логический уровень с второго выхода

19 блока 9 устанавливает триггер 10 в нулевое состояние. Третий отрицательный импульс на входе 6 выборки не переводит триггер 10 н единичное

Состояние, так как он удерживается в нулевом состоянии по входу сброса.

Запись информации н контрольный регистр 8 блокируется нулевым логическим уровнем, поступающим на первые входы первого 11 и второго 12 элемен тов И. Ио окончании третьего отрицательного импульса на входе 6 выборки происходит установка нового адреса на адресных входах 4, и запускается новый цикл чтения, При считывании ложной информации из первой области памяти (уровень ло гической единицы на выходе 17 и логического нуля на выходе 17 конт3 рольного регистра 8) на информационном входе 5 устанавливается логический уровень с выхода ll контрольного регистра 8, Одновременно единичный уровень второго выхода 19 блока

9 устанавливает триггер 1,0 в нулевое состояние, На пятом выходе,20 блока

9 устанавливается единичный логичесl кий уровень, переводящий первый l u второй 2 накопители в режим записи.

Третьим отрицательным импульсом на шине 6 разрешения выборки производит

467572 6 ся перезапись информации н первую область памяти первого 1 и второго 2 накопителей (при уровне логического нуля .на прямом выходе 22 триггера 10)

Ири считывании ложной информации нз второй области памяти (уровень логической единицы на выходе 17> и логического нуля на ныходе l/ конт-рольного регистра 8) на информационf ной шине 5 устанавливается логический уровень с выхода l/„ контроль ного регистра 8, Одновременно единичный логический уровень с третьего выхода l8 блока 9 устанавливает триг гер 1,0 в единичное состояние, На пятом ныходе 20 блока 9 устанавливается единичный логический уровень, переводящий первый 1 и второй 2 нако2р пители в режим записи. Третьим отрицательным импульсом на входе. 6 выборки производится перезапись информации во вторую область памяти первого 1 и второго 2 накопителей (при

25 уровне логической единицы на прямом выходе 22 трит гера 10).

Ири считывании ложной информации из первой и второй областей памяти (уровни логической единицы на выхо-.

30 дах 1/ и 17 контрольного регистра

i8) на информационном входе 5 уста. навливается нулевой логический уровень, а на выходе 16 блока 9 устанавливается единичный логический уро-, З5 вень, сигнализирующий о сбое памяти, 1

Таким образом, в устройстве обес;печивается запись информации в раз ные области основного накопителя в разные промежутки времени, благодаря чему достигается истинность записан" ной информации хотя бы в одной области накопителя, а также аналогичная запись производится н дублирующий накопитель, Ири считывании информации — 45 обеспечивается определение сбоя хотя бы в одной иэ областей накопителей путем поочередного сравнения .содержимого областей накопителей, информация в которых записана в разные

50 промежутки времени, Благодаря этому повышается надежность определения сбоя информации при считывании. В случае определения сбоя информации при считывании она корректируется по

55 истинной информации, находящейся в других областях памяти. Этим достигается высокая достоверность восстановления истинной информации при наличии сбоев при ее хранении.

Формула

1467 изобретения

Резервированное запоминающее устройство, содержащее первый накопитель, выход которого соединен с первым информационным входом контрольного регистра, выходы которого подключены к входам блока обнаружения ошибок с первого по четвертый, первый выход которого является выходом признака ошибки устройства, первый, и второй элементы И, элемент задержки, вход которого является входом выборки устройства, о:т л и ч а.ю- 1б щ е е с я тем, что, с целью повышения надежности устройства, в него введены второй накопитель, первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, счетный триггер, причем одни адресные входы первого и второго накопителей являются адресными входами устройства, другой адресный вход первого накопителя соединен с прямым выходом счетного триггера и с пер- 25 выми входами второго элемента И и второго элемента HCKJIIO×ÀI0ÙÅE ИЛИ, выход которого подключен к другому адресному входу второго накопителя, выход которого соединен с четвертым ЗО информационным входом контрольного регистра и с вторым входом первого элемента HCKJIN×ÀÞÙI .Å ИЛИ, первый

572 8. вход которого подключен к выходу первого накопителя, а выход соединен с вторым и третьим информационными входами контрольного регистра, первый и второй синхровходы которого подключены к выходам соответственно первого и второго элементов И, вторые входы которых соединены с выходом элемента задержки, вход которого подключен к синхровходу счетного триггера и к входам выборки первого и второго накопителей, входы записи которых со- единены с пятым выходом блока обнаружения ошибок, второй и третий выходы которого подключены соответственно к входам установки в "0" и "1 счетного триггера, первый вход первого элемента И и, третий вход второго элемента И являются управляющим входом устройства н соединены с пятым входом блока обнаружения ошибок, шестой вход которого подключен к второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является входом записи-чтения устройства, информационные входы первого и второго накопителей являются информационным входом устройства и соединены с четвертым выходом блока обнаружения ошибок, третий вход первого элемента И подключен к инверсному выходу счетного триггера.

1467572

РГ4 й/ . ЗРл lсь