Устройство передачи двоичных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - обеспечение передачи асинхронных сигналов. Устройство содержит источник I цифровых сигналов, источник 2 синхросигналов, блоки задержки 3 и 4, счетные триггеры 5 и 9, эл-т ИСКЛЮЧАЮЩЕЕ ИЛИ 6, мажоритарный блок 7, делитель 8 частоты и согласующий блок Ю. Цель достигается за счет принудительного сбрасывания в «О делителя 8. Это обеспечивает требуемую синхронность работы счетного триггера 9 и поступления входных данных, а в конечном итоге - возможность работы с асинхронной входной информацией. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ÄÄSU ÄÄ 1467782 (5g 4 Н 04 1 25 49

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛВСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4292249/24-09 (22) 30.07.87 (46) 23.03.89. Бюл. № 11 (72) А. Л. Ратанов, Д. М. Манкевич, Ю. К. Гришин и Н. У. Тихова (53) 621.394.62 (088.8) (56) Авторское свидетельство СССР № 1100749, кл. Н 04 L 25/49, 1983. (54) УСТРОЙСТВО ПЕРЕДАЧИ ДВОИЧНЫХ СИГНАЛОВ (57) Изобретение относится к электросвязи. Цель изобретения — обеспечение передачи асинхронных сигналов. Устройство содержит источник 1 цифровых сигналов, источник 2 синхросигналов, блоки задержки

3 и 4, счетные триггеры 5 и 9, эл-т ИСКЛЮЧАЮЩЕЕ ИЛИ 6, мажоритарный блок

7, делитель 8 частоты и согласующий блок

10. Цель достигается за счет принудительного сбрасывания в «О» делителя 8. Это обеспечивает требуемую синхронность работы счетного триггера 9 и поступления входных данных, а в конечном итоге — возможность работы с асинхронной входной информацией. 2 нл.

1467782

1О

1

Изобретение относится к электросвязи и может использоваться в системах передачи дискретной информации.

Цель изобретения — передача асинхронных сигналов.

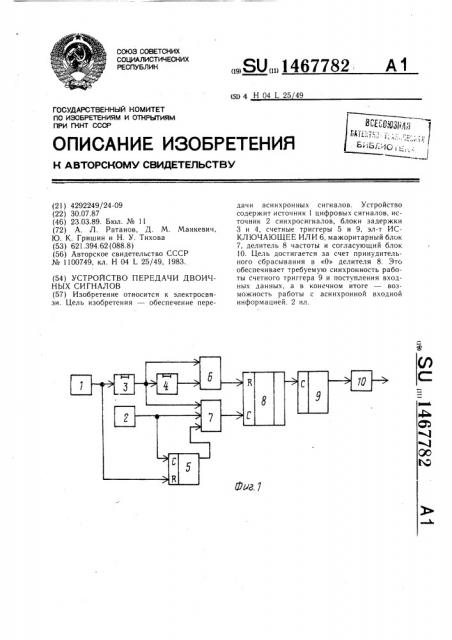

На фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 — временные диаграммы, поясняющие работу устройства.

Устройство содержит источник 1 цифровых сигналов, источник 2 синхросигналов, блоки 3 и 4 задержки, второй счетный триггер 5, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

6, мажоритарный блок 7, делитель 8 частоты, первый счетный триггер 9, согласующий блок 10.

Устройство работает следующим образом.

Цифровой двоичный сигнал (фиг. 2 а), задержанный в блоке 3 (фиг. 2 в), поступает на вход элемента 6 и, после задержки в блоке 4 (фиг. 2 г), на другой вход элемента 6.

Блок 4 и элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ 6 образуют схему детектирования изменений входного сигнала, на выходе которой (фиг. 2 д) формируются короткие импульсы, передние фронты которых совпадают с моментами смены уровня сигнала на выходе блока 3, а длительность определяется задержкой блока 4.

Входной информационный сигнал непосредственно от источника поступает на

R-вход счетного триггера 5, на С-вход которого подается сигнал от источника 2 (фиг. 2 б). Этот сигнал представляет из себя импульсную последовательность, частота которой в 2 "+" раза превышает темп поступления информации от источника 1, где п=1,2... (для большей наглядности на фиг. 2 предствлен случай n=2). Фаза синхросигнала никак не связана с моментами смены значений информационного сигнала, т. е. эти сигналы асинхронны. В качестве источника 2 может использоваться как встроенный, так и внешний генератор тактовых импульсов. Включение счетного триггера 5 определяет его работу как управляемого делителя частоты синхросигнала на два, причем низкий уровень информационного сигнала разрешает деление, а высокий — блокирует его, сбрасывая в «О» триггер 5 (фиг. 2 е).

Совместное включение источника 2, блока 3, счетного триггера 5 и мажоритарного блока 7 обеспечивает формирование на выходе мажоритарного блока 7 импульсной последовательности переменной частоты (фиг. 2 ж). Фаза и длительность формируемых импульсов совпадает с фазой и длительностью синхросигнала от источника 2.

Частота, формируемой последовательности равна частоте синхросигнала в интервалах, когда уровень сигнала на выходе блока 3 соответствует логической единице и вдвое меньше при логическом нуле. Таким образом, 25

2 на выходе мажоритарного блока 7 формируется импульсная последовательность, закон изменения частоты которой можно представить выражением

F — (1+D), г где F — частота формируемой последовательности; - — частота исходного синхросигнала;

0 — при логическом нуле на выходе бло-!

)= ка 3

1 — при логической единице на выходе блока 3.

Очевидно, что поделив сигнал на выходе мажоритарного блока 7 на 2 "+ можно получить на выходе устройства импульсную последовательность, соответствующую биимпульсному представлению исходного информационного сигнала от источника 1. Это обеспечивается последовательным включением делителя 8 и счетного триггера 9, которые в сумме создают нужный коэффициет деления.

Задержка исходного информационного сигнала в блоке 3 заставляет делитель 8 постоянно «опаздывать» со сменой частоты выходного сигнала. Как видно из фиг. 2з (первый каскад делителя) и фиг. 2и (второй каскад делителя), изменения частоты формируемых импульсных последовательностей происходят с запаздыванием по отношению к исходному информационному сигналу на время задержки блока 3 (в данном случае, равное периоду исходного синхросигнала). Это запаздывание приводит к тому, что фаза последовательности импульсов на выходе счетного триггера 9 меняется не скачками, а через некоторое промежуточное значение (фиг. 2к, заштрихованные импульсы). Сигнал, полученный на выходе счетного триггера 9, соответствует биимпульсному представлению исходного информационного сигнала, причем главная смена фазы обеспечивает заданную достоверность передачи.

Как видно из фиг. 2д, импульсы, формируемые на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6 и поступающие на Rвход делителя 8, не оказывают влияния на его работу, когда они присутствуют в моменты циклического обнуления разрядов делителя 8, т. е., когда цикл работы делителя 8 совпадает с фазой входной информации.

Иначе происходит при их рассинхронизации (начальный участок диаграммы фиг. 2ж), когда делитель 8 принудительно сбрасывается в «О», что обеспечивает требуемую синхронность работы счетчика и поступления входных данных, а в конечном итоге— возможность работы с асинхронной входной информацией.

Согласующий блок 10 обеспечивает преобразование электрических параметров переда1467782 ваемого сигнала к виду, приемлемому для передачи в канал связи.

Формула изобретения

Устройство передачи двоичных сигналов, содержащее источник цифровых сигналов, источник синхросигналов, первый, второй блоки задержки, первый счетный триггер, выход которого соединен с входом согласующего блока, выход которого является выходом устройства, отличающееся тем, что, с целью передачи асинхронных сигналов, введены второй счетный триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и делитель частоты, причем выход источника цифроСоставитель Н.Лазарева

Редактор Н. Тупица Техред И. Верес Корректор М. Максимишинец

Заказ 1215/56 Тираж 627 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1! 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101 а !

В, г

Р

1,Ж

3 вых сигналов через последовательно соединенные первый и второй блоки задержки соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом первого блока задержки и первым входом мажоритарного блока, второй вход которого соединен с выходом источника синхросигнала и С-входом. второго счетного триггера, R-вход и выход которого соединены соответственно с выходом источника цифровых сигналов, и третьим входом мажоритарного блока, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с Rвходом делителя частоты, С-вход которого соединен с выходом мажоритарного блока, а выход — с входом первого счетного триггера.