Фазовый дискриминатор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и может быть использовано в системах автоматического управления или радиоизмерительной аппаратуре для определения знака разности фаз. Цель изобретения - повышение точности при малых соотношениях С/Ш входного сигнала. Для достижения цели в устройство введены формирователь (Ф) 9 импульсов управления, счетчик импульсов (СИ) 10, Ф 11 импульсов обнуления, П-триггер 12, однопороговый и двухпороговый компараторы 13 и 14. Последовательность m импульсов с Ф9 поступает на СИ 10. Параметр m выбирается из соображений обеспечения необходимого быстродействия и точности фазового дискриминатора . Ф 11 формирует импульсы, замыкающие ключи 4 и 8 на время, достаточное для разряда конд-ров 3 и 7, тем самым -подготавливая устройство к работе в следующие m полуперирдов опорного напряжения. После прохождения m полуиериодов на компараторе 13 сравнивается интегральная оценка фазы , накопленная за т/2 четных полупериодов с интегральной оценкой фазы, накопленной за га/2 нечетных полупериодов . Это позволяет вместе с компаратором 14 достичь высокой точности дискриминации при полупериодном быстродействии, высоких фильтрующих качеств при воздействии слабых входных сигналов с малым отношением С/Ш. 3 ил. о 5 сл

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК ("> А» 2 .Ы—

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4282144/24-09 (22) 13.07.87 (46) 30.03.89. Бюл. 11 - 12 (72) Р.-А. Д. Иванцив, А.М. Нивинский, С.Ф. Романюк и В.М. Сокаль (53) 621.376.23(088 ° 8) (56) Авторское свидетельство СССР

В 567199, кл. Н 03 D 3/18, 1977. (54) ФАЗОВЫЙ ДИС КРИМИНАТОР ! (57) Изобретение относится к радиотехнике и может быть использовано в системах автоматического управления или радиоизмерительной аппаратуре для определения знака разности фаз. Цель изобретения — повышение точности при малых соотношениях С/Hl входного сигнала. Для достижения цели в устройство введены формирователь (Ф) 9 импульсов управления, счетчик импульсов (СИ) 10, Ф 1 1 импульсов обнуления, Л-триггер 12, однопороговый и двухпороговый компараl

Изобретение относится к радиотех- ? нике и может быть использовано в системах автоматического управления или радиоиэмерительной аппаратуре дпя определения знака разности фаз при малом соотношении сигнал/шум входного сигнала.

Цель изобретения — повышение точности при малых соотношениях сигнал/

/шум входного сигнала.

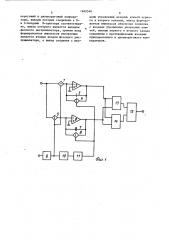

На фиг. 1 приведена структурная электрическая схема фазового дискриминатора; на фиг. 2 — временные диаграммы работы устройства; на фиг.3—

„„SU„„1469540 А1 торы 13 и 14. Последовательность m импульсов с Ф9 поступает на СИ 10.

Параметр ш выбирается из соображений обеспечения необходимого быстродействия и точности фазового дискриминатора. Ф 11 формирует импульсы, замыкающие ключи 4 и 8 на время, достаточное для разряда конд-ров 3 и 7, тем самым-подготавливая устройство к работе в следукщие т полупериодов опорного напряжения. После прохождения m полупериодов на компараторе 13 сравнивается интегральная оценка фазы, накопленная sa m/2 четных полупериодов с интегральной оценкой фазы, накопленной за m/2 нечетных полупериодов. Это позволяет вместе с компаратором 14 достичь высокой точности дискриминации при полупериодном быстродействии, высоких фильтрующих С„ качеств при воздействии слабых входных сигналов с малым отношением С/Ш. ф

3 ил. характеристика, поясняющая принцип работы двухпорогового компаратора. Ю

Фазовый дискриминатор содержит 4ь входной ключ 1, интегрирующий усили- Ю тель 2, конденсатор 3, разрядный ключ

4 первого канала, входной ключ 5, интегрирующий усилитель 6, конденсатор

7, разрядный ключ 8 второго канала, с формирователь 9 импульсов управления, счетчик 10 импульсов, формирователь

Ф»

11 импульсов обнуления, D-триггер 12, однопороговый 13 и двухпороговый 14 компараторы.

Фазовый дискриминатор работает следующим образом.

1469540

На измерительный вход дискриминатора поступает входной синусоидальный сигнал (фиг.2а). Формирователь 9 импульсов управления формирует. импульсы напряжения прямоугольной формы длительностью в половину периода опорного напряжения (фиг.2б) . Полученная последовательность импульсов используется для противофазного управления ключами 1 и 5.

Таким образом, каждый полупериод опорного напряжения один из ключей

Открыт, а другой закрыт. При этом интегрирующий усилитель 2 на конден15 саторе 3 накапливает заряд, пропорциональный сдвигу фазы в нечетные полупериоды, а интегрирующий усилитель 6 на конденсаторе 7 накапливает заряд, пропорциональный тому же сдвигу фазы, но в четные полупериоды опорного напряжения. Напряжения, пропорциональные сдвигу фазы, но противоположные по знаку с выходов инУ тегрирующих усилителей 2 и 6 поступают на противофазные входы однопорогового компаратора 13 (фиг.2в, r), на выходах которого появляются напряжения, характеризующие знак сдвига фазы (фиг. 2ж), и противофазные входы.двухпорогового комнаратора 14.

Двухпороговый компаратор 14 реализует характеристику, показанную на фиг . 3 . Б, H У величины нижнег o H верхнего порогов двухпорогового комп ар ат ора 14 .

Разность напряжений между нижними и верхними порогами двухпорогового компаратора 14 выбрана таким образом, чтобы за полупериод опорного сигнала изменение. напряжения на выходах интегрирующих усилителей 2 и 6 не превышало этой величины.

На выходе двухпорогового компаратора 14 формируется напряжение логи45 ческого нуля„когда сумма напряжений с выходов интегрирующих усилителей 2 и б попадет в зону между нижним и верхним порогами двухпорогового компаратора 14. Когда суммарное напряжение выходит за пределы зоны между порогами двухпорогового компаратора 14, он переключается из логичес кого нуля в логическую единицу, записывая фронтом в D-триггер 12 сигнал с однопорогового компаратора 13 (фиг.2д, е)., Таким образом, если сдвиг фаз между опорным и входным сигналами не изменится, то подтверждается предыпущее состояние D-триггера 12, в случае изменения сдвига фаз и переключения однопорогового компаратора 13 фронтом двухпорогово-. го компаратора 14 новое состояние перепишется в триггер 12 (фиг. 2з).

Последовательность m импульсов с формирователя 9 импульсов управления поступает на счетчик 10 импульсов. Параметр m выбирается из соображений обеспечения необходимого быстродействия и точности фазового дискриминатора ° После прохождения ш импульсов управления через счетчик 10 последний вырабатывает сигнал, поступающий на формирователь 11 импульсов обнуления. Формирователь 11 импульсов обнуления формирует импульсы, замыкающие ключи 4 н 8 на время, достаточное для разряда конденсаторов 3 и 7, тем самым подготавливая дискриминатор к работе в следующие

m полупериодов опорного напряжения.

Таким образом, после прохождения

m полупериодов опорного напряжения на .однопороговом компараторе 13 сравнивается интегральная оценка фазы, накопленная за m/2 четных полупериодов, с интегральной оценкой фазы, накопленной за m/2 нечетных полупериодов (при ш — четное). Это позволяет вместе с применением двухпорогового компаратора 14 достичь высокой точности дискриминации при полупериодном быстродействии, высоких фкльтрующих качеств при воздействии на фазовый дискриминатор слабых входных сигналов с малым соотношением сигнал/шум., Формула изобретения

Фазовый дискриминатор, содержащий два соединенных по входу канала, входы которых являются первым входом фазового детектора, и каждый из которых состоит из последовательно соединенных входного ключа и инвертирующего усилителя, параллельно которому подключены конденсатор и разрядный ключ, отличающийся тем, что, с целью повышения точности при малых соотношениях сигнал/шум входного сигнала, в него введены последовательно соеДиненные формирователь импульсов управления, счетчик импульсов, форм яр Ова тел ъ импул ьсов обнуления, а также D-триггер, одно1469540 пороговый и двухпороговый компараторы, выходы которых соединены с Dи С-входами 0-триггера соответственно, выход которого является выходом фазового дискриминатора, причем. вход формирователя импульсов управления является вторым входом фазового дискриминатора, а выход соединен с входами управления входных ключей первого и второго каналов, выход формирователя импульсов обнуления соединен с входами управления разрядных ключей, выходы первого и второго канала соединены с противофазными входами однопорогового и двухпорогового компараторов.

6 д

6i

Составитель А. Колосов

Техред М. Ходанич Корректор И, Муска

Редактор Т. Лазаренко

Заказ 1364/56 Тираж 879 Подл ис ное

ВНИИПИ Государственного комитета по изобретениям и открытиям при Г Т и ГКНТ СССР

113035, Москва, Ж-35, Рауаская наб., д. 4/5

tt

Производственно-издательский комбинат Патент, г. .жг р д, у . р о о л. Гага ина 101