Устройство для измерения фазового дрожания

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи и м.б. использовано для контроля качества каналов связи. Цель изобретения - повышение точности измерения фазового дрожания как в цифровьк, так и в аналоговых системах связи. Достигается это за счет введения в устр-во формирователя импульсов 5, фазового детектора 21, фильтра низкой частоты 24, г-ра 25 импульсов и узла 29 выделения: опор .1 ной тактовой частоты, который содержит блок 7 определения опережения и запаздьюания фазы, блок 11 определения среднего значения фазы, RS- триггеры 13, 18, элементы И 14, 15, дешифратор 20, счетчик 22, блок сравнения 23 и счетный триггер 26. В устр-ве осуществляется формирование из псевдослучайного линейного сигнала двух регулярных импульсных последовательностей . При этом одна из последовательностей формируется как - опорный высокостабильный импульсный сигнал, а вторая повторяет фазовые флуктуации линейного сигнала. Обе эти последовательности подаются на фазовый детектор 21, где происходит выделение огибающей измеряемого фазового дрожания, поступающей далее на индикатор. 2 з.п. ф-лы, 5 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„,90„„146955 (б11 4 Н 04 В 3/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4274635/24-09 (22) 02,07,87 (46) 30,03.89. Бюл. 1 - 12 (72) В,A,Àáðàìoâ и С,И,Нечаев (53) 621.396.664(088,8) (56) Авторское свидетельство СССР

Р 696617, кл. Н 04 В 3/46, 1978. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ФАЗОВОГО ДРОЖАНИЯ (57) Изобретение относится к технике связи и м.б. использовано для контроля качества каналов связи. Цель изобретения — повышение точности измерения фазового дрожания как в цифровых, так и в аналоговшх системаМ связи. Достигается это за счет введения в устр-Во формирователя 3&I пульсов 5, фазового детектора 21, фильтра низкой частоты 24, г-ра 25 импульсов и узла 29 выделенкя опор.! .

3 ной тактовои частоты, который содержит блок 7 определения опережения к запаздывания фазы, блок 11 определения среднего значения фазы, Ютриггеры 13, 18, элементы И 14, 15, дешифратор 20, счетчик 22, блок сравнения 23 и счетный триггер 26. В устр-ве осуществляется формирование из псевдослучайного линейного сигнала двух регулярных импульсных последовательностей, При этом одна из последовательностей формируется как опорный высокостабильный импульсный сигнал, а вторая повторяет фазовые флуктуации линейного сигнала. 06е эти последовательности подаются на фазовый детектор 21, где происходит выделение огибающей измеряемого фазового дрожания, поступающей далее на индикатор. 2 з,п. ф-лы, 5 ил.

1469556

1!зобретение относится к технике связи 1! может быть использовано для контроля качества каналов связи.

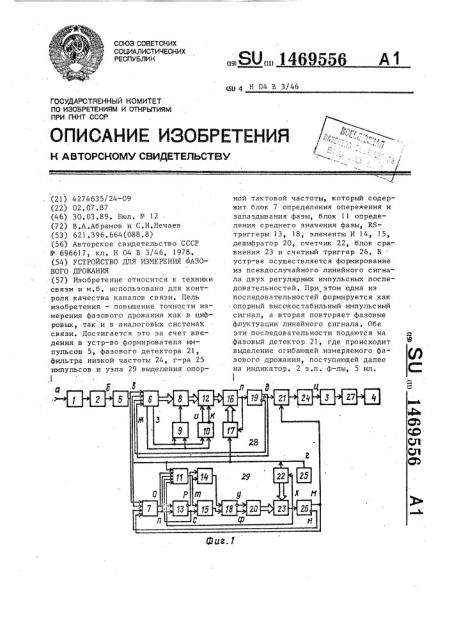

Цель изобре гения — повышение точности измерения фазового дрожания как в цифровых, так и в аналоговых спс.темах связи, Па фиг. 1 изображена структурная электрическая схема устройства для измерения фазового дрожания; на фиг, 2 приведены временные диаг раммы работы устройства; на фиг. 3 показана схема реализации одного блдка определения опережения и запаздывания фазы; на фпг. 4 — то же, другого блока определения опережения и запаздывания фазы; на фиг. 5 — схема построения блока определения среднего значения фазы.

Устройство состоит из блока ) согпасования, выпрямителя 2, квадратичного детектора 3, индикатора 4, формирователя 5 импульсов, блоков 6, 7 определения опережения и запаздывания фазы накопителя 8, элемента, ИЛИ 9, RS-триггера 10, блока 11 опре деления среднего значения фазы, дешифратора 12, RS-триггера 13, первого элемента И 14, второго элемента И

15, блока 1 6 сравнения, счетчика 17, RS-триггера 18, счетного триггера 19, дешифратора 20, фазового детектора 21 счетчика ?2, блока 23 сравнепия, фильтра 24 низкой частоты, генератора 25 импульсов, счетного триггера

26, блока 27 усреднения„ Блоки 6, 8, 9, 10, 12, !6, 17, 19 образуют узел

28 выделения тактовой частоты; блоки

7, 11, 13, 14, 15, 18, 20, 22, 23, 26 — узел 29 выделения опорной тактовой частоты, Блок 6 (фиг. 3) определения опережения и запаздbtBBnèÿ фазы состоит из элементов И 30 — 35, формирователей 36 — 39 кiпульсов, RS òðèããåðîâ

40 — 44, элементов ИЛИ 45, 46, элементов 47, 48 задержки, счетчиков 49, 50, узла 51 ключевых элементов и уз. ла 52 элементов ИЛИ, 30

Блок 7 {фиг. 4) определения опережения и запаздывания фазы состоит из, коммутаторов 53, 54, элементов

ИЛИ 55, 56, элементов И 57 — 64, формирователей 65 — 70 импульсов, RS-триггеров 71 — 76, элементов 77, 78 задержки, счетчиков 79, 80, дешифраторов 81, 82, счетного тригге10

50 55 ра 83, узла 84 элемен"îB ИЛИ, узла

85 ключевых элементов.

Блок )1 (фиг. 5) определения среднего значения фазы состоит из формирователей 86 — 88 импульсов, элемента 89 задержки, элементов И

90 — 92, элементов ИЛИ 93 — 95, инBертора 96, RS-триггеров 97, 98, первого счетчика 99, элемента 100 сравнения, дешифратора 101 и второго счетчика 102.

Устройство для измерения фазового дрожания работает следующим образом.

На вход устройства на линии связи или с выхода регенератора (в случае, когда измеряется фазовое дрожание импульсной последовательности)подается цифровой или аналоговый сигнал.

Рассмотрим работу данного устройства для наиболее трудного случая, когда на его вход поступает псевдослучайный цифровой сигнал (фиг. 2а), скважность между импульсами в котором изменяется по случайному закону, функционирование предложенного устройства основано на формировании из псевдослучайного линейного сигнала двух регулярных импульсных последовательностей, соответствующих напряжению тактовой частоты данной системы связи. При этом одна из последовательностей формируется как опорный высокостабильный импульсный сигнал. Вторая же импульсная после-. довательность формируется таким образом, что она повторяет фазовые флуктуации, имеющие место в цифровом линейном сигнале на входе устройства, Обе регулярные импульсные последовательности подаются на фазовый детектор, где происходит выделение огибающей измеряемого фазового дрожания. Флуктуационное аналоговое напряжение после прохождения через фильтр. низкой частоты, квадратичный детектор и блок усреднения подается на индикатор, Перед началом работы все тригге-. ры и счетчики, входящие в данное устройство, устанавливаются в исходное состояние.

Сигнал с входа устройства (фиг.2а) попадает на вход блока 1 согласования, Блок 1 согласования обеспечивает необходимое входное сопротивле ние устройства для сопряжения с измеряемым каналом связи. Кроме того, в данном блоке осуществляется усиле1469556 ние сигнала (можно с использованием

АРУ), а в случае, когда сигнал представляет собой однополярную двоичную последовательность (например, как в системе ИКМ-12), осуществляется дифференцирование этого сигнала, С выхода блока 1 согласования сигнал поступает на вход выпрямителя 2, где осуществляется его двухполупериодное выпрямление (без фильтрации). Выпрямленный сигнал (фиг. 2б) подается на вход формирователя 5. В данном блоке осуществляется формирование коротких импульсов по передним фронтам выпрямленного сигнала (фиг. 2в).

Короткие импульсы с выхода формирователя 5.подаются на первые входы блоков 6, 7 определения опережения и запаздывания фазы. На вторые входы блоков 6, 7 поступают высокочастотные импульсы (фиг. 2г) от генератора 25 импульсов. На третий и четвертый входы блока 6 подаются прямоугольные импульсы (частота которых соответствует тактовой частоте контролируемой системы связи) с инверсного.и прямого выходов первого счетного триггера 19 (фиг. 2д, е).

На третий и четвертый входы бло30 ка 7 также подаются прямоугольные импульсы с инверсного и прямого выходов счетного триггера 26 (фиг, 2м,н).

Импульсная последовательность с выхода счетного триггера 26 является высокостабильным опорным сигналом, с которым сравнивается импульсная последовательность, получаемая на выходе счетного триггера 19 и повторяющая фазовые флуктуации, имеющие место в сигнале на входу устройства.

Формирование флуктуирующей по фазе регулярной импульсной последовательности (фиг. 2д, е) происходит следующим образом.

В блоке 6 происходит сравнение фазы (момента появления) каждого импульса с выхода формирователя 5 (фиг. 2в) с фазой (моментом перехода из 1 в "0" и из "0" в "1") прямоугольных импульсов с выходов счет- 5О ного триггера 19 (фиг. 2д, е). Промежуток времени, соответствующий разности фаз этих сравниваемых импульсов, заполняется высокочастотными.импульсами от генератора 25 55 (фиг, 2г) . При этом чем больше разность фаз между сравниваемыми импульсами, тем большее количество нысокочастотных импульсов от генерато- „ ра 25 уменьшается в промежутке времени, соответствующем данной разности. фаз ° Высокочастотные импульсы заполнения подсчитываются счетчиком, находящимся н блоке 6, и íà его кодовом выходе поянляются кодовые комбинации, соответствующие в двоичном выражении величине разности фаз между сравниваемыми сигналами.

В блоке 6 имеются также первый и второй управляющие выходы. Короткие импульсы, которые поянляются на первом управляющем выходе блока 6 (фиг. 2ж), соответствуют такому состоянко, когда фаза импульсов с выхода формирователя 5 (фиг. 2в} опережает фазу импульсов с выхода счетного триггера 19 (фиг. ?д). Появление таких же коротких импульсов на втором управляющем выходе блока б (фиг. 2з) соответствует такому положению, когда фаза импульсов с выхода формирователя 5 запаздывает по отношен по к фазе импульсов с выхода счетного триггера 19.

Кодовые комбинации с кодового выхода блока 6, соответствующие разности фаз между сравниваемыми сигналами, подаются к кодовому входу накопителя 8, но не записываются в него.

Запись кодовой комбинации в накопитель 8 происходит только при появлении на его управляющем входе короткого импульса, поступившего с первого или второго управляющего выхода блока 6 через элемент ИЛИ 9 (фиг. 2ж, s).

Кодовая комбинация, записанная в, накопитель 8, появляется на его выходе и подается к кодовому входу дешифратора 12. Дешифратор 1? преобразует кодовые комбинации с выхода блока 6, соответствующие разности .фаз между сигналами с выходов формирователя 5 и счетного триггера 19, в кодовые комбинации, соответствующие длительностям единичных тактовых интервалов для данной системы связи, Рассмотрим для примера случай, когда длительность единичного тактового интервала может быть представлена 1024 высокочастотными импульсами с выхода генератора 25. Данное количество импульсов (1024), соответствующее длительности неискаженного тактового интервала, представляется двоичным числом 10000000000.

5 146 .Такое двоичное число появится на кодовом выходе счетчика 7 после подачи на его информационный вход 10?4 импульсов с выхода генератора 25, Двоичное число 10000000000 (1024) с выхода счетчика 17 подается к второму кодовому входу блока 16 сравнения. Для срабатываний блока 16 сравнения необходимо, чтобы иа его первом кодовом входе было точно такое же двоичное число. Следовательно, при отсутствии фазового сигнала между импульсами линейного сигнала (выход формирователя 5) и тактовыми им- пульсами (выход йервого счетного триггера 19) на выходе дешифратора

12 появляются только кодовые комбинации вида 10000000000 (1024), на основе которых формируются тактовые импульсы (фиг, 2д, е)> где моменты порехода иэ "0" в "1" и из "1" в "0" точно соответствуют таким же моменTBhf в неискаженном линейном сигнале (фиг. 2а) на входе устройства.

При близком, но не равном значении фазы импульса линейного сигнала (1-й вход блока 6) с фазой тактового импульса (3 и 4-й входы блока 6) па кодовом выходе блока 6 появляется, например, кодовая комбинация

0000000001. Эта кодовая комбинация подается к кодовому входу накопителя 8. Кроме того на одном из двух управляющих выходов блока 6 (например, на первом) появляется короткий импульс (фиг, 2ж),.свидетельствующий об опережении фазой информационного импульса (выход фогмирователя 5) фазы тактового импульса (выход счетного триггера 19), который подается с первого управляющего выхода блока 6 на первый вход элемента ИЛИ 9 и через него на управляющий вход накопителя 8. Под действием данного импульса накопитель 8 записывает кодовую комбинацию 0000000001, и она появляется на его выходе. Эта комбинация подается к кодовому входу дешифратора 12.

Импульс с первого управляющего выхода блока 6 поступает также на

R-вход КБ-триггера 10, на инверсном выходе которого будет напряжение логической единицы (д иг, 2к), а на прямом - напряжение логического нуля ,,(фиг. 2и) . Сигналы с прямого и инверсного выходов RS-триггеров 10 подаются на первый и второй дополни

9556 6 тельные входы дешид ратора 12 и добавляются в старшие разряды к кодовой комбинации, присутствующей на кодовом входе дешифратора 12, Тогда

6 на входе дешифратора 1? будет кодовая комбинация 100000000001, Дешифратор 12 осуществляет преобразование данной кодовой.комбинации в кодовую комбинации 01111111100 (1023) . Эта кодовая комбинация подается на первый вход блока 16 сравнения> на второй кодовый вход которого поступают непрерывно меняющиеся кодовые комбинации с кодового выхода счетчика 17.

При поступлении на информационный вход счетчика 1023 импульсов с выхода генератора 25 »а кодовом выходе счетчика 17 появляется кодовая комбинация 01111111111 (1023), В определенный момент времени на первом и втором кодовых входах блока 16 сравнения оказываются одинаковые кодовые комбинации, вследствие

25 чего на его выходе появляется короткий импульс (фиг. 2л). Под действием этого импульса сбрасывается в нуле— вое состояние счетчик 17, а также срабатывает счетный триггер 19, На прямом выходе счетного триггера 19 появляется напряжение логической единицы, Следствием всего этого будет укорачивание длительности сформированного тактового интервала сигнала на выходе счетного триггера 19 (фиг. 2д, е, л) на величину одного периода высокочастотных импульсов заполнения от генератора 25. В результате фаза тактовых импульсов ока40 зывается точно подстроенной под фазу входных информационных импульсов.

Во время пауз в поступлении информационных импульсов на первый вход блока 6 (при псевдослучайном цифровом информационном сигнале в

45 линии) на кодовом выходе данного блока будет кодовая комбинация

0000000000. Эта кодовая комбинация с приходом короткого импульса с первого или второго управляющего выхода

5О блока 6 записывается в накопитель 8, В дешифраторе 12 к этой кодовой комбинации в ее старшие разряды добавляются напряжения логического нуля и единицы с прямого и инверсного выходов RS-триггера 10. В результате

wможет иметь место либо кодовая комбинация 1 0000000000, либо кодовая комбинация 010000000000. Обе эти

1469556 8 кодовые комбинации дешифратор 12 преобразует в кодовую комбинацию

10000000000 (1024), соответствующую неискаженному тактовому интервалу сигнала на выходе счетного триггера 19, Рассмотрим случай, когда фаза входного информационного импульса (выход формирователя 5) немного отстает от фазы тактового импульса (выход счетного триггера 19).

Пусть на кодовом выходе блока 6, как и в ранее рассмотренном случае, будет кодовая комбинация 00000000001 °

Эта кодовая комбинация подается к кодовому входу накопителя 8, Кроме того,на втором управляющем выходе блока 6 появляется короткий импульс, свидетельствующий о запаздывании входного импульса относительно тактового. Под действием этого импульса кодовая комбинация, приложенная к кодовому входу накопителя 8, записывается в него и оказывается на его кодовом выходе (кодовом вхбде дешифратора 12). Одновременно под действием этого же импульса, подаваемого на S-вход RS-триггера 10, он опрокидывается и на его прямом выходе появляется напряжение логической единицы, а на инверсном — напряжение логического нуля. Эти напряжения поступают на первый и второй дополнительные входы дешифратора 12.

В результате на входе дешифратора 12 образуется кодовая комбинация

0100000000001. Дешифратор 12 преобразует данную комбинацию в кодовую комбинацию 100000000001 (1025), которая прикладывается к первому кодовому входу блока 16 сравнения. На второй кодовый вход блока 16 сравнения подаются непрерывно меняющиеся кодовые комбинации с выхода счетчика 17. При совпадении кодовых комбинаций на первом и втором кодовых входах блока 16 сравнения на его кодовом выходе появляется короткий импульс (фиг. 2л). Этим импульсом, во-первых, сбрасывается в исходное состояние счетчик 17, а во-вторых, под его воздействием срабатывает счетный триггер 19, В результате длительность тактового интервала сигнала на выходе счетного триггера

19 увеличивается на один период высокочастотных импульсов заполнения (от генератора 25), что соответствует подстройке фазы тактового импуль5

55 са под фазу входного информационного импульса, Наибольшая величина расхождения фазы информационного импульса с фазой тактового импульса для данного устройства может быть выбрана равной половине тактового интервала. Это соответствует 512 импульсам заполнения от генератора 25 и комбинации

10000000000 на кодовом выходе блока 6, При опережении информационным импульсом на входе устройства фазы тактового импульса на половину тактового интервала (512 импульсов заполнения) на кодовом входе дешифратора 1? (совместно с двумя дополнительными входами) образуется кодовая комбинация 101000000000. Данная комбинация преобразуется в дешифраторе

12 в кодовую комбинацию 01000000000 (512) .

При отставании фазы информационного импульса относительно фазы тактового импульса на половину тактового интервала (512 импульсов заполнения) на кодовом входе дешифратора

12 (совместно с двумя дополнительными входами) образуется кодовая комбинация 011000000000. Данная комбинация преобразуется в дешифраторе

12 в кодовую комбинацию 11000000000 (1536) .

Далее кодовая комбинация (например, 11000000000) прикладывается к первому кодовому входу блока 16 сравнения, на второй кодовый вход которого непрерывно поступают комбинации с выхода счетчика .17. Через

1536 импульсов, подаваемых на информационный вход счетчика 17 от генератора 25, на выходе данного счетчика появляется кодовая комбинация

11000000000, которая подается на второй кодовый вход блока 16 сравнения, Поскольку кодовые комбинации на обоих входах блока 16 сравнения одинаковы, то íà его выходе появляется короткий импульс. Этим импульсом счетчик 17 сбрасывается в исходное состояние, и, кроме того, под воздействием данного импульса срабатывает счетный триггер 19. На выходе счетного триггера 19 оказывается сформированным импульс, длительность которого стала равной 1,5 тактовым интервалам или 1536 импульсам заполнения. В результате этого фаза тактовых импульсов на выходе счет1469556

10 ного триггера 19 оказалась точно подстроенной под фазу информационного сигнала на входе устройства.

Таким образом, любое изменение фазы входных импульсов относительно тактовых импульсов (выход счетного триггера 19) всегда завершается подстройкой фазы данных тактовых импульсов под фазу входного сигнала.

В результате проделанных операций происходит переход от линейного сигнала со случайной скважностью (фиг. 2а) к регулярной импульсной последовательности (фиг, 2д) с сохранением информации о фазовом дрожании сигнала. Это необходимо было проделать для того, чтобы исключить влияние случайной скважности линей)ного сигнала на измеряемое фазовое дрожание. Беэ данного преобразования измерение фазовых флуктуаций в

)цифровом сигнале со случайной скважностью между импульсами оказалось бы невозможным.

Регулярное тактовое колебание (фиг. 2д) с выхода счетного триггера 19 поступает на первый вход фазового детектора 21. Однако для выделения огибающей фазовых флуктуаций из этого сигнала необходимо иметь высокостабильное опорное колебание. Это колебание получают с помощью блоков 7, 11, 13 14, 15, 18, 20, 22, 23, 26, образующих узел

29 выделения опорной тактовой частоты.

Формирование высокостабильной импульсной последовательности (фиг. 2м, н) осуществляется следующим образом.

В блоке 7 происходит сравнение фазы (момента появления) импульса с выхода формирователя 5 (фиг. 2в) с фазой прямоугольных импульсов, поступающих с прямого и инверсного выходов счетного триггера 26. Наличие опережения или запаздывания фазы информационных импульсов проявляется в появлении на первом или втором управляющем входе блока 7 коротких импульсов (фиг. 2о, п). Эти сигналы подаются на R- u S-входы RS-триггера 13 и на второй и третий входы блока 11 определения среднего значения фазы.

При появлении на первом управляющем выходе (фиг. 2о) блока 7 короткого импульса (свидетельствующего об опережении фазы информационного импульса по отношению к тактовому) RSтриггер 13 устанавливается в такое

5 состояние при котором на его ин1 версном выходе будет напряжение логической единицы, а на прямом — напряжение логического нуля (фиг. 2р, с).

Эти напряжения прикладываются к первым входам первого и второго элемен. тов И 14, 15, однако не проходят через них, так как на вторые входыданных элементов подается напряжение логического нуля с выхода блока 11 определения среднего значения фазы.

На первый вход блока 11 поступают высокочастотные импульсы (фиг. 2г) с выхода генератора 25„На четвертый вход блока 11 подаются напряжения логических нулей и единиц с прямого выхода RS-триггера 13, а на пятый вход блока 11 — короткие импульсы (фиг. 2х) с выхода блока 23 сравнения. Моменты появления импульсов на

25 выходе блока 11 в стационарном режиме работы измерительного устройства соответствуют средним значениям фазы информационного сигнала на входе данного, устройства. Короткий импульс с выхода блока 11 (фиг. 2т) поступает на вторые входы первого и вто) рого элементов И. 14, 15, однако проходит только через первый элемент И

14, поскольку на его первом входе в это время действует потенциал ло35 гической единицы с инверсного выхода RS-триггера 13. Этот короткий импульс подается на К-вход RS-триггера 18 и опрокидывает его, На инверс40 ном выходе RS-триггера 18 появляется потенциал логической единицы, а на прямом — потенциал логического нуля. Кодовая комбинация 10 прикладывается к первому и второму входам

45 дешифратора ? 0. Дешифратор 20 преобразует данную кодовую комбинацин э кодовую комбинацию 01111111111()023) на основе которой формируются укороченные на один период высокочастотных импульсов заполнения высокостабильные тактовые импульсы (фиг. 2м).

Происходит это следующим образом.

Кодовая комбинация 011111111)) (1023) прикладывается к первому «одовому входу блока 23 сравнения. На второй кодовый вход блока 23 с кодового выхода счетчика 22 поступают непрерывно меняющиеся кодовые комбинации, пропорциональные количеству

1469556

5

30

55 высокочастотных импульсов, поступив- ших на информационный вход счетчика 22.

В момент совпадения кодовых комбинаций 01111111111 на первом и вто ром кодовых входах блока 23 сравнения на его выходе появляется короткий импульс (фиг. 2х). Этот импульс, во-первых, сбрасывает в исходное состояние счетчик 22, а но-вторых, заставляет сработать счетный триггер 26. Если кодовая комбинация

01111111111 ()023) продолжает присутствовать на первом кодовом входе блока 23 сравнения н течение продолжительного времени, то на выходе счетного триггера 26 формируются тактовые импульсы, длительность единичного интервала в которых равна

1023 высокочастотным импульсам от генератора 25.

При появлении на втором управляю- щем выходе блока 7 коротких импульсов (фиг. 2п), свидетельствующих об отставании по фазе со стороны информационных импульсов по отношению к тактовым,. RS-триггер 13 устанавливается в такое состояние, при котором на его инверсном выходе будет потенциал логического нуля, а на прямом — потенциал логической единицы. Эти напряжения прикладываются к первым входам первого и второго элементов И 14, 15 (фиг, 2р, с).

Короткий импульс, появившийся на выходе блока 11 (фиг. 2т), проходит через второй элемент И !5 и заставляет сработать RS-триггер 18. На инверсном выходе RS-триггера 18 появляется потенциал логического нуля, а на прямом — потенциал логической единицы (фиг, 2у, ф), Кодовая комбинация 01 с выходов RS-триггера 18 прикладывается к первому и второму входам дешифратора 20. Дешифратор 20 преобразует данную кодовую комбинацию в кодовую комбинацию 10000000001 (1025), на основе которой формируются увеличенные на один период высокочастотных импульсов заполнения высокостабильные тактовые импульсы (фиг. 2м).

Результатом работы описываемых блоков будет наличие высокостабильного опорного колебания на выходе счетного триггера 26. При этом фаза данного сигнала соответствует математическому ожиданию фазы информационного сигнала.

Тактовые импульсы, флуктуирующие по фазе (с выхода счетного триггера 19), и высокостабильные опорные тактовые импульс.: (с выхода счетного триггера 26) подаются соответственно на первый и второй входы фазового детектора 21. Из сигнала с выхода фазового детектора 21 с помощью фильтра 24 низкой частоты вьделяется напряжение огибающей фазового дрожания, представляющее собой шумоподобное колебание (фиг. 2ц) . Это напряжение подается затем на вход квадратичного детектора 3. Сигнал с выхода квадратичного детектора 3 поступает на вход блока 27 усреднения, представляющего в простейшем случае интегринующую схему. После усреднения напряжения, пропорциональное среднеквадратичной величине фазового дрожания, подается на вход индикатора 4.

Формула изo6 ретения

1, Устройство для измерения фазового дрожания, содержащее последовательно соединенные блок согласования и выпрямитель, узел вьделения тактовой частоты, квадратичный детектор, блок усреднения и индикатор, о т л и ч а ю щ е е с я тем, что, с целью повышения точности измерения фазового дрожания как в цифровых, так и в аналоговых системах связи, введены генератор импульсов и последовательно соединенные формирователь импульсов, узел выделения опорной тактовой частоты, фазовый детектор и фильтр низкой частоты, выход которого подключен к входу квадратичного детектора, выход выпрямителя подключен к входу формирователя импульсон, выход которого подключен к первому входу узла выделения тактовой частоты, выход которого подключен к другому входу фазового детектора, выход квадратичного детектора подключен к входу блока усреднения, выход которого соединен с входом индикатора, а выход генератора импульсов подключен к второму и третьему входам узла выделения тактовой частоты и к второму, третьему и четвертому входам узла выделения опорной тактовой частоты.

1З 146

2, Устройство IIo II, 1, o T JI u ч а ю щ е е с я тем, ITo узел выделения тактовой частоты содержит последовательно соединенные блок Опре-. деления опережения н запаздывания фазы, накопитель, дешифратор, блок сравнения и счетный триггер, элемент ИЛИ, включенный между первым и вторым управляющимн выхздами блока определения опережения и запаздывания фазы и управляющим входом накопителя, RS-TpIö.ãåð, входы которого соединены с входами элемента HJIH а выходы подключены к другим входам дешифратора, счетчик„ выходы которого подключены к другим входам блока сраВнения> ВыхОд которого пОдключен к управляющему входу счетчика, при этом второй вход блока определения опережения и запаздывания фазы и счетный вход счетчика являются соответственно вторым и третьим вхо, дами узла выделе тактовой частоты, выходом которого является первый выход счетного триггера, подключенный к третьему входу блока определения опережения и запаздывания фазы, четвертый вход которого соединен с вторым выходом счетного триггера.

3. Устройство по п. 1, о т л и— чающе ес я тем, чтоузелвыделения опорной тактовой частоты содержит последовательно соединенные блок определения опережения и запаз— дывания фазы, первый RS-триггер, первый элемент И, вход которого соеI

9556 14 динен с выходом блока определения среднего значения фазы, второй RSтриггер, другой вход которого соединен с выходом второго элемента И, дешифратор, блок сравнения, другие входы которого соединены с выходами счетчика, и счетный триггер, первый выход которого является выходом узла выделения опорной тактовой частоты, при этом первый и второй входы блока определения опережения и запаздывания фазы являются соответственно первым и вторым входами узла выделения опорной тактовой частоты, а третий и четвертый входы соединены соответственно с вторым и первым вь|ходами счетного триггера, первый вход блока определения среднего значения фазы и счетный вход счетчика являются соответственно третьим и четвертым входами узла выделения опорной тактовой частоты, второй и третий входы блока определения сред25 .него значения фазы соединены соответственно с первым и вторым выходами блока определения опережения и запаздывания фазы, соединенным с другим входом первого RS-триггера, второй выход которого подключен к четвертому входу блока определения среднего значения фазы, пятый вход которого соединен с выходом блока сравнения и управляющим входом счетчика, первый вход второго элемента

И соединен с вторым выходом первого

RS-триггера, а второй вход соединен с вторым входом первого элемента И.

8 г Ь д

1469556

1469556

Составитель А.Сеселкин

Редактор А,Маковская Техред Л.Сердюкова Корректор Л.Обручар

Заказ 1366/57 Тираж 627 Подписное

БНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Чоакпа, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101