Кодер для цифровых систем передачи телефонных сигналов

Иллюстрации

Показать всеРеферат

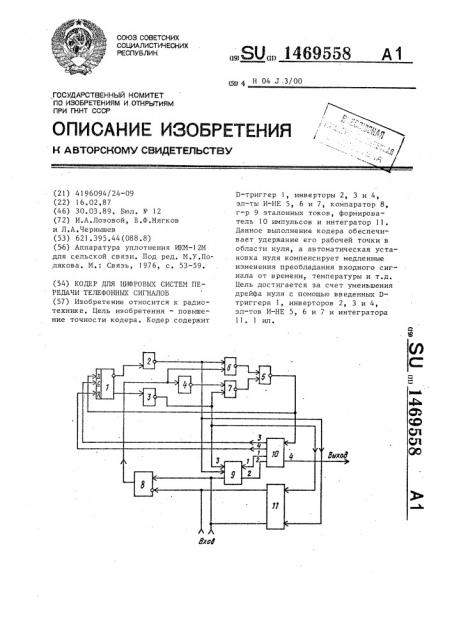

Изобретение относится к радиотехнике . Цель изобретения - повышение точности кодера. Кодер содержит D-триггер 1, инверторы 2, 3 и 4, эл-ты И-НЕ 5, 6 и 7, компаратор 8, г-р 9 эталонных токов, формирователь 1 О импульсов и интегратор 11. Данное выполнение кодера обеспечивает удержание его рабочей точки в области нуля, а автоматическая установка нуля компенсирует медленные изменения преобладания входного сигнала от времени, температуры и т.д. Цель достигается за счет уменьшения дрейфа нуля с помощью введенных D- триггера 1, инверторов 2, 3 и 4, эл-тов И-НЕ 5, 6 и 7 и интегратора 11 . I ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

151> 4 Н 04 J 3/00 4

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4196094/24-09 (22) 16.02.87 (46) 30.03.89. Бюл. Р 12 (72) И.А.Лозовой, В.Ф.Мягков и Л.А.Чернышев (53) 621.395.44(088.8) (56) Аппаратура уплотнения ИКМ-12М для сельской связи. Под ред. N.Ó,ÏOлякова. М.: Связь, 1976, с. 53-59. (54) КОДЕР ДЛЯ ЦИФРОВЬЖ СИСТЕМ ПЕ—

РЕДАЧИ ТЕЛЕФОННЫХ СИГНАЛОВ (57) Изобретение относится к радиотехнике, Цель изобретения — повышение точности кодера. Кодер содержит

„„Я0„„1469558 Д1

D-триггер 1, инверторы 2, 3 и 4, эл-ты И-HF. 5, 6 и 7, компаратор 8, г-р 9 эталонных токов, формирователь 10 импульсов и интегратор 11.

Данное выполнение кодера обеспечивает удержание его рабочей точки в области нуля, а автоматическая установка нуля компенсирует медленные изменения преобладания входного сигнала от времени, температуры и т.д.

Цель достигается за счет уменьшения дрейфа нуля с помощью введенных Dтриггера 1, инверторов 2, 3 и 4, эл-тов И-НЕ 5, 6 и 7 и интегратора

11. 1 ил.

1469558

Кодер для цифровых систем передачи телефонных сигналов, содержащий формирователь импульсов, первый и второй выходы. которого подключены к первому и второму управляющим входам генератора эталонных токов, первый выход которого подключен к прямому входу компаратора, о т л и— ч а ю шийся тем, что, с целью повышения точности эа счет уменьшения дрейфа нуля, введены D-триггер, первый, второй и третий инверторы, первый, второй и третий элементы

И - НЕ и интегратор, первый и второй входы которого объединены с соответствующими третьим и четвертым управляющими входами генератора эталонных токов и подключены к выходам соответственно первого и второго инверторов, входы которых подключены соответственно к инверсному и прямому выходам D-триггера, входы синхронизации и сброса которого под,ключены соответственно к третьему и четвертому выходам формирователя им -пульсов, вход которого объединен с информационным входом D-триггера и подключен к выходу первого элемента

И-НЕ, входы которого соединены с выходами соответственно второго и третьего элементов И-НЕ, первые вхоИзобретение относится к радиотехнике и связи и может быть использо-.. вано в цифроаналоговых преобразователях телефонных сигналов в аппара5 туре с импульсно-кодовой модуляцией.

Целью изобретения является повышение точности за счет уменьшения дрейфа нуля.

На чертеже представлена структур- 10 ная электрическая схема кодера для цифровых систем передачи телефонных сигналов.

Кодер содержит D-триггер 1, пер- 15 вый 2, второй 3 и третий 4 инверторы, первый 5, второй 6 и третий 7 элементы И-НЕ, компаратор 8, генератор 9 эталонных токов, формирователь 10 импульсов и интегратор )1. 20

Кодер для цифровых систем передачи цифровых сигналов работает следующим образом.

Для обеспечения автоматической установки нуля прямой и инверсный 25 выходы 9-триггера 1, запоминающего значение первого разряда, определяемого полярностью кодируемого сигна« ла, соединены через интегратор 11 с входом компаратора 8. 30

Работа автоматической установки нуля кодера заключается в том,) что при преобладании входного сигнала какой-либо полярности на выходах

0"триггера 1 появляются соответству35 ющие сигналы - "1 и "0". Эти сигналы через первый 2 и второй 3 инвер- . торы подаются на интегратор 11 который накапливает энергию и в резуль. тате на вход компаратора 8 иэ интег" щ0 ратора 11 поступает ток такого направления, которое компенсирует пре- обладание входного сигнала. Носле компенсации преобладания и перехода через нуль состояние выходов П-триггера 1 изменяется на обратное и ток, протекающий от первого 2 и вто- . рого 3 инверторов через интегратор

11 к компаратору 8, начинает изменяться в обратном направлении, что приводит к повторному переходу через нуль.

Таким образом, рабочая точка предлагаемого кодера будет удерживаться в области нуля, а автоматическая установка нуля будет компенсировать медленные изменения преоб- 1 ладания входного сигнала от времени, температуры и т.д.

Кодовая комбинация, поступающая от компенсатора 8, проходит либо через третий иннертор 4, третий элемент И-НЕ 7 и первый элемент И-НЕ 5 при наличии "1" на инвертирующем и

"0" на прямом выходах D-триггера 1, либо через второй элемент И-НЕ 6 и первый элемент И-НЕ 5 при наличии

"0" на ийвертирующем и "1" на прямом выходах D-триггера 1. Нри этом в первом случае осуществляется инверсия кодовой комбинации, во втором случае инверсия отсутствует. Информация о первом разряде на D-триггер

1 поступает после установки D-триггера 1 в исходное состояние.

Генератор 9, управляемый формирователем 10, формирует сигналы, которые сравниваются компаратором 8 с выходным сигналом кодера.

На четвертом выходе формирователя 10 присутствуют сигналы импульснокодовой модуляции.

Формула изобретения

1469558

Составитель В.Шевцов

Редактор А.Маковская Тжред Л.Сердюкова Корректор О.Кравцова

Закаэ 1366/57 Тираж 627 Подписное ВНИИПИ Государственного комитета lIo.êâîáðåòåíèÿì и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Проиэводственно-иэдательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 ды которых подключены к выходам со- ответственно первого и второго инв ерто ров, а в торые входы в торого и третьего элементов И-HE подключены соответственно к входу и выходу третьего инвертора, вход которого соединен с выходом компаратора, прямой и инверсный входы которого соединены соответственно с первым и вторым выходами интегратора.