Запоминающее устройство на сегнетоэлектрических матрицах

Иллюстрации

Показать всеРеферат

Класс 42m, )4 > № 147025

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

11ос)пнснач рупца Л I /-I

Е, И. Мамонов и И. С. Желудев

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО HA СЕГНЕТОЗЛЕКТРИЧЕСКИХ

МАТРИЦАХ

Заявлено 25 января 1960 г за ¹ 65l825/26 в Комитет по делам изобретений и открытий при Совете Министров СССР

Опубликовано в «Бк>ллетене изобретений > ¹ 9 за 1962 г

Известны запоминающие устройства на сегнетоэлектрических матрицах с полупроводниковыми схемами управления и восстановлением информации после считывания, сочетаюшие параллельный принцип действия с возможностью последовательной выдачи через магнитострнкционную линию задержки Эти устройства содержат блок адресной сслекции с диодным дс.цифратором, регистры и усилители.

B предлагаемом запоминающем устройстве на сегнетоэлектричсских матрицах для повышения надежности и быстродействия схемы управления связаны с матрицей посредством трансформаторно-реостатных цепей, позволяющих устранить накопление паразитных зарядов производить считывание в форсированном режиме.

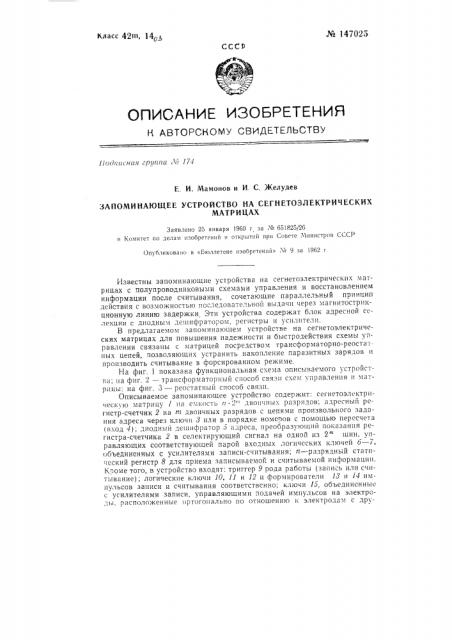

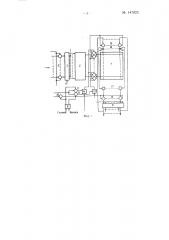

Нг фиг. 1 показана функциональная схема описываемого устройстpà; на фиг. 2 — трансформаторный способ связи схем управления и матрицы, на фиг. 3 — рсостатный способ связи.

Описываемое запоминающее устройство содержит: сегнетоэлсктри ескую матрицу 1 на емкость п.оп двоичных разрядов; адрссньш регистр-счетчик 2 на m двоичных разрядов с цепями произвольного задания адреса через ключи 3 или B порядке номеров с помощью пересчета (вход 4); диодный дешифратор 5 адреса, преобразующий показания регистра-счетчика 2 в селектируюший сигнал на одной из 2" шин, управляющих соответствуюгцей парой входных логических ключей 6 — 7. объединенных с усилителями записи-считывания; тт — разрядный статический регистр 8 для приема записываемой и считываемой информации.

K".,î 1е того, в устройство входят: триггер 9 рода работы (запись пли считывание); логические ключи 10, 11 и 12 и формирователи 13 и l4 IMiIóëüñ0â записи и считывания соответственно; ключи 15, объединснные с усилителями записи, управляющими подачей импульсов на электроды, расположенные ортогоца по отношению к электродам с дру¹ 147025 гой стороны матрицы, соединенным с ключами 6 — 7; трансформаторы

1б воспринятия считываемой информации, связанные на входе с электрической цепью прохождения токов переключения перекрестий матрицы, а на выходе — с усилителями 17 считывания, с выхода которых сигнал считывания подается через стробирующие ключи 18 на статический регистр 8.

Управление описываемым устройством выполняется полупроводниковыми схемами, причем усилители записи-считывания, связанные с логическими ключами б — 7 и работающие на общую нагрузку — каждая пара на один из 2 электродов матрицы 1, выполнены таким образом, что разнополярные импульсы с транзиторных усилителей 19 и 20 записи и считывания объединяются с помощью трансформаторного выхода 21. Трансформаторная связь схем управления с матрицей благоприятна для быстрого стекания паразитных зарядов перекрестий и для согласования импедансов и, кроме того, позволяет избежать гальванической связи с цепями переключения перекрестий матрицы.

В случаях, когда гальваническая связь допустима, трансформаторы заменяются усилителями с эмиттерным входом 22, шунтированным сопротивлением 23, и с общей базой, используемой для подачи стробирующего сигнала 24, Выходной сигнал снимается с коллекторной нагрузки

25. Так как коды записываются в плоскости матрицы так. что каждое слово располагается на перекрестиях, связанных с одним из 2 электродов на одной ее стороне и со всеми ортогональными электродами— с другой, то считывание производится в форсированном режиме не матричным способом, а с помощью одного импульса достаточно большой величины. Выдача считанной информации может производиться параллельно (через статический регистр 8) или последовательно (ерез магнитострикционную линию задержки) .

Таким образом, описываемое устройство обладает сравнительно с известными повышенной надежностью и быстродействием, что обусловливает промышленную полезность его применения.

Предмет изобретения

Запоминающее устройство «а сегнетоэлектрических матрицах с полупроводниковыми схемами управления и восстановлением информации после считывания, содержащее блок адресной селекции с диодным дешифратором, регистры и усилители и сочетающее параллельный принцип действия с возможностью последовательной выдачи через магнитострикционную линию задержки, о тл и ч а ю щ е е с я тем, что, с целью повышения надежности и быстродействия; схемы управления связаны с матрицей посредством трансформаторно-реостатных цепей, позволяющих устранить накопление паразитных зарядов и производить считывание в форсированном режиме. № 147025 № 1 17025 иг.

Фи г,3

Составитель описания А. И. Хохлов

Тсхред А. А, Кудрявицкая Корректор Ю. М. Федулова

Редактор Н. С. Кутафина

Г1одп. к печ, 24,V-62 r. Формат бум. 70 ;108 /, Объем 0,35 изд. л.

Зак. 4819 Тираж 700 Цена 4 коп.

ЦБТИ Комитета по делам изобретений и открытии при Совете Министров СССР

Москва, Центр, M. Черкасский пер., д 2/6

Типография ЦБТИ, Москва. Петровка, 14,