Устройство для сбора статистических данных о работе программ эвм

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в аппаратных и гибридных мониторах для получения статистических данных о работе программ. Цель изобретения - расширение функциональных возможностей за счет получения динамических характеристик вычислительного процесса. Устройство позволяет за счет вывода промежуточных результатов получить динамические характеристики вычислительного процесса. Счет событий вычислительного процесса осуществляется при помощи счетчика 2, результаты счета хранятся в блоке 1 памяти. Для счета событий служат регистр 4, триггер 7, распределитель 9 импульсов, элементы ИЛИ 11,12, мультиплексоры 14,15, элемент 2И-ИЛИ 17, формирователь 18. Для вывода промежуточных результатов счета служат счетчик 3, регистр 5, триггер 8, распределитель 10 импульсов, элемент ИЛИ 13, элемент И 16. Блок 6 анализа приоритета разрешает конфликтные ситуации между выводом результатов и счетом событий. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„1471202 А I (51) 4 G 06 F 15/36 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н Д BTQPCHGMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4278397/24-24 (22) 10.06.87 (46) 07.04.89. Бюл. № 13 (72) C.Ë.Óëûáèí и А.И.Ляхов (53) 681.3 (088,8) (56) Авторское свидетельство СССР № 960829, кл. С 06 F 11/30, 1980.

Авторское свидетельство СССР № 1128266, кл. С 06 F 15/36, 11/00, 1982. (54) УСТРОЙСТВО ДПЯ СБОРА СТАТИСТИЧЕСКИХ ДАННЫХ О РАБОТЕ ПРОГРАММ ЭВМ (57) Изобретение относится к вычислительной технике и может быть использовано в аппаратных и гибридных мониторах для получения статистических данных о работе программ. Цель изобретения — расширение функциональных возможностей за счет получения динамических характеристик вычислительного процесса. Устройство позволяет за счет вывода промежуточных результатов получить динамические характеристики вычислительного процесса. Счет событий вычислительного процесса осуществляется при помощи счетчика 2, результаты счета хранятся в блоке 1 памяти. Для счета событий служат регистр 4, триггер 7, распределитель 9 импульсов, элементы ИЛИ 11, 12, мультиплексоры 14, 15, элемент 2И-ИЛИ 17, формирователь 18. Для вывода промежуточных результатов счета служат счетчик 3, регистр 5, триггер 8, распределитель 10 импульсов, элемент ИЛИ 13, элемент И 16. Блок 6 анализа приоритета разрешает конфликтные ситуации между выводом результатов и счетом событий. 1 ил.

1471202

10

Изобретение относится к вычислительной технике и может быть использовано в аппаратных и гибридных мониторах для получения статистических данных о работе программ.

Цель изобретения — расширение функциональных возможностей эа счет получения динамических характерис-. тик вычислительного процесса.

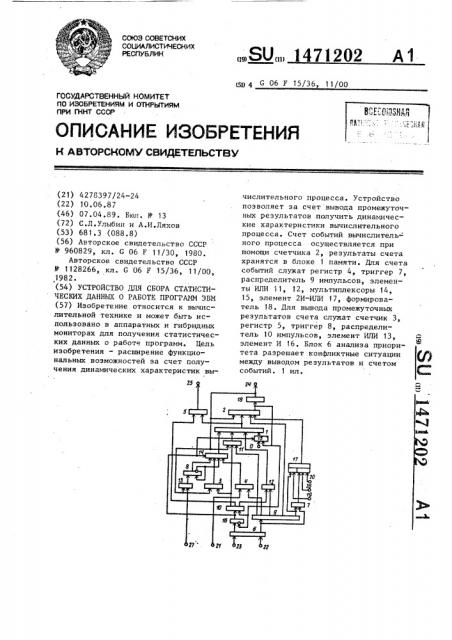

На чертеже представлена схема устройства.

Устройство содержит блок 1 памяти, первый 2 и второй 3 счетчики, второй 4 и первый 5 регистры, блок

6 анализа приоритета, первый 7 и второй 8 триггеры,.первый 9 и второй 10 распределители импульсов, первый 11, второй 12 и третий 13 элементы ИЛИ, первый 14 и второй 15 мультиплексоры, элемент И 16, элемент 2И-ИЛИ 17, формирователь 18 импульсов, первый 19 и второй 20 входы режимов устройства, вход 21 метки события устройства, входы признаков наступления события 22 и считывания 23, управляющий выход

24 признака перехода к другой половине блока памяти устройства и информационный выход 25 устройства, вход 26 меток времени и вход 27 переключения адреса блока памяти устройства.

Блок памяти предназначен для запоминания результатов счета частоты или длительности событий вычислительного процесса. Он имеет емкость

2 " и разрядных слов, где m - количество разрядов в метке события; и— максимальная разрядность промежуточных результатов. Этот блок (m+1)-м адресным разрядом делится пополам.

В одной половине хранятся текущие результаты счета, в другой— результаты, полученные в предыдущем интервале времени.и подлежащие считыванию. Переключение половин блока памяти происходит при достижении ь одним из результатов величины 2

Устройство может работать в одном из двух режимов: в режиме "Счет событий", который задается подачей единичного потенциала на вход 19 устройства, или в режиме "Измерение времени", который задается подачей единичного потенциала на вход 20 устройства.

В режиме "Счет событий" устройство работает следующим образом.

В исходном состоянии (цепи установки узлов устройства в исходное состояние на чертеже не показаны) все ячейки блока 1 памяти и счетчик

2 сброшены в "0". На вход 19 устройства подается единичный потенциал, на вход 20 устройства подается нулевой потенциал. С группы входов 21 устройства на информационный вход регистра 4 поступает метка со- . бытия вычислительного процесса (например, код операции). На первый вход блока 6 анализа приоритета с входа 22 устройства приходит признак,, говорящий о том, что на группе входов 21 находится новая метка события. Блок 6 анализа приоритета работает по принципу FIFO (первый пришел, первый обслужился), поэтому на первом выходе блока 6 анализа приоритета появляется сигнал, который поступает на вход сброса триггера 7, сбрасывая его в "0", и на вход распределителя 9 импульсов. На пяти выходах распределителя 9 импульсов, последовательно появляется "1".

Сигнал с первого выхода распределителя 9 импульсов поступает на первый вход элемента ИЛИ 11. Единичный сигнал с выхода элемента ИЛИ 11. поступает на вход записи блока памяти и записывает в ячейку, адрес которой приходит на группу адресных входов блока 1 памяти с группы выходов мультиплексора l4 информацию, приходящую на группу информационных входов блока 1 памяти группы выходов мультиплексора 15.

На управляющие входы мультиплексоров 14 и 15 приходит нулевой потенциал с выхода элемента И 16, поэтому на выходы мультиплексоров 14 и 15 приходит информация с их первых групп входов. Первая группа входов мультиплексора 14 соединена с выходами регистра 4, на котором хранится метка предыдущего события вычислительного процесса, и инверсным выходом триггера 8.

Первая группа входов мультиплексора 15 соединена с выходами счетчика 2, на котором хранится результат счета по предыдущему событию вычислительного процесса. Таким образом, результат счета по предыдущему событию записан в половину блока 1 па» мяти, определяемую триггером 8, в

1471202

10 ячейку, адресом которой является предыдущая метка события.

Сигнал с второго выхода распределителя 9 импульсов поступает на вход записи регистра 4 и записывает на него метку текущего события вычислительного процесса. С выходов регистра 4 метка события через мультиплексор 14 поступает на группу адресных входов блока 1 памяти.

Сигнал с третьего. выхода распределителя 9 импульсов поступает на первый вход элемента ИЛИ 12. Единичный сигнал с выхода элемента ИЛИ 12 15 поступает на вход считывания блока

1 памяти. На выходе блока 1 памяти появляется информация, хранящаяся в ячейке, адресом которой является метка события. Эта информация посту- 20 пает на информационные входы счетчика 2 и регистра 5.

Сигнал с четвертого выхода распределителя 9 импульсов поступает на вход записи счетчика 2 и записы- 25 вает на него информацию, приходящую из блока 1 памяти.

Сигнал с пятого выхода распределителя 9 импульсов поступает на установочный вход триггера 7, устанав- 30 ливая его в "1", и на первый вход элемента 2И-ИЛИ t7. На второй вход элемента 2И-ИЛИ 17 приходит единичный потенциал с входа 19 устройства.

На выходе элемента 2И-ИЛИ 17 появля35 ется сигнал, который поступает на счетный вход счетчика 2, увеличивая

его содержимое на "1". Первым тактом следующего цикла работы устройства содержимое счетчика 2 перепи- 4О сано в соответствующую ячейку блока

1 памяти. Таким образом, в ячейках, адресами которых являются метки событий, хранятся результаты счета этих событий. 45

Если в результате прибавления "1" к содержимому счетчика 2 полученный результат счета достигает величины

2 (т.е. в старшем разряде счетчика 2 появляется "1"), то устройство переключается на хранение результатов счета в другой половине блока.1 памяти (т.е. изменяет состояние триггера 8 на противоположное). Переключение осуществляется таким образом, что единичный сигнал с выхода старшего разряда счетчика 2 поступает на вход формирователя 18, инверсный вход элемента И 16 и вход сбро-са распределителя 10 импульсов. При этом блокируется элемент И 16, сбра- сывается в "0" распределитель 10 импульсов, а формирователь 18 формирует единичный сигнал определенной длительности. Сигнал с выхода формирователя 18 поступает ыа второй вход элемента ИЛИ 11, первый вход элемента ИЛИ 13 и входы сброса счетчиков

2 и 3. На выходе элемента ИЛИ 11 появляется сигнал, записывающий полученный на счетчике 2 результат счета (2 ) в соответствующую ему ячейку блока 1 памяти. Длительность сигнала, формируемого формирователем 18, должна быть не менее длительности цикла записи в блок 1 памяти. Задним фронтом этого сигнала обнуляются счетчики 2 и 3. Задним фронтом сигнала, приходящего с выхода элемента ИЛИ 13 на вход записи триггера 8, на триггер 8 записывается информации, приходящая на его информационный вход с инверсного выхода. Триггер 8 изменяет свое состояние на противоположное, что обеспечивает „ адресацию при счете частоты событий вычислительного процесса второй половины блока 1 памяти. Кроме того, сигнал с выхода формирователя 18 поступает на выход 24 устройства. Сигнал с выхода 24 устройства может быть заведен на вход прерывания технологической 3ВМ, которая организует .. считывание из блока 1 памяти проме-; жуточных результатов счета частоты или длительности событий вычислительного процесса.

В режиме "Измерение времени" устройство работает следующим образом.

Ка вход 20 устройства подается единичный потенциал, на вход 19 устройства подается нулевой потенциал. На информационный вход регист" ра 4 подается метка события вычислительного процесса (например, имя программы), длительность которого надо измерять. На первый вход блока 6 анализа приоритета проходит признак события (например, признак входа в программу). Далее работа устройства не отличается от работы в режиме "Счет событий" за исключением того, что сигнал с пятого выхода распределителя 9 импульсов . устанавливает триггер 7 в единичное состояние. Единичный потенциал с вы5 14 хода триггера 7 поступает на третий вход элемента 2И-ИЛИ 17, на четвертый вход этого элемента приходит единичный потенциал с .входа 20 устройства, а на лятыи вход — метки времени с входа 26 устройства. На ныходе элемента 2И-ИЛИ 17 появляются сигналы с частотой меток времени.

Эти сигналы поступают на счетный вход счетчика 2. Процесс счета. будет прерван при появлении в вычислительном процессе ноного события, о чем известит сигнал на входе 22 устрой, ства. При этом на первом выходе блока 6 анализа приоритета выработан сигнал, передний фронт которого сбрасывает триггер 7 в "0", Считывание результатов счета из блока 1 памяти организуется таким образом, что по получению сигнала с выхода 24 устройства технологическая ЭВМ переходит к выполнению программы считывания промежуточных результатов. Технологическая ЭВМ подает на вход 23 устройства сигнал, который поступает на второй вход блока 6 анализа приоритета.

На втором выходе блока 6 анализа приоритета появляется единичный по— тенциал, который поступает на вход элемента И 16, с выхода которого единичный потенциал поступает на управляющие входы мультиплексоров

14 и 15. На группу выходов мультиплексора 14 проходит информация с

его второй группы входов, которая соединена с выходами счетчика 3 и прямым выходом триггера 8. На группу выходов мультиплексора 15 проходит нулевая информация, которая скоммутирована на его второй группе входов. Таким образом, на группу информационных входов блока

1 памяти подана нуленая информация, а группа адресных нходов блока 1 памяти соединена с группой выходов счетчика 3 и прямым выходом триггера 8.

Кроме того, сигнал с выхода элемента И 16 подается на вход распределителя 10 импульсов, на трех выходах которого последовательно вырабатывается единичный сигнал.

Сигнал с первого выхода распределителя 10 импульсов поступает на второй вход элемента ИЛИ 12. Единичный сигнал с выхода элемента ИЛИ 12 считывает информацию из ячейки бло71202 6 ка 1 памяти, адресуемой счетчиком 3 и триггером 8. Считанная информация поступает с выхода блока 1 памяти на информационный вход регистра 5. t0

Сигнал с второго выхода распределителя импульсов поступает на вход записи . регистра 5 и записывает в него считанную из блока 1 памяти информацию. Информация с выхода регистра 5 поступает на группу 25 выходов устройства, которая может быть соединена с входом технологической ЭВМ.

Сигнал с третьего выхбда распределителя 10 импульсов поступает на третий вход элемента ИЛИ 11, сигнал с выхода которого записывает н считанную ячейку блока 1 памяти нулевую информацию.. KpoMe того, сигнал с третьего выхода распределителя импульсов поступает на счетный вход счетчика 3 и задним фронтом увеличивает содержимое этого счетчика на единицу.

Если во время процесса считывания н старшем разряде счетчика 2 появится "1", то процесс считывания будет приостановлен: распределитель

10 импульсов будет обнулен, а элемент И 16 заблокирован. При пропадании единичного сигнала с выхода старшего разряда счетчика 2 элемент И 16 разблокируется, сигнал с второго выхода блока 6 анализа приоритета вновь поступит на вход распределителя 10 импульсов и процесс считывания будет повторен.

Для того, чтобы по окончании счета частоты или длительности событий считать из блока 1 памяти последние результаты счета, необходимо подать единичный сигнал на вход 27 устройства.

Этот сигнал поступает на второй вход элемента ИЛИ 13. Сигнал с выхода элемента ИЛИ 13 изменяет состояние триггера 8 на противоположное, что обеспечивает при считывании адресацию той половины блока 1 памяти, н которой хранятся последние результаты счета.

Таким образом, предлагаемое устройство позволяет получить динамические характеристики вычислительного процесса за счет вывода промежуточных результатов в технологическую 3ВМ.

1471202

Формула изобретения

40 Устройство для сбора статистических данных о работе программ ЗВИ, содержащее первый триггер, элемент

И, первый .распределитель импульсов, первый и второй элементы ИЛИ, первый мультиплексор, блок памяти и первый регистр, причем группа выходов пер- 10 вого мультиплексора соединена с группой адресных входов блока памяти, выход которого соединен с информационным входом первого регистра, выход которого является информационным 15 выходом устройства, о т л и ч а ю— щ е е с я тем, что, с целью расширения функциональных возможностей за счет получения динамических характеристик вычислительного процесса, 20 устройства содержит блок анализа приоритета, второй распределитель импульсов, третий элемент ИЛИ, два счетчика, второй регистр, второй триггер, элемент 2И-ИЛИ, второй муль- 25 типлексор и формирователь импульсов, причем первый и второй входы блока анализа приоритета являются соответственно входами признака наступления события и считывания устройства,пер- 30 вый выход блока анализа приоритета соединен с входом пуска первого распределителя импульсов и входом сброса первого триггера, первый, второй, третий и четвертый выходы первого распределителя импульсов соединены соответственно с первым входом первого элемента ИЛИ, входом записи второго регистра, первым входом второго элемента ИЛИ и входом записи первого счетчика, установочный вход первого триггера и первый вход эле— мента 2И-ИЛИ соединены с пятым выходом первого распределителя импульсОВ, разряды инфОрмациОННОгo ВыхОда 45 первого счетчика подключены к первой группе информационных входов второго мультиплексора, старший разряд информационного выхода первого счетчика подключен к входу формирователя импульсов, входу сброса вто50 рого распределителя импульсов и ин. версному входу элемента И, выход которого соединен с входом пуска второго распределителя импульсов и управляющими входами первого и вто55 рого мультиплексоров, информацион- ный вход первого счетчика соединен с выходом блока памяти, входы записи и считывания которого соединены с выходами соответственно первого и второго элеменFQB ИЛИ, выход формирователя импульсов соединен с входами сброса первого и второго счетчиков, первым входом третьего элемента ИЛИ, вторым входом .первого элемента ИЛИ и является управляющим выходом признака перехода к другой половине блока памяти устройства, вход переключения адреса блока памяти устройства подключен к второму ,входу третьего элемента ИЛИ, выход которого соединен с .синхровходом второго триггера, инверсный и прямой выходы которого соединены со старшими разрядами соответственно первой и второй групп информационных входов первого. мультиплексора, инверсный выход второго триггера соединен с его информационным входом, группа выходов второго регистра соединена с первой группой информационных входов первого мультиплексора, группа информационных выходов второго счетчика соединена с второй группой информационных входов первого мультиплексора, информационный вход второго регистра является входом метки события устройства, группа информационных входов блока памяти соединена с группой выходов второго мультиплексора, вторая группа информационных входов которого подключена к шине нулевого потенциала устройства, первый и второй выходы второго распределителя импульсов соединены соответственно с вторым входом второго элемента ИЛИ и входом записи первого регистра, третий выход второго распределителя импульсов соединен с третьим входом первого элемента ИЛИ и счетным входом второго счетчика, счетный вход первого счетчика соединен с выходом элемента 2И-ИЛИ, второй и третий входы которого являются соответственно первым и вторым входами режимов устройства, четвертый вход элемента

2И-ИЛИ является входом меток времени устройства, пятый вход элемента

2И-ИЛИ соединен с выходом первого триггера, второй выход блока анализа приоритета соединен с прямым входом элемента И.