Устройство для управления мостовым транзисторным инвертором

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и предназначено для использования во вторичных источниках питания и электроприводах переменного тока, выполняемых на высоковольтных транзисторах с бестрансформаторным входом. Цель изобретения заключается в повышении КПД за счет импульсного подключения делителей напряжения к источнику питания. Предложенное устройство содержит задающий генератор 1, делитель частоты 2, формирователи основных импульсов 3 с трансформаторным выходом, силовые 23,24, дополнительные 25,26 и вспомогательные транзисторы 27,28, а также резистивные делители напряжения 29-32. Сущность решения основана на подключении делителей напряжения через вспомогательные транзисторы параллельно переходу коллектор-эмиттер силовых транзисторов, а дополнительных параллельно их база-эмиттерным переходам. Перед моментом включения вспомогательный транзистор напряжение на делителе включает дополнительный транзистор и тем самым не позволяет открыться очередному силовому транзистору до полного выключения ранее работающего. Одновременно переход коллектора-база закрывающегося выводится в активную область, что способствует сокращению времени выключения силовых транзисторов. 1 ил.

СОЮЗ СОВЕТСХИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК д1) 4. Н 02 М 7/537

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4184292/24-07 (22) 19.01.87 (46) 07.04.89. Бюл. Р 13 (71) Научно-исследовательский институт автоматики и электромеханики при

Томском институте автоматизированных систем управления и радиоэлектроники (72) В.И.Авдзейко и А.В.Федоров (53) 621.314.58 (088.8) (56) Авторское свидетельство СССР

1101998, кл. Н 02 M 7/5387, 1984.

Авторское свидетельство СССР

Р 1415386, кл. Н 02 М 7/537, 1986. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ МОСТОВЫИ ТРАНЗИСТОРНЫМ ИНВЕРТОРОМ (57) Изобретение относится к электротехнике и предназначено для использования во вторичных источниках питания и электроприводах переменного тока, выполняемых на высоковольтных транзисторах с бестрансформаторным входом. Цель изобретения заключается в повьппении КПД за счет импульсного подключения делителей напряжения к

„„SU„„1471271 А1 источнику питания. Предложенное устройство содержит задающий генератор делитель частоты 2, формирователи основных импульсов 3 с трансформаторным выходом, силовые 23,24, дополнительные 25,26 и вспомогательные транзисторы 27,28, а также резистивные делители напряжения 29-32. Сущность решения основана на подключении делителей напряжения через вспомогательные транзисторы параллельно переходу коллектор-эмиттер силовых транзисторов, а дополнительных параллельно их база-эмиттерным переходам. Перед моментом включения .вспомогательный транзистор напряжения на делителе включает дополнительный транзистор и тем самым не позволяет открыться очередному силовому транзистору до полного выключения ранее работающего.

Одновременно переход коллектора — база закрывающегося выводится в активную область, что способствует сокращению времени выключения силовых транзисторов. 2 ил.

14712

Изобретение относится к электротехнике и может быть использовано в преобразователях постоянного напряжения в низкочастотное переменное для систем вторичного электропитания и электропривода.

Цель изобретения — повышение КПД за счет импульсного подключения делителей напряжения к источнику питания. 1ð

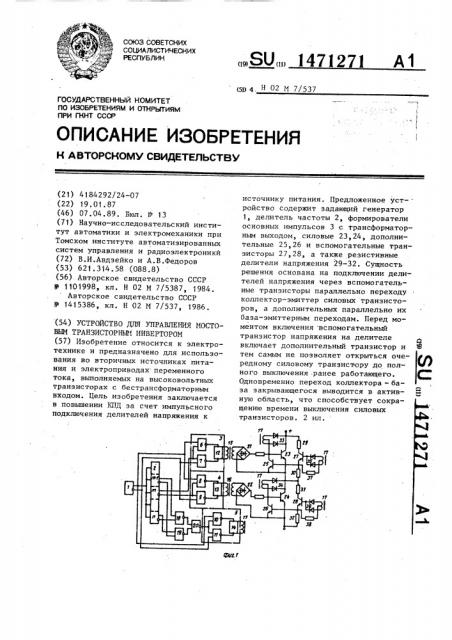

На фиг. 1 представлена схема устройства; на фиг. 2 — временные диаграммы напряжений.

Схема управления содержит задающий генератор 1, делитель 2 частоты, основной 3, дополнительный 4 и вспомогательный 5 формирователи импульсов, выполненные на элементах И-НЕ 2

6-11, усилителях 12-14 мощности и выходных трансформаторах 15-17, до- 2р полнительные элементы И-НЕ 2 18-20, основные выпрямители 21 и 22, силовые 23 и 24, дополнительные 25 и 26 и вспомогательные 27 и. 28 транзисторы, делители 29-32 напряжения на ре- 25 зисторах, дополнительные 33 и 34 и вспомогательные 35 и 36 выпрямители и ограничительные резисторы 37 и 38.

Прямой выход задающего генератора 1 связан с первыми входами всех форми-. 3p рователей импульсов и с входом делителя 2 частоты, инверсный выход задающего генератора подключен к вторым входам формирователей 3-5 импульсов. Прямой основной выход делителя

2 частоты подключен к третьему входу основного формирователя импульсов, а инверсный к третьему входу дополнительного 4 формирователя импульсов.

Дополнительные 18 и 19 элементы И-НЕ 4р

2 первыми входами соединены с прямым и инверсным выходами (m-!) ячейки делителя 2 частоты, а вторые входы этих элементов с инверсным и прямым выходами и ячейки делителя 2 частоты.

Выходы элементов 18 и 19 И-НЕ 2 связаны с входами третьего 20 дополнительного элемента И-НЕ 2, соединенного выходом с третьим входом вспомогательного формирователя 5 импульсов.

Все схемы формирователей импульсов выполнены на двух элементах 6-7, 8-9, 10-11 И вЂ” НЕ 2 и усилителях 12-14 мощности с выходными трансформаторами

15-17. Первые входы элементов 6-11

И-НЕ 2 образуют первые и вторые входы формирователей импульсов, а вторые входы элементов И-НЕ 2 объединены и образуют третьи входы формирователей.

71 2

Выходные обмотки трансформаторов 15 и 16 основного 3 и дополнительного 4 формирователей импульсов через выпрямители 21 и 22 подключены к переходам база — эмиттер верхнего 23 и нижнего

24 силовых транзисторов стойки инвертора. Делители напряжения на резисторах 29, 30 и 31, 32 связаны с переходами коллектор — эмиттер силовых транзисторов, при этом резисторы 29 и 30, а также 31 и 32 связаны между собой через вспомогательные транзисторы 27 и 28. Выходные обмотки трансформатора 17 через выпрямители 33 и 34 подключены к переходам коллектор — база силовых транзисторов, а также через выпрямители 35 и 36 и ограничительные резисторы 37 и 38 к переходам база— эмиттер вспомогательных транзисторов

27 и 28, эмиттеры которых связаны с базами дополнительных транзисторов

25 и 26, коллекторами подключенных к базам, а эмиттерами.к эмиттерам силовых транзисторов 23 и 24 °

На фиг. 2 показаны временные диаграммы напряжения: 39 — задающего генератора, 40-42 — соответственно на выходе m m"1 и и ячеек делителя частоты, 43 — íà выходе первого дополнительного 18 элемента И-НЕ 2; 44на обмотках трансформатора 15 усилителя 12 мощности, 45 — на обмотках трансформатора 17 усилителя. 14 мощности, 46 — на обмотках трансформа-. тора 16 усилителя 13 мощности, 47 на переходе база — эмиттер силового транзистора 24.

Работа схемы управления осущест-вляется следующим образом.

На первые и вторые входы формирователей 3-5 импульсов подаются напряжения с прямого и инверсного выходов задающего генератора 1 (диаграмма 39, фиг. 2). Формирователи начинают ра-. ботать, если на третьи входы их подаются сигналы логической "1". Допустим, что на третий вход формирователя 3 основных импульсов в момент времени t --t„ поступает с выхода г ячейки m делителя частоты сигнал логической "1" (диаграмма 40). Усилитель 12 мощности работает на частоте задающего генератора (диаграмма 39) и на обмотках трансформатора 15 формирует напряжение 44, под действием которого силовой транзистор 23 открыт. На третьи входы дополнительного 4 и вспомогательного 5 формирова14712 телей импульсов подается сигнал "0 и усилители 13 и 14 мощности не работают.

В момент времени t на вход дополнительного элемента подается сигнал логической " 1" и на третий вход вспомогательного 5 формирователя импульсов поступает сигнал логической

"1", поэтому на обмотках трансформа- !О тора 17 формируется пачка импульсов, показанная на диаграмме 45. Под действием напряжения на обмотках трансформатора 17 открываются вспомогательные транзисторы 27 и 28. Вслед- 15 ствие того, .что силовой транзистор

23 открыт, напряжение питания инвертора приложено к резисторам 31 и 32 делителя напряжения, под действием которого дополнительный тран- 20 зистор 26 открыт. В момент времени

t< происходит переключение выходных напряжений на основных выходах делителя 2 частоты. На третий вход формирователя 3 основных импульсов подается "0" и усилитель 12 мощности выключается. Одновременно на третий вход дополнительного 4 формирователя импульсов подается сигнал логической

"1"., усилитель 13 мощности начинает 30 работать и на обмотках трансформатора 16 формируется напряжение 46. Одка транзистор 24 не открывается, так как его база — эмиттерный переход шунтируется открытым дополнительным транзистором 26 — диаграмма 47 (t

). После окончания процесса расса3 сывания избыточных носителей транзистор 23 закрывается (t ) . Вспомо,3 гательные транзисторы 27 и 28 под 40 действием напряжения 45 открыты, поэтому при закрывании транзистора 23 падение напряжения на резисторе 32 уменьшается, значительно уменьшается базовый ток дополнительного транзис- 45 тора 26 и он заркывается в момент времени t . Напряжение 46 на обмотке трансформатора 16 открывает транзистор 24 при полном закрывании транзистора 26. Далее процесс управления инвертором повторяется.

В течение времени t -t напряжение трансформатора 17 открывает не только вспомогательные транзисторы

27 и 28, но и смещает переход коллектор — база открытого транзистора в активную ббласть. При этом часть базового тока начинает протекать через диоды дополнительных выпрями71 телей 33 и 34, обеспечивая к моменту выключения коэффициент насьпцения открытого транзистора 23 или 24 близким к единице.

Таким образом, введение вспомогательного формирователя импульсов, делителей напряжения и вспомогательных транзисторов позволяет повысить КПД схемы. Вспомогательные транзисторы

27 и 28 включены только в течение части периода выходного напряжения, поэтому цепь из резисторов 29-32 дает небольшие потери, эначитепьно снижая потери при переключении транзисторов 23 и 24. Время выключения транзисторов дополнительно уменьшается за счет использования импульсного источника в цепи коллектор — база силовых транзисторов. При этом статические потери возрастают незначительно, особенно при низкой частоте выходного напряжения. Промежуток времени t„ -t выбирается для обеспечения к моменту выключения величины коэффициента насыщения, равной единице, а промежуток времени t -t определяется временем рассасывания и выключения силовых транзисторов.

Формула изобретения

Устройство для управления мостовым транзисторным инвертором, содержащее задающий генератор, основной формирователь импульсов с выходным трансформатором, дополнительные транзисторы, дополнительные выпрямители, делители напряжения, выполненные на резисторах, предназначенные для подключения первыми выводами к переходам коллектор — эмиттер силовых транзисторов, нижние резисторы делителей вторым выводом связаны с базами дополнительных транзисторов, предназначенных для подключения переходом коллектор — эмиттер к переходу база — эмиттер силовых транзисторов, о т л и— ч а ю щ е е с я тем, что, с целью повьппения КПД за счет импульсного подключения делителей напряжения к источнику питания, оно снабжено делителем частоты, дополнительным и вспомогательным формирователями импульсов с выходными трансформаторами, тремя дополнительными элементами

И-НЕ 2, двумя основными и двумя вспомогательными выпрямителями, двумя вспомогательными транзисторами, двуЧЗ

Составитель В.Бунаков

Редактор Г.Гербер Техред Л.Олийнык Корректор С.Черни

Заказ 1615/54 Тираж 645 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГЕНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,103

5 14712 мя ограничительными резисторами, причем каждый формирователь импульсов содержит два элемента И-HF. 2 и усилитель мощности, первые входы элементов И-HF 2 образуют первый и вто5 рой входы формирователей, вторые входы элементов И-НЕ 2 связаны с, входами усилителей мощности, выходы которых подключены к первичным обмоткам выходных трансформаторов, делитель частоты выполнен на основе кольцевой пересчетной схемы на и ячейках с прямым и инверсным выходами, выходы m-й ячейки являются основными выходами делителя частоты, прямой выход задающеro генератора связан с входом делителя частоты и с первыми входами основного, дополнительного и вспомогательного формирователей импульсон, инверсный выход задающего генератора подключен. к вторым входам формирователей импульсов, прямой и инверсный : оановные выходы делителя частоты подклю- 2Б чены к третьим входам соответственно основного и дополнительного формирователей импульсов, первый и второй дополнительные элементы И-НЕ 2 пер-. выми входами связаны соответствен- 30 но с прямым и инверсным выходами

m-1 ячейки делителя частоты, а вторыми входами — с прямым и инверсным выходами и-й ячейки, выходы элементов И-НЕ 2 подключены к входам третьего дополнительного элементов

И-HE 2, выходом связанного с третьим входом вспомогательного формирователя импульсов, вторичные обмотки выходных трансформаторов основного и дополнительного формирователей импульсов через первый и второй основные выпрямители предназначены для подключения к переходам база-эмиттер верхнего и нижнего силовых транзисторов, основные выходные обмотки в вспомогательного формирователя импульсов подсоединены крайними выводами к входам дополнительных выпрямителей, а средней точкой предназначены для подключения к базам силовых транзисторов, дополнительные обмотки трансформатора вспомогательного формирователя импульсов через последовательно включенные ограничительные резисторы и вспомогатепьные выпрямители связаны с переходом база — эмиттер вспомогательных транзисторов, коллекторы которых подключены к второму выводу верхних резис-. торов делителей напряжения, а эмиттеры — к второму выводу нижних резисторов делителей напряжения.