Транзисторный ключ

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в устройствах для передачи импульсных сигналов через трансформатор в нагрузку, например в кабельную магистраль. Целью изобретения является увеличение амплитуды выходного сигнала и уменьшение рассеиваемой мощности за счет снижения потерь в выходной цепи устройства. Для достижения цели сигнал перегрузки формируется на вторичной обмотке выходного трансформатора и поступает через компаратор на вход R триггера с динамическим входом, вход S триггера подключен к шине управления, а выход через инвертор блокирует запуск выходного транзистора. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51) 4 Н 03 К 17/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4200890/24-21 (22) 24.02.87 (46) 07 ° 04.89. Бюл. У 13 (72) О.И.Зайцев, Е.С.Комарова, Ф.О.Коньков и В.P.Øâàðöáåðã (53) 62 1.316 (088.8) (56) Заявка Японии Ф 57-28216, кл. Н 03 К 17/08, 1982.

Источник электропитания вторичный ВИП. — Техническое описание

ПХ2.087.059ТО, 1984. (54) ТРАНЗИСТОРНЫЙ КЛЮЧ (57) Изобретение относится к импульсной технике и может быть использовано в устройствах для передачи

Изобретение относится к импульсной технике и может быть использовано в устройствах для передачи импульсных сигналов через трансформатор в нагрузку, например в кабельную магистраль.

Цель изобретения — увеличение амплитуды выходного сигнала и уменьшение рассеиваемой мощности путем снижения потерь в выходной цепи устройства.

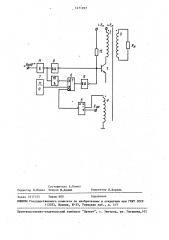

На чертеже представлена электрическая принципиальная схема транзисторного ключа.

Транзисторный ключ содержит выходной транзистор 1, развязывающий трансформатор с первичной 2, вторичной 3 и дополнительной 4 обмотками,компаратор 5, элемент памяти в виде триггера 6 с инверсным динамическим единичным S-входом и двумя инверсными динамическими нулевыÄÄSUÄÄ 1 71297 А1 импульсных сигналов через трансформатор в нагрузку, например в .кабельную магистраль. Целью изобретения является увеличение амплитуды выходного сигнала и уменьшение рассеиваемой мощности эа счет снижения потерь в выходной цепи устройства.

Для достижения цели сигнал перегрузки формируется на вторичной обмотке выходного трансформатора и поступает через компаратор на вход R триггера с динамическим входом, вход S триггера подключен к шине управления, а выход через инвертор блокирует запуск выходного транзистора. 1 ил.

2 ми R-входами, генератор 7 опроса, первый и второй инверторы 8 и 9 с открытыми коллекторами, третий и

- четвертый инверторы 10 и 11 и ре« зистор 12. При этом вход инвертора

11 подключен к входной клемме, а выход — к входу инвертора 8 и к вхо . ду инвертора 10. Выход инвертора 8 подключен к базе выходного транзистора 1, эмиттер которого подключен к общей шине, а между коллектором которого и шиной источника питания включена первичная обмотка

2 развязывающего трансформатора, между базой выходного транзистора 1 и шиной +5В включен резистор 12, нагрузка подключена к вторичной обмотке 3 развязывающего трансформатора, а дополнительная обмотка 4 развязывающего трансформатора включена между общей шиной и инверсным входом компаратора 5, выход инвертора 10

1471297

1О

55 подключен к инверсному динамическому единичному S-входу триггера 6, выход генератора 7 опроса подключен к первому инверсному динамическому нулевому R-входу триггера 6, а выход компаратора 5, прямой вход которого подключен к источнику опорного напряжения, подключен к второму инверсному динамическому нулевому Rвходу триггера 6. Выход последнего подключен к входу инвертора 9, а его выход - к базе выходного тран зистора 1.

Транзисторный ключ работает следующим образом.

В исходном состоянии импульсы на вход устройства не подаются. На входе присутствует напряжение логического нуля сигнала 0-0,4В. На выходе генератора 7 опроса постоян— но присутствует импульсный сигнал прямоугольной формы низкой частоты (к примеру, 1-100 Гц), который по своему заднему фронту устанавливает триггер 6 в состояние логического нуля по выходу (на выходе напряжение

0-0,4В). Дальнейшего изменения состояния триггера 6 в статическом состоянии не происходит. Входной постоянный сигнал с напряжением логического нуля 0-0,4 В, присутствующий на входе инвертора 11, вызывает на выходе этого элемента напряжение ,логической единицы амплитудой 2,45В которое поступает на вход инвертора 10 и вход инвертора 11 что, в свою очередь, переводит эти элементы в состояние логического нуля по выходу. Поскольку, триггер 6 находится в состоянии логического нуля по выходу, то инвертор 9 по выходу отключен и не влияет на входной сигнал. Ток от источника питания через резистор 12 поступает на выход инвертора 8, и выходной транзистор 1 закрыт. Сигнала на нагрузке нет, следовательно амплитуда напряжения на инверсном входе компаратора 5 меньше напряжения порогового напряжения, и на выходе компаратора присутствует напряжение логического нуля.

С приходом импульса напряжения логической единицы на вход устройства на выходе инвертора 11 появляется напряжение логического нуля, которое отключает по выходу инвертор 8 и вызывает на выходе инвертора

10 напряжение логической единицы, которое не меняет состояние триггера 6. Ток от источника питания через резистор 12 поступает в базу выходного транзистора 1 и открывает его.

Через первичную обмотку 2 раэвязывающего.трансформатора протекает ток, а на нагрузке, подключенной к вторичной обмотке 3 трансформатора, также протекает ток и возникает импульс напряжения, который появляется и на дополнительной обмотке 4 трансформатора. Амплитуда и форма сигнала напряжения на дополнительной обмотке 4, подключенной к инверсному входу компаратора 5, повторяет амплитуду и форму сигнала напряжения на нагрузке, подключенной к вторичной обмотке 3 раэвязывающего трансформатора. При напряжении на нагрузке (и на дополнительной обмотке 4), превышающем напряжение опорного источника, компаратор 5 переходит в состояние логической единицы по выходу, что также не меняет состояние триггера 6. После окончания действия входного импульса (на входе инвертора 11 появляется напряжение логического нуля) на выходе инвертора 10 также происходит перепад напряжения от состояния логической единицы в состояние логического нуля, и триггер 6 переходит в состояние логической единицы по выходу. Выходы инверторов 8 и 9 находятся в состоянии логического нуля по выходу,.и ток через резистор

12 от источника питания поступает на выходы этих элементов. Выходной транзистор закрывается. На нагрузке формируется спад выходного сигнала.

Одновременно спад выходного напряжения происходит и на дополнительной обмотке 4 развязывающего трансформатора. При уменьшении амплитуды сигнала на инверсном входе компаратора 5 оно становится меньше, чем напряжение от порогового источника на его прямом входе, и на выходе компаратора происходит изменение сигнала от состояния логической единицы в состояние логического нуля.

Поскольку это изменение поступает на второй инверсный динамический нулевой R-вход триггера 6 позже, чем изменение, приходящее на инверсный динамический единичный S-вход триггера 6 за счет задержки сигнала

1471297 в выходном транзисторе 1, развязывающем трансформаторе и компараторе 5, то триггер 6 опять меняет свое состояние и переходит в состояние логического нуля на выходе, и элемент 9 отключается по выходу.Ток от источника питания через резистор

12 поступает на выход инвертора 8.

Устройство готово к приему следующего входного импульса.

В случае, если .на вторичной обмотке 3 развязывающего трансформато.ра присутствует режим короткого замыкания или амплитуда его меньше пороговой, то во всех случаях амплитуда сигнала на дополнительной обмотке 4 меньше напряжения опорного источника и на выходе комнаратора постоянно присутствует напряжение логического нуля. После окончания входного импульса триггер 6 меняет свое состояние, как было описано и уже постоянно остается в таком состоянии . На выходе инвертора 9 постоянно присутствует напряжение логического нуля, выходной транзистор 1 отключен,и его состояние не зависит от сигнала на входе устройства. В дальнейшем триггер 6 может изменить свое состояние только по заднему фронту сигнала от генератора 7 опроса. В случае, если на нагрузке режим короткого замыкания отсутствует, устройство автоматически возобновляет свою работу, а если режим короткого замыкания присутствует, выходной транзистор 1 опять отключается до следующего заднего

5 фронта сигнала от генератора 7 onроса.

Ф о р м у л а и з о б р е т е н и я

1р Транзисторный ключ, содержащий выходной транзистор, у которого в коллекторную цепь включена первичная обмотка развязывающего трансформатора, а вторичная обмотка соединена с нагрузкой, первый инвертор, у которого вход соединен с шиной управления, а выход — с базой выходного транзистора, компаратор, у ко- . торого первый вход соединен с шиной источника опорного напряжения, второй вход — с шиной защищаемой цепи, а выход — с R-входом элемента памяти, выход элемента памяти через второй инвертор соединен с

25 базой выходного транзистора, и третий инвертор, о т л и ч а ю— шийся тем, что, с целью увеличения амплитуды выходного сигнала и уменьшения рассеиваемой мощности, gp элемент памяти выполнен в виде RSтриггера с динамическими входами, у которого S-вход через третий инвертор соединен с шиной управления, а шина защищаемой цепи соединена с дополнительной вторичной обмоткой развязывающего трансформатора.

1471297

Составитель А.Бомко

Редактор Н.Яцола Техред М.Дидык

Корректор Н.Король

Заказ 1617/55 Тираж,880 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101