Резервированный делитель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в мажоритарно-резервируемых синхронизирующих устройствах. Цель изобретения - повышение надежности работы при одновременном увеличении стабильности выходной частоты за счет "жесткой" синхронизации счетчиков 4 импульсов трех резервируемых каналов 1, 2 и 3, а также отсутствие искажения сигнала на выходных шинах 13, 14 и 15 устройства при сбое одного из счетчиков 4 - достигается за счет введения в каждый канал инвертора 7, формирователей 8 и 9 импульсов. В устройстве также имеются входные шины 10, 11 и 12, мажоритарный элемент 5 и элемент 6 эквивалентности. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1471310 А 2 дц 4 Н 03 К 23/66

: н., 1

F, „„f

„1;.;-", I

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ПЛАНТ СССР (61) 645282 (21) 4285403/24-21 (22) 15.07.87 (46) 07.04.89. Бюл. ¹ 13 (72) А.Г.Климашев и А,M.Ïîïîâ (53) 621.374.3(088.8). (56) Авторское свидетельство СССР № 645282, кл. Н 03 К 23/66, 12.09.77. (54) РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к импульсной технике и может быть использовано в мажоритарно-резервируемых синхронизирующих устройствах. Цель изобретения — повышение надежности работы при одновременном увеличении стабильI ности выходной частоты за счет жесткой" синхронизации счетчиков 4 им- пульсов трех резервируемых каналов

1, 2 и 3, а также отсутствия искажения сигнала на выходных шинах 13, 14 и 15 устройства при сбое одного из счетчиков 4 — достигается за счет введения в каждый канал инвертора 7> формирователей 8 и 9 импульсов. В устройстве также имеются входные шины 10, 11 и 12,.мажоритарный элемент

5 и элемент 6 эквивалентности. 2 ил..

1471310

Изобретение относится к импульсной технике, может применяться в мажоритарно-резервированных цифровых синх- ронизирующих устройствах и являет5 ся усовершенствованием изобретения по авт.св. Н - 645282.

Цель изобретения †. повышение надежности работы при одновременном увеличении стабильности выходной час- 10 тоты за счет "жесткой" синхронизации счетчиков импульсов трех каналов, а также отсутствия искажения сигнала на выходных шинах устройства при сбое одного из счетчиков импульсов. 15

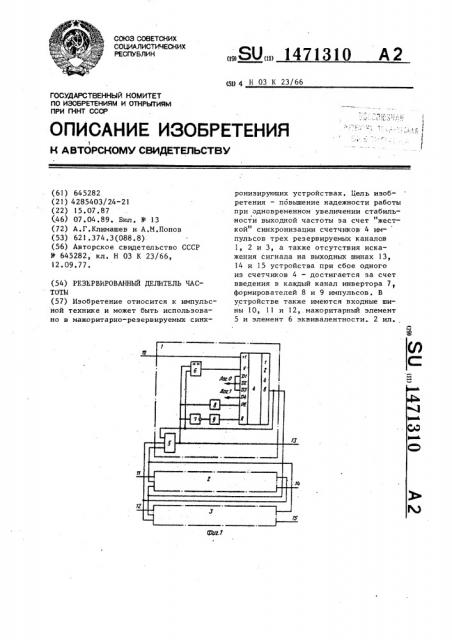

На фиг.1 представлена электрическая функциональная схема резервированного делителя частоты; на фиг.2— временные диаграммы, поясняющие его работу. 20

Устройство содержит три канала

1-3, каждый из которых состоит из счетчика 4 импульсов, мажоритарного элемента 5, элемента 6 эквивалентности, инвертора 7 и формирователей 8 и 9 импульсов. Кроме того, устройство содержит входные 10-12 и выходные

13-15 шины соответственно каждого канала 1-3. Счетный вход счетчика 4 импульсов соединен с входной шиной 30

10 (11,12) соответствующего канала

1 (2, 3), выход мажоритарного элемента 5 соединен с выходной шиной 13 (14,15) соответствующего канала 1 (2,3), с первым входом элемента 6 эк- 35 вивалентности, через первый формирователь 8 импульсов — с входом разрешения записи параллельного кода счетчика 4 импульсов и через последовательно соединенные инвертор 7 и - 40 второй формирователь 9 импульсов— с входом установки в "0" счетчика 4 импульсов, выход старшего разряда которого соединен с вторым входом элемента 6 эквивалентности и с соответ- 45 ствующим (номеру канала) входом мажоритарного элемента 5 каждого из каналов 1-3. Информационный вход старшего разряда счетчика 4 импульсов co1l 11 единен с шиной логической 1, информационные входы . остальных разряtl Н дов — с шиной логического 0

Принцип работы делителя состоит в том, что при подаче на шины 10-12 счетных импульсов от трех асинхронных генераторов на шинах 13-15 появляются синхронные по трем каналам и

1-3 сигналы пониженной в 2 частоты, где N — разрядность счетчика 4.

Резервированный делитель частоты работает следующим образом.

При включении питания счетчики

4 устанавливаются в произвольное состояние (фнг.2а). На выходе элемен— та 5 (фиг.2б) поддерживается логический уровень, соответствующий уровню большинства выходов старшего разряда счетчиков 4 каналов 1-3. В тех каналах, где логический уровень на выходе старшего разряда счетчика 4 совпадает с уровнем на выходе элемента 5, на выходе элемента 6 (фиг.2в) устанавливается уровень логической

"1", и счетчики 4 этих каналов пересчитывают свои последовательности импульсов, В процессе счета логический уровень на выходе старшего разряда счетчиков 4 изменяется на противоположный, По принципу большинства (два из трех) логический уровень на выходе элемента 5 также изменяется на противоположный, что обеспечивает возбуждение в каждом канале 1-3 того формирователя 8 или 9, на входе которого произошло изменение логического уровня с "0" на "1".

При смене логического уровня на выходе элемента 5 с "0" на "1" на выходе формирователя 8 в каждом канале

1-3 формируется импульс записи параллельного кода (фиг.2г) в счетчики 4.

В старший разряд счетчика 4 записывается логическая "1", а в остальные разряды — "0", что соответствует состоянию двоичного суммирующего счетчика при смене кода в старшем разряде с "0" на "1". При смене логического уровня на выходе элемента 5 с "1" на

"0" благодаря инвертору 7 уровень на входе формирователя 9 изменяется с

"0",на "1", и на выходе формирователя

9 каждого канала 1-3 формируется импульс сброса (фиг.2д). Во все разряды счетчика. 4 записывается логический "0, что соответствует состоянию двоичного суммирующего счетчика при смене кода в старшем разряде с

"1" на "0". Таким образом обеспечивается автоматическая синхронизация устройства по трем каналам не только при включении питания, но и при случайном сбое любого из каналов

1-3.

После синхронизации логический уровень на выходе старшего разряда счетчика 4 в каждом канале 1-3 совпадает с уровнем на выходе элемен1471310

Фиг. 2 та 5. На выходе элемента 6 устанавливается уровень "1", и счетчик 4 в каждом канале 1-3 пересчитывает свою последовательность импульсов. В процессе счета логический уровень на выходе старшего разряда счетчика 4 одного из каналов 1-3, например канала 1 (фиг.2а), на вход которого поступает опережающая последовательность импульсов, изменяется на противоположный. Однако по принципу большинства логический уровень на выходе элемента 5 сохраняется без изменения (фиг.2б). На выходе элемента 6 опере- 15 жающего канала появляется логический

"0" (фиг,2в), и счет прекращается до тех пор, пока не изменится логический уровень на выходе старшего разряда счетчика 4 другого канала, 20 например канала 2. В этом случае по принципу большинства соответственно: изменяется также логический уровень на выходе элемента 5, и на выходе элемента 6 опережающего канала вновь появляется логическая "1", разрешающая счет.

Одновременно на выходе, например формирователя 9 при изменении логического уровня на его входе с "0 на 30

"1" (фиг.2д) появляется импульс, обеспечивающий установку (сброс) счетчика 4 опережающего и отстающего каналов в состояние, соответствующее состоянию счетчика 4 канала 2, вы-. звавшего переключение на выходе элемента 5.

Таким образом, при смене состояния на выходе элемента 5 дважы в течение цикла пересчета обеспечивается синхронизация устройства па трем каналам. В каждом канале 1-3 сигнал с выхода элемента 5 выдается на соответствующую.шину 13-15 устройства, Частота выходного сигнала соответствует частоте не отстающей и не опережающей входной импульсной последовательности, деленной на 2

Благодаря тому, что устройство синхронизируется по трем каналам 1-3, при каждой смене состояния на выходе элемента 5 сбои и даже полный отказ счетчика 4 одного из каналов 1-3 (фиг ° 2а) не искажают сигнал на выходных шинах устройства (фиг.2б).

Ф о р м у л а и з обретения

Резервированный делитель частоты по авт.св, Р 645282, о т л и ч а юшийся тем, что, с целью повышения надежности работы, в каждый канал введены инвертор, первый и вто.с рой формирователи импульсов, при этом выход мажоритарного элемента через первый формирователь импульсов соединен с входом разрешения записи параллельного кода счетчика импульсов и через соединенные последовательно инвертор и второй формирователь импульсов. — с входом установки в. "О" счетчика импульсов, информационный вход старшего разряда которого соединен с шиной логической единицы, информационные входы остальных разрядов — с шиной логического нуля,