Последовательный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении систем обработки цифровой информации. Цель изобретения - увеличение быстродействия. Последовательный сумматор содержит блок 1 сдвиговых регистров, регистр 2, блок 3 уплотнения, блок 4 распределения синхросигналов, блок 5 формирования значений сумм и переносов очередного среза, блок 6 распределения переносов, блок 7 хранения сумм и переносов. 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (511 4 G 06 F 7/50

В ЕСОЮЗНАЯ галл:",; !,ë ;,::,нская

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H A BTQPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ДО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4246414/24-24 (22) 18.05.87 (46) 15.04.89. Бюл.й- 14 (72) Г.И.Васильев и В.В.Храмов (53) 681.325.5(088,8) (56) Введение в кибернетическую технику/Под ред. Б.Н.Малиновского.

Киев: Наукова думка, 1979, с.126.

Заявка Франции 1! - 2454!36, кл. G 06 Р 7/50, опублик. !979. (54) ПОСЛЕДОВАТЕЛЬНЫЙ СУММАТОР (57) Изобретение относится к вычисли—

ÄÄSUÄÄ 1472900 А1 тельной технике и может быть использовано при построении систем. обработки цифровой информации. Пель изобретения — увеличение быстродействия.

Последовательный сумматор содержит блок 1 сдвиговых регистров, регистр

2, блок 3 уплотнения, блок 4 распре, деления синхросигналов, блок 5 формирования значений сумм и переносов очередного среза, блок 6 распределения переносов, блок 7 хранения сумм и переносов. 5 ил.

1472900

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных систем обработки цифровой информации.

Цель изобретения — увеличение быстродействия.

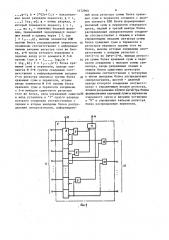

На фиг.1 представлена структурная схема последовательного сумматора; на фиг.2 — функциональная схема блока формирования значений сумм и переносов очередного среза; на фиг.3функциональная схема блока распределения переносов; на фиг.4 — функциональная схема блока хранения сумм и переносов; на фиг.5 — временная диаграмма работы блока распределения синхросигналов..

Последовательный сумматор (фиг.1) 20 содержит блок 1 сдвиговых регистров, регистр 2, блок 3 уплотнения, блок 4 распределения синхросигналов, блок

5 формирования значений сумм и переносов очередного среза, блок 6 рас- 25 пределения переносов, блок 7 хранения сумм и переносов.

Блок 5 формирования значений сумм и переносов очередного среза (фиг.2) содержит регистр 8, первую и вторую щ группы элементов И 9, 10, элемент

ИЛИ 11, информационные входы 12 регистра, вход 13 разрешения записи регистра, выход 14 суммы, выходы 15 переноса. Блок 6 распределения переносов (фиг.3) содержит регистр 16, группу элементов ИЛИ 17, входы

18 элементов ИЛИ, выходы 19 регистра, вход 20 установки в "0" регистра, вход 21 управления записью, 40

Блок 7 хранения сумм и переносов (фиг ° 4) содержит сдвиговый регистр

22, регистр 23 суммы, группу регистров 24 переноса, и-1 групп элементов

И 25». . 25 „,, где n — разрядность 45 операндов, входы 26 записи переносов, вход 27 управления сдвигом сдвигового регистра, вход 28 установки в "1" одного разряда, вход 29 управления, вход 30 записи суммы, выходы 31 суммы,50 выходы 32 переноса.

Принцип действия устройства основан на формировании и использовании двух признаков: признака нечетности количества единиц в разрядном срезе

55 и признака границы между "0" и "1" в упорядоченной их последовательности. Упорядочение состоит в том, что вначале подряд размещаются все единицы разрядного среза, а затем оставшиеся нули, Признак границы в таком векторе позволяет сразу же установить нужные значения переносов и распределить их по принципу "сразу на свое место", т.е. в отличие от традиционной схемы распространения переносов, при которой перенос распространяется вначале на соседний старший разряд, затем на более старший и т.д., здесь переносы распределяются минуя часть соседних старших разрядов сразу же в те позиции, которые задаются признаком границы у между "0" и "1" в упорядоченном разрядном срезе. Этот признак однозначно определяется количеством "1" в разрядном срезе.

Устройство работает следующим образом.

Массив слагаемых з апи сыв ае т ся в блок 1, который может обеспечивать считывание одноименных разрядов всех слагаемых, начиная с младшего, По сигналу считывания m-разрядное содержимое младших разрядов всех m, слагаемых заносится в первые m разрядов регистра 2, предназначенного для хранения значений разрядов, подлежащих суммированию, часть входов регистра 2 используется для занесения значений переносов, попавших в данный разряд при обработке последующих разрядных срезов. Регистр 2 обнуляется каждый раз перед занесением очередного разрядного среза.

Содержимое регистра 2 подается в блок 3, где происходит перестановка

"0" и "1" поступившего двоичного кода так, что вначале подряд располагают все r единиц поступившего кода, а затем все m+K — r нулей этого кода.

Затем код с выходов блока 3 подается

I через входы 12 на регистр 8 блока 5.

Если число единиц нечетное, то с помрщью группы элементов И 9 и элемента ИЛИ 11 на выходе 14 блока 5 формируется единичный сигнал суммы S в противном случае — нулевой сигнал ($, .= 0).

Си гн алы пе рено с а формируются с помощью группы элементов И 10 на выходах 15 таким образом, что в еди" ничном состоянии оказывается тот выход 15, который находится ближе всех к границе между нулями и единицами. во входном коде со смещением в сторону единиц. Например, если число

14729 единиц во входном коде равно пяти, то возбуждается только второй сверху выход 15. Сброс регистра 8 осуществляется через вход 13 синхросигналом иэ блока 4. Сигнал переноса, сформированный на одном из выходов 15 блока 5, поступает на соответствующий вход 18 блока 6, в котором с помощью группы элементов ИЛИ 17 происходит 10 распределение сигнала переноса в соответствующие разряды регистра 16.

Сброс регистра в "0" осушествляется по входу 20, а управление записью в регистр — по входу 21 соответствующими15 синхросигналами из блока 4. Сигналы переноса с выходов 19 блока 6 поступают на соответствукщие входы 26 блока 7, Запись поступивших значений переноса в один из регистров 24 20 переноса группы производится по единичному разрешающему сигналу одного иэ разрядов сдвигового регистра 22, содержащего одну "1", через группы элементов И 25. Сдвиг регистра 22 25 производится по синхросигналу на вхо де 27, для регистра 22 используется вход 28. Сдвиг регистров 24 переноса и регистра 23 суммы вправо производится по синхросигналам на входе 29. 30 регистр 23 суммы используется для записи и хранения значений сумм, формируемых в блоке 5, Сигнал суммы S подается в регистр 23 суммы через вход 30,- а сформированное после обработки всех разрядных срезов значение суммы подается на выход сумматора через выходы 31. Значения сигналов переноса, сформированные при обработке очередного среза и записанные в - 40 соответствующий регистр 24 переноса, подаются для последующей обработки совместно со значениями разрядного среза на входы регистра 2 с выходов

32 блока 7.

Формул а изобретения

Последовательный сумматор, содер.— жащий и-разрядный блок сдвиговых регистров (n — разрядность операндов), регистр, отличающийся тем, что, с целью увеличения быстродействия, регистр имеет разрядность

m+n-1 (m — количество операндов), в сумматор введены блок уплотнения, блок формирования значений сумм и переносов очередного среза, блок распределения переносов, блок хранения сумм и переносов, блок распределения синхросигналов; блок формиро(где

r =О, 00

4 вания значений сумм и переносов очередного среза содержит регистр, первую и вторую группы элементов И по

0,5 (m + Iog < m) элементов И каждая, элемент ИЛИ; блок распределения переносов содержит регистр, группу эле- ментов ИЛИ; блок хранения сумм и переносов содержит сдвиговый регистр, регистр суммы, группу из п-1 регистров переноса, и-1 групп элементов И по log (m + log m) элементов И в каждой, причем m выходов блока сдвиговых регистров соединены соответственно с m входами регистра сумматора, выходы которого соединены с соответствующими информационными входами блока уплотнения, выходы которого соединены с соответствующими информационными входами регистра блока формирования значений сумм и переносов очередного среза, все нечетные прямые выходы которого соединены с первыми входами первой группы элементов

И блока формирования значений сумм и переносов очередного среза, выходы которых соединены соответственно с входами элемента ИЛИ блока формирования значений сумм и переносов очередного среза, вторые входы первой группы элементов И блока формирования значений сумм и переносов очередного среза подключены соответственно к инверсным четным выходам регистра блока формирования значений сумм и пере носов очередного среза, первые входы второй группы элементов И блока формирования значений сумм и переносов очередного среза соединены соответственно с прямыми четными, а вторые их входы — с соседними старшими инверсными четными выходами регистра блока формирования значений сумм и переносов очередного среза, выход элемента

ИЛИ блока формирования значений сумм и переносов очередного среза подключен к информационному входу сдвигово-. го регистра блока хранения сумм и переносов, выход j-го элемента И второй группы блока формирования значений сумм и переносов очередного среза (где j = 1,. ° °,38/2 Г; 3 S/2(=

0>5(log >m + m); S — число единиц в вертикальном срезе) подключен к одному из входов Р; -х элементов

ИЛИ блока распределения переносов

1472

5 ...,q-1; k = 2 (2г+1); r - максимальное число разрядов переноса; q = 1, ...,) log< m(; q — номер разряда, в который помещается перенос; i = 1, ш; х — значение булевой функции, принимающей чередующиеся значения нулей и единиц через 2 ", где

) 1,...,ц), выходы элементов ИЛИ группы блока распределения переносов 10 соединены соответственно с информационными входами регистра того же бло". ка, р-й выход которого подключен к первому входу р-го элемента И f-й группы (где р 1, ° ., log<(m + 15

+ log ш); f 1,...,n-1) блока хранения сумм и переносов, выходы элементов И f"é группы соединены соответственно с информационными входами

f-ro регистра переноса группы блока 20 хранения сумм и переносов, вторые входы элементов И f-й группы блока хранения сумм и переносов соединены с f-м выходом сдвигового регистра того же блока, вход управления сдвигом25 и вход установки в "1" одного разряда которого соединены соответственно с первым и вторым выходами блока распределения.синхросигналов, информацион900 6 ный вход регистра суммы блока хранения сумм и переносов соединен с выходом элемента ИЛИ блока формирования значений сумм и переносов очередного среза, первый и третий выходы блока распределения синхросигналов соедине. ны соответственно с первым и вторым управляющими входами регистра суммы блока хранения сумм и переносов и регистров переноса группы того же блока, выходы которых соединены соот-. ветственно с входами регистра с (m+1)-ro по (m+n-1)-й, выходы регист= ра суммы блока хранения сумм и переносов соединены с выходом суммы сумматора,.входы разрешения чтения и записи блока сдвиговых регистров соединены соответственно с четвертым и пятым выходами блока распределения синхросигналов, шестой - девятый выходы которого соединены соответст" венно с управляющим входом регистра, входом разрешения записи регистра блошка формирования значений сумм и переносов очередного срез а и входами установки в "0" и управления записью регистра блока распределения переносов.

Фиг. 2

1472900

1472900 фас Риес амки4

cjtr. P k

rjIþäó,жег фЬма В и 5

08». м

Ам

+br. Ю

А.6

Составитель А. Клюев

Техред М.Дидык

Корректор И.Муска

Редактор И.Рыбченко

Заказ 1712/48

Тираж бб7

1Ioд пи сно е

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, R-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101