Устройство для вычисления корреляционной функции

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в гидроакустике, радиолокации, при спектральном и корреляционном анализе сигналов, представленных в цифровой форме. Цель изобретения - повышение помехоустойчивостидостигается введением в устройство счетчика 12,четырех блоков оперативной памяти 13, 17, 19 и 23, двух блоков вычитания 14 и 20, четырех блоков умножения 15, 18, 21 и 24, двух сумматоров 16 и 22 и блока памяти 25, отображающих входные сигналы в логарифмический масштаб времени. Результат вычислений инвариантен к доплеровской дисперсии, за счет чего выигрыш в помехоустойчивости прямо пропорционален величине базы обрабатываемых сигналов. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1 у 4 G 06 F 15/336

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО- ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР! (61) 135250 1 (21) 4236419/24-24 (22) 27. 04, 87 (46) 15.04. 89. Вюл. М -14 (72) В. А. Сапрыкин, Е. Н. Одинцов, Ю.В. Городничев и О.А.Артамонов (53) 681. 3 (088. 8) (56) Авторское свидетельство СССР

Ф 1352501, кл. С 06 F 15/336 1986. (54) )УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано в гидроакустике, радиолокации, при спектральном и корреляционном аналйзе сигналов, представ„„Я0„„1472916 А 2 ленных в цифровой форме. Цель изобретения — повьппение помехоустойчивости - достигается введением в устройство счетчика 12, четырех блоков оперативной памяти 13, 17, 19 и 23, двух блоков вычитания 14 и 20, четырех блоков умножения 15,, 18, 21 и 24, двух сумматоров 16 и 22 и блока памяти 25, отображающих входные сигналы в логарифмический масштаб времени. Результат вычислений инвариантен к допплеровской дисперсии, за счет чего выигрыш в помехоустойчивости прямо пропорционален величине базы обрабатываемых сигнапов.

2 ил.

1472

Изобретение относится к вычислительной технике и может быть использовано в гидроакустике, радиолокации, при спектральном и корреляционном анализе сигналов, представленных в цифровой форме.

Цель изобретения — повышение помехо у стой чи во ст и.

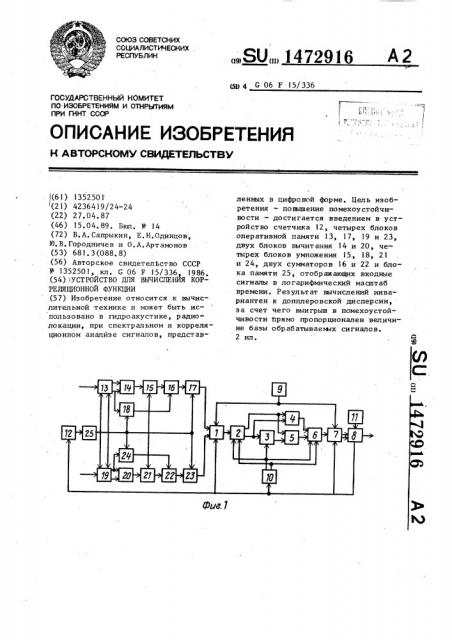

На фиг. 1 изображена структурная 10 схема устройства для вычиспения корреляционной функции, на фиг. 2 схема блока формирования выходного массива.

Устройство (фиг. 1) содержит 15 первый блок 1 дискретного преобразования Фурье, блок 2 разделения спектров, согласованный фильтр 3, первый

4 и второй 5 блоки комплексного перемножения спектров, блок 6 смешива-. 20 ния спектров, второй блок 7 дискретного преобразования Фурье, блок,8 формирования выходного массива, блок

9 памяти коэффициентов, блок 10 управления согласованной фильтрацией, генератор 11 тактовых импульсов, счетчик 12, перый блок 13 оперативной памяти, первый блок 14 вычитания, третий блок 15 умножения, первый сумматор 16, третий блок 17 оператив-30 ной памяти, первый блок 18 умножения, второй блок 19 оперативной памяти, второй блок 20 вычитания, четвертый блок 21 умножения, второй сумматор

22, четвертый блок 23 оперативной памяти, второй блок 24 умножения и блок 25 памяти. . Блок формирования выходного массива (фиг. 2) содержит счетчик 26, элемент НЕ 27, первый 28 и второй 40

29 сумматоры, элемент И 30 и блок 31. памяти.

Устройство работает следующим образом.

Обработка сигналов начинается с цикла записи последовательностей отсчетов сигналов X(n) и Y(n) в блоки

13 и 19 оперативной памяти. Отсчеты поступают на входы блоков 13 и 19, на управляющие входы которых с блока

25 памяти подаются сигналы, опреде" ляющие режим записи адресов, по которым запйсываются отсчеты. По окончании цикла записи начинается режим считывания при этом блоки 17 и 23

Ф

55 работают в режиме записи. Считывание из блоков 13 и !9 ведется rio двум адресам сразу из каждого. По первому адресу считываются значения X(t„(n ) ) 916 2 и Y(t„.(п ) ), которые с первых выходов блоков 13 и 19 поступают на входы уменьшаемого первого и второго блоков 14 и 20 вычитания, по второму адреcy — значения Х(е (и )) и Y(t <(n )) которые с вторых выходов блоков 13 и

19 поступают на входы вычитаемого первого и второго блоков 14 и 20 вычитания. С выходов последних снимаются значения разностей X(t„(n ) )Х(р(п))иY(t))(n))Y(tр(п))е торые поступают на первые входы соот" ветственно третьего !5 и четвертого

21 блоков умножения. В это же время на первых входах первого 18 и второго

24 блоков умножения удерживаются знаеенж X(t (n )) и Y(t t(n )), где п =1, N -1 — номер отсчета отображенI ной последовательности; N — колйчество отсчетов в отображении, ))

t (и }=(N-1) )", N - количество отсчетов в выборке. На вторые входы бло-:. ков 18 и 24 подается код коэффициента

К (n ), а на вторые входы блоков 15 и 21 — код коэффициента N(n ). С выходов третьего 18 и четвертого 24 блоков умножения снимаются значения произ ведений К (и ) 5 X (t () (n ) )Х(Ср(п ))1 и К (и )(7(й (и ))

-Y(tp(n ))3, а с выходов первого 15 и второго 21 блоков умножений — значения произведений N(n ) Х(1 (и }) и

N(n ) Y(t (и )), которые поступают на первые и вторые входы первого 16 и второго 22 сумматоров, с выходов которых снимаются значения.

X (n ) К (n )(X(t„(n )) X(tp(n )))+

+N(n )X(tр(п ))

Y (и ) К (n )(7 (Йр (и ) ) 7 (1р (и ) )) +

+N(n )Y(t (n )), где К(п ) — дробная часть значения ()

t „(n ) =А+ 1; t <(n ) =А;

А - целая часть значения

t (n ); N(n ) =1/ t(n ) .

Значения К(п ), И(п ) t))(n ) .р(п ) заносятся в соответствующие разряды блока 25 памяти. Вычисленные значения Х (n ) и Y (п ) записываются в блоки 17 и 23 по соответствующим адресам. Время удерживания адресов и операндов на выходе блока

25 должно быть достаточным для срабатывания блоков 14, 20; 15, 21;

18, 24; 16, 22 и записи без искажения

Составитель Е. Куртин

Редактор А. Лежнина Техред М.Дидык Корр ектор М. Самбор ская

Заказ 1712/48, Тираж бб7 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r.Óæãoðoä, ул. Гагарина, 101 ти соединен с адресными входами пер- вого и второго блоков оперативной памяти, первые выходы которых подключены к входам уменьшаемого соответственно первого и второго блоков вычитания, входы вычит аемо ro которых соединены с вторыми выходами соответственно первого и второго блоков оперативной памяти и первыми входами соответственно первого и второго блоков умножения, вторые входы которых соединены с третьим выходом с блока памяти, четвертый выход которого подключен к первым входам третьего и четвертого, блоков умножения, вторые входы которых соединены с выходами соответственно первого и вто. рого блоков вычитания, выходы тре72916 6 тьего и четвертого блоков умножения соединены с первыми входами соответственно первого и второго сумма5 торов вторые входы которых подключеФ ны к выходам соответственно первого и второго блоков умножения, выходы первого и второго сумматоров соединены с информационными входами соответственно третьего и четвертого блоков оперативной памяти, входы

"Запись — считывание" которых подключены к пятому выходу блока памяти, выходы третьего и ч етв ертог о блоков оперативной памяти подключены соответственно к пер вому и второму входам первого блока дискретного преобразователя Фурье °