Устройство для коррекции двухградационных изображений при воздействии шумов

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано для коррекции двухградационных изображений. Цель изобретения, заключающаяся в упрощении устройства и повышении его быстродействия, достигается введением блока коррекции строчных шумов, семи блоков памяти, двух элементов И и двух элементов ИЛИ-НЕ, что позволяет осуществлять устранение на изображении шумов, состоящих из 2<SP POS="POST">.</SP>N и N<SP POS="POST">.</SP>2 элементов изображения. 2 з.п.ф-лы, 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 С 06 К 9/00 и - EÛIÇÌ0

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 4247505/24-24 (22) 13,03,87 (46) 15,04.89. Бюл. № 14 (71) Научно-исследовательский институт проблем машиностроения при МВТУ им. Н.Э.Баумана (72) M.È.Алекберов (53) 681.-327.12(088.8) (56) Патент США № 3737855, кл. 340-146.3, опублик, 1973.

Авторское свидетельство СССР

¹ 708371, кл. G 06 К 9/00, 1977.

Изобретение относится к вычислительной технике и может быть применено для коррекции двухградационных изображений.

Цель изобретения — упрощение устройства и повышение быстродействия.

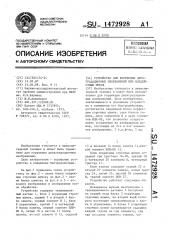

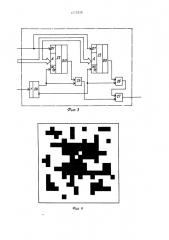

На фиг. 1 приведена схема устройства; на фиг.2 — схема блока коррекции строчных шумов; на фиг.3 — схема блока памяти; на фиг.4 и 5 — исходное изображение и изображение после обработки.

Устройство содержит телевизионный датчик 1, блок 2 коррекции строчных шумов, первый 3 и второй 4 блоки памяти, первый элемент И 5, блок 6 управления, третий 7 и четвертый

8 блоки памяти, первый элемент ИЛИНЕ 9, пятый 10 и шестой 11 блоки памяти, второй элемент И 12, сецьмой

Я0,» 1472928 А 1 (54) УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ДВУХ-ГРАДАЦИОННЫХ ИЗОБРАЖЕНИЙ ПРИ ВОЗДЕЙСТВИИ ШУМОВ (57) Изобретение относится к вычислительной технике и может быть использовано для коррекции двухградационных изображений. Цель изобретения, заключающаяся в упрощении устройства и повышении его быстродействия, достигается введением блока коррекции строчных шумов, семи блоков памяти, двух элементов И и двух -.ë-.åìåíтов ИЛИ -НЕ, что позволяет осуществлять устранение на изображении шумов, состоящих из 2 п и п 2 элементов изображения. 2 з.п.ф-лы, 5 ил.

13 и восьмой 14 блоки памяти 14,второй элемент ИЛИ-НЕ 15.

Блок коррекции строчных шумов содержит три триггера 16-18, третий 19 и четвертый 20 элементы И, четвертый триггер 21. 3

Блок памяти содержит первый 22 и Ю второй 23 элементы памяти, пятый триг- Я ) гер 24, пятый 25, шестой 26 элементы }

И, третий элемент ИЛИ 27. Q0

Устройство работает следующим, образом.

Искаженное шумами изображение с телевизионного датчика 1 поступает

3 » на первый вход блока 2 коррекции строчных шумов, на второй вход которого поступают синхроимпульсы с блока 6 управления. В блоке 2 коррекции строчных шумов производится задержка каждой строки на три элемента, где три соседчих элемента строки, за1472928 писанные на П-триггерах 16, 17 и 18, сравниваются на элементах И 19 и 20.

При появлении на строке трех соседних единиц (111) на выходе элемента

И 19 появляется сигнал "1", переключает четвертый триггер 21 (RS-триггер) в состояние "1", RS-триггер сохраняет свое состояние до тех пор, пока на R âõîä не поступает сигнал

"1" с выхода четвертого элемента И

20, который говорит о том, что на строке появились три соседних нуля (000). Далее RS-триггер 21 сохраняет состояние "0" до тех пор, пока не по- 15 явятся на строке три соседние единицы (111) и так далее (фиг.2). Таким образом, происходит корректировка строк от строчных шумов типа "1", "11", "0", "00", Далее откорректиро- 20 ванная строка поступает на вход первого блока 3 памяти. В зависимости от состояния пятого триггера 24 (Ттриггер) определяется элемент памяти, куда записывается текущая строка. 25

Например, если пятый триггер 24 находится в состоянии "0", то запись производится в элемент 22 памяти, а с элемента памяти 23 считывается предыдущая строка. С поступлением каждо- 30 го элемента строки в адресные шины элементов 22 и 23 памяти поступает соответствующий адрес с блока 6 управления. Таким образом, строка, корректированная от строчных шумов, запоминается в блоке 3 памяти. 9 поступлением следующей строки строка, записанная в блоке памяти 3, перезаписывается в блок 4 памяти и параллельно в блоке 3 памяти запоминается те- 40 кущая строка и так далее. Две предыдущие строки и текущая строка одновременно с выходов блоков 3 и 4 памяти и блока 2 коррекции строчных шумов поэлементно поступают на вход 45 первого элемента И 5, информация с выхода первого элемента И 5 запоминается в блоке 7 памяти. С поступлением следующей строки информация с выхода блока 7 памяти запоминается в блоке 8 памяти и так далее. Информация с выходов блоков 7 и 8 памяти и с выхода первого элемента И 5 поступает на вход первого элемента ИЛИ-HE

9. На выходе первого элемента ИЛИ-НЕ

9 появляется "0" только тогда, когда среди сравниваемых элементов столбца есть хотя бы три соседние единицы (111) . Таким образом, на выходе первого элемента ИЛИ-НЕ 9 формируется инверсное и корректированное от шумов типа "1" и "1/1" изображение.

Чтобы корректировать изображение от шумов типа "0" и "О/О" процесс корректировки иэображения от шумов типа "1" и "1/1" повторяется на инвертированным изображении на блоках 10, 11, 13 и 14 памяти и на элементах

И 12 и ИЛИ-НЕ 15. На выходе второго элемента ИЛИ-НЕ 15 получается изображение (фиг.5), корректированное от шумов.

Формула изобретения

1. Устройство для коррекции двухградационных изображений при воздействии шумов, содержащее телевизионный датчик, первый блок памяти и блок управления, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства и повышения быстродействия, оно содержит блок коррекции строчных шумов, семь блоков памяти, два элемента И и два элемента И и два элемента ИЛИ-НЕ, выход телевизионного датчика соединен с информационным входом блока коррекции строчных шумов, выход строчных гасящих импульсов телевизионного датчика соединен с входом строчной синхронизации блока управления, вход синхронизации блока коррекции строчных шумов соединен с первым выходом блока управления, а выход соединен с информационным входом первого блока памяти и первым входом первого элемента И, адресные входы блоков памяти соединены с третьим выходом блока управления, входы записи блоков памяти— с вторым выходом блока управления, выход первого блока памяти — с информационным входом второго блока памяти и с вторым входом первого элемента И, выход второго блока памяти— с третьим входом первого элемента И, выход первого элемента И вЂ” с информационным входом третьего блока памяти и первым входом первого элемента

ИЛИ-НЕ, выход третьего блока памяти— с информационным входом четвертого блока памяти и вторым входом первого элемента ИЛИ-НЕ, выход четвертого блока памяти — с третьим входом первого элемента ИЛИ-НЕ, выход второго элемента ИЛИ-HE — с информационным входом пятого блока памяти и первым

5 14729 входом второго элемента И, выход пятого блока памяти — с информационным входом шестого блока памяти и с вторым входом второго элемента И, выход

5 шестого блока памяти — с третьим выФ ходом второго элемента И, выход второго элемента И вЂ” с информационным входом седьмого блока памяти и первым входом второго элемента ИЛИ-НЕ, выход седьмого блока памяти — с информационным входом восьмого блока памяти и вторым входом второго элемента ИЛИ-НЕ, выход восьмого блока памяти — с третьим входом второго эле-)5 мента ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ является выходом устройства.

2. YCTpOHCTBO IIG II ° 1, ч а ю щ е е с я тем, что блок коррекции строчных шумов содержит четыре триггера и два элемента И, вход данных первого триггера является ин-. формационным входом блока, входы стробирования первого, второго и третьего триггеров являются входом синхро- 25 низации блока, прямой выход первого триггера соединен с входом данных второго триггера и с первым входом третьего элемента И, прямой выход второго триггера соедйнен с входом 30 данных третьего триггера и с вторым входом третьего элемента И, третий вход которого соединен с прямым выходом третьего триггера, инверсные выходы первого, второго и третьего триггеров соединены с входами четвертого элемента И, выходы третьего и четвертого элементов И соединены с установочным входом и входом сброса четвертого триггера, выход которого является выходом блока.

3. Устройство по п.1, о т л .и ч аю щ е е с я тем, что блок памяти содержит два элемента памяти, пятый и шестой элементы И, третий элемент

ИЛИ и пятый триггер, входы данных первого и второго элементов памяти являются информационным входом блока, адресные входы первого и второго элементов памяти являются адресным входом блока, прямой выход пятого триггера соединен с входом запись первого элемента памяти и первым входом пятого элемента И, выход первого элемента памяти — с вторым входом пятого элемента И, инверсный выход пятого триггера — с входом запись второго элемента памяти и первым входом шестого элемента И, выход второго

1 элемента памяти — с вторым входом шестого элемента И, выход пятого элемента И вЂ” с первым входом третьего элемента ИЛИ, выход шестого элемента И вЂ” с вторым входом третьего элемента ИЛИ, выход которого является выходом блока, вход пятого триггера является входом записи блока.! 472928

1472928

Составитель А.Глотов

Редактор Н,Киштулинец Техред Л.Олийнык Корректор С.Шекмар

Заказ 1713/49 Тираж 667 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101