Ассоциативная запоминающая ячейка

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в ассоциативных процессорах для создания баз знаний. Цель изобретения - повышение быстродействия и расширение функциональных возможностей ячейки за счет обеспечения записи и считывания признака принадлежности информации объекту. Ячейка с управляющими входами 1-6, информационными выходами 7 и входом 8 содержат элемент И-ИЛИ 9, триггеры 10,14, элементы И 11-13,16,18,элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 17, элемент НЕ 15. 3 ил.

1

„„SU„„, 1474740

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 51) 4 С 11 С 15/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOIVlV СВИДЕТЕЛЬСТВУ

2

43

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР.(21) 4240090/24-24 (22) 04.03.87 (46) 23.04.89. Бюл. ¹- 15 (71) Институт кибернетики им. В. M. Глушкова (72) В. А. Ященко и С. О. Чепига (53) 681.327(088.8) . (56) Авторское свидетельство СССР

¹ 634372, кл. G ll С 15/00, 1978.

Авторское свидетельство СССР

¹ 1127007, кл. G 11 С 15/00, 1983. (54) АССОЦИАТИВНАЯ ЗАПОИИНА10ЩАЯ ЯЧЕЙ КА (57) Изобретение относится к вычислительной технике и может быть использовано в ассоциативных процессорах для создания баз знаний. Цель изобретения — повышение быстродействия и расширение функциональных возможностей ячейки за счет обеспечения записи и считывания признака принадлежности информации обьекту. Ячейка с управляющими входами 1-6, информационными выходами 7 и входом 8 содержит элемент И-ИЛИ 9, триггеры 10, 14, элементы И 11-13, 16, 18, элементы

ИСКЛЮЧАЮЩЕЕ ИЛИ 17, элемент НЕ 15 °

3 ил.

1474740

Изобретение относится к вычислительной технике и может быть использовано в ассоциативных процессорах для создания баз знаний.

Цель изобретения = повышение быстродействия и расширение функцио-: нальных возможностей ячейки за счет обеспечения записи и считывания признака принадлежности информации объ- 10 екту.

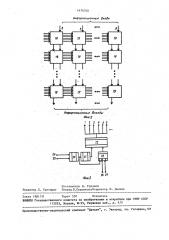

На фиг. 1 изображена структурная схема ассоциативной запоминающей ячейки; на фиг. 2 — структурная схема матрицы, составленной из этих яче- 15 ек, на фиг. 3 — структурная схема блока. управленйя.

Ассоциативная запоминающая ячейка (фиг. I) содержит первый вход 1 .разрешения чтения бита информации, первый вход 2 разрешения чтения конъюнкции битов информации, второй вход 3 разрешения чтения бита информации, второй вход 4 разрешения чтения коньюнкции битов информации, первый 5 и второй 6 входы разрешения записи инФормации, информационные выход 7 и вход 8, элемент И-ИЛИ 9, третий триггер 10, первый 11, второй 12 и третий 13 элементы И, первый 14» и второй 14 триггеры, элемент НЕ 15, четвертый элемент И 16, первый 17 и второй 17 элементы ИСКЛЮЧАЮЩЕЕ HJIH пятый элемент И 18. Сигналы, .необхо.димые для работы ячейки 19 и матрицы, 35 собранной из данных ячеек (фиг. 2), вырабатываются .блоком управления, содержащим (фиг. 3) элемент И 20, счетчик 21, блок 22 перепрограммируемой памяти микрокоманд, счетчик 23 и вхо- 40 ды 24-27.

При формировании из ассоциативных запоминающих ячеек 19 матрицы размером m х и, где m — количество строк, а n — количество столбцов, входы 1-6 разрешения каждой ячейки соединяются с разрешающими входами соседней справа ячейки, а выход 7 и вход 8 — с соот-гветствующими выходом и входом соседней снизу ячейки.

Индентификаторы (фиг. 1) расшифровываются следующим образом: (1 — информационный выход; D — информационный вход1 — Разрешающии вход установки в единицу, R — вход установки в нуль.

Ячейка 19 в матрице реализует следующие логические функции.

Запись битов

А ° и A( (2) (3) К =А(,ЛА (4) К = A< ° ., Л А,„° Л A(1 (5) где j = 1, 2, З,...,m1;

i = 1, 2, З,...,п, и чтение битов А ; и Функций по формулам (2), (4) и (5).

Выполнение этих функций может выполняться одновременно во всех ячейках 19, что увеличивает быстродействие матрицы.

Матрица, составленная из ячеек 19, . работает следующим образом.

На входы 8 подаются признаки вводимых в матрицу объектов. По управляющим сигналам, поступающим на входы

5 и 6 разрешения записи, осуществляется запись информации об объектах в матрицу. В каждой строке матрицы выполняются функции по формулам (2)— (5). Если в К число установленных разрядов 2, а А,„ . ф К и А<,, 4 К, то осуществляется перезапись К в соседнюю снизу строку ячеек.

Если в К число установленных разрядов 2, то выполняется запись в матрицу информации о новом объекте.

Таким образом, в матрице формируется структура данных, обеспечивающая запоминание и динамическую перестрой1 t ку ассоциативных связей между отдельными объектами, характеризующимися сочетаниями признаков, которые удовлетворяют некоторому критерию, учитывающему принадлежность сочетания нескольким объектам.

Чтение информации из матрицы осуществляется по управляющим сигнала, подаваемым на входы 1-4 разрешения считывания данных. Опишем более под-. робно работу ассоциативной запоминающей ячейки и блока управления.

При поступлении единичного сигна- ла на вход 6 и бита информации на вход 8 происходит установка тригrepa

14 в соответствии с битом информации, поступающим на вход 8.

14747и0

Формула изо бре те ния

Ассоциативная запоминающая ячейка, содержащая первый и второй триггеры, с первого по четвертый элементы И, элемент И-ИЛИ и элемент НЕ, причем выход первого триггера подключен к

При поступлении единичного сигнала на вход 5 и бита информации ня вход

8 происходит установка триггера 14 в соответствии с сигналом «а входе 8.

С выхода триггеров 14„ и 14 сигналы поступают на первый и второй входы элемента И 13, с выхода которого сигнал, соответствующий конъюнкции битов информации, хранящихся в триггерах

14 „и 14, устанавливает триггер 10.

При поступпении единичного сигнала на вход 3 бит информации с выхода триггера 10 через элемент И-ИЛИ 9 поступает на выход 7. Кроме того, ин- 15 вертированный сигнал с инверсного выхода триггера 10 поступает на вторые входы элементов И 11 и 12, а на первые входы этих элементов поступают сигналы с выходов триггеров 143 и 20

14 . По разрешающему сигналу на вхо— де 4 сигнал, соответствующий конъюнкции битов информации, через элемент

И-ИЛИ 9 поступает на выход 7. При поступлении единичного (разрешающего) 25 сигнала на вход 2 сигнал, соответствующий конъюнкции битов информации, через элемент И-ИЛИ 9 с выхода элемента И 12 поступает на выход 7. По разрешающему сигналу на входе l сиг- 30 нал с выхода триггера 14 поступает на выход 7 через элемент И-ИЛИ 9, Управляющие сигналы 1-6 вырабатываются в блоке управления (фиг. 3).

На вход 26 счетчика 23 подается сигнал, разрешающий запись начального адреса микропрограммы минус единица по входу 27. На вход 24 пода. ется сигнал, разрешающий прохождение тактового сигнала по входу 25 на счетный 40 вход счетчика 23 и через счетчик 21 на вход чтения блока 22, с выхода счетчика 23 на вход адреса блока 22 подается адрес микрокоманды, которая считывается на выход блока 22 при 45 наличии сигнала на вход чтения.

Счетчик 21 служит для обеспечения устойчивой работы блока управления, т.е. для согласования сигналов чтения

1 и адреса на входе блока 22. 50 первым входам первого и третьего эл»ментов И и первому информационному входу элемента И-ИЛИ, выход которого является информационным выходом ячейки, выход второго триггера соединен с первым входом второго элемента И, отличающаяся тем, что, с целью повышения быстродействия и расширения функциональных возможностей ячейки за счет обеспечения записи и считывания признака принадлежности информации объекту, в нее введены третий триггер, пятый элемент И и первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выхоцы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединены соответственно с входами .установки в 0" первого и второго триггеров, выход второго триггера подключен к второму входу третъего элемента И, выход которого соединен с входом установки в "1" третьего триггера и . входом элемента НЕ, выход которого подключен к входу установки в "0" третьего триггера, прямой выход которого соединен с вторым информационным входом элемента И-ИЛИ, инверсный выход третьего триггера соединен с вторыми входами первого и второго элемен. тов И, выходы которых подключены соответственно к третьему и четвертому информационным входам элемен та ИИЛИ, выходы четвертого и пятого элементов И соединены соответственно с входами установки в "1" первого и второго триг г еров, инфо рмационные входы четвертого и пятого элементов

И и первого и второго элементов ИСКЖОЧАЮЩЕЕ ИЛИ объединены и являются информационным входом ячейки, разрешающие входы первого элемента ИСКЛОЧАЮЩЕЕ ИЛИ и четвертого элемента И объединены и являются первым входом разрешения записи ячейки, разрешающие входы второго элемента ИСКЛЮЧАК61ЕЕ

ИЛИ и пятого элемента И объединены и являются вторым входом разрешения записи ячейки, с первого по четвертый разрешающие входы элемента И-ИЛИ являются соответственно первым вхоцом разрешения чтения битя информации, первым входом разрешения чтения коньюнкции битов информации, вторым входом разрешения чтения битя информации и вторым входом разрешения чтения конъюнкции битов пнформлцпи ячейки.

Имрормоциониые drt opbi

44 °

° 4 °

9

499 б

Инрориационные выходы сь.г

26 27

Составитель В. Рудаков

Редактор Л. Гратилло Техред Л. Сердюкова Корректор Y.. Демчик

Заказ 1991/51 Тираж 558 . Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина,101