Дельта-модулятор

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и технике связи. Его использование в системах передачи сигналов позволяет повысить точность преобразования за счет расширения динамического диапазона преобразуемых сигналов. Дельта-модулятор содержит компаратор 1, формирователь 4 информационной импульсной последовательности, интегратор 5, блок 9 выделения пачек символов и блок 10 расширения пачек символов. Благодаря введению компараторов 2,3, интеграторов 6,7, амплитудно-импульсного модулятора 8, мультиплексора 11, блока 12 коммутации и источника 13 пороговых уровней в дельта-модуляторе обеспечивается компрессия по пачкам одинаковых символов,число которых меняется при изменении уровня входного сигнала. 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

А1

„„SU„„147485 (51)4 H 03 M 3/02

;г:

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4240321/24-24 (22) 05.05.87 (46) 23.04.89. Бюп. М- 15 (71) Ленинградский электротехнический институт связи им. проф.M.À.Áîí÷-Бруевича (72) А.В.Бухинник, Б.Е.Трофимов и П.E.Ùåðáàòûé (53) 621.376 .56(088.8) (56) Авторское свидетельство СССР

У 349080, кл. Н 03 M 3/02, 1970.

Электросвязь, 1979, Р 11, с. 38-40, рис ° 1.

Авторское свидетельство СССР

Р 1129732, кл. Н 03 M 3/02, 1983. (54) ДЕЛЬТА-МОДУЛЯТОР (57) Изобретение относится к автоматике и технике связи. Его использование в системах передачи сигналов позволяет повысить точность преобразования за счет расширения динамического диапазона преобразуемых сигналов. Дельта-модулятор содержит компаратор 1, форьырователь 4 информационной импульсной последовательности, интегратор 5, блок 9 выделения пачек символов и блок 10 расширения пачек символов. Благодаря введению компараторов 2 и 3, интеграторов 6 и 7, амплитудно-импульсного модулятора 8, мультиплексора 11, блока 12 коммутации и источника 13 пороговых уровней в дельта-модуляторе обеспечивается компрессия IID пачкам одинаковых сим- а волов, число которых меняется при изменении уровня входного сигнала.

2 ил.

14 74850

Изобретение относится к автоматике и технике связи и может быть использовано в системах передачи сигналов.

Цель изобретения — повышение точ5 ности преобразования за счет расширения динамического диапазона преобразуемых сигналов.

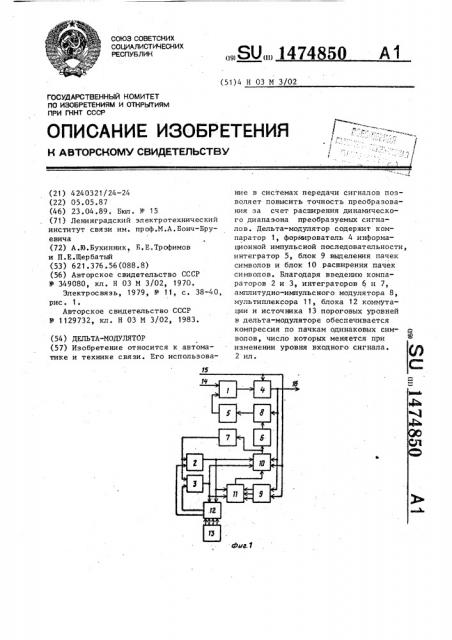

На фиг. 1 показана блок-схема дельта-модулятора; на фиг. 2 — гра- 10 фик зависимости соотношения сигнал/шум (с/ш) для разных видов дельта-модуля ции .

Дельта-модулятор содержит первый— третий компараторы 1-3, формирователь 4 информационной импульсной последовательности (ФИИП), первыйтретий интеграторы 5-7, амплитудноимпульсньпЪ модулятор (АИМ) 8, блок 9 выделения пачек с ".";волов, блок 10 20 расширения пачек с ., молов, мультиплексор 11, блок 12 коммутации и источник 13 пороговых уровней. Дельтамодулятор имеет информационный 14 и тактовый 15 входы и выход 16. ФИИП4 25 может быть выполнен в виде триггера.

Блок 9 выделения пачек символов может быть выполнен на регистре сдвига, к прямым и инверсным выходам которого подключены элементы эквива- 30 лентности. При этом на, первом выходе блока 9 сигнал появляется при выделении пачки из N+1 одинаковых символов (импульсов или пауз), на втором выходе — при N а на третьем — при

У

З5

N-1 символах в пачке (N 3 3).

Блок 10 расширения пачек символов может быть реализован, например, на четырехразрядном регистре сдвига (для N = 4), выходы двух первых разря-О дов которого соединены с входами элемента ИЛИ непосредственно, а выходы двух последних разрядов — через элементы И, другие входы которых являются управляющими входами блока, пятый вход элемента И объединен с информационным входом регистра и является информационным входом блока.

Едоки 2, 3, 5-13 образуют местный домодулятор, аналогичный дельта-демодулятору на принимающей стороне.

Местный демодулятор и дельта-демодулятор на принимающей стороне формируют аппроксимирующий сигнал из одного и того же цифрового сигнала, по55 этому, если на передающей стороне с помощью местного демодулятора будет вноситься коэффициент кампрессирования M(U „), дельта-демодулятор будет работать с коэффициентом экспандирования M(U < ), так как по отношению

3х к входному аналоговому сигналу местный демодулятор включен в цепь обратной связи дельта-модулятора, а дельта-демодулятор на принимающей стороне включен прямо.

Дельта-модулятор работает следующим образом.

Входной аналоговый сигнал U, поступает с входа 14 на компаратор 1, где сравнивается с восстановленным

I значением аналогового сигнала U npet дыдущего такта, поступающим с интегратора 5 (с выхода местного демодулятора) . Если U< > U,, то на выходе компаратора действует сигнал логической "1", а если U c U, — логического "0". Компаратор 1 обладает узкой перегородной зоной, ширина которой в 3-4 раза меньше минимального шага квайтования дельта-модулятора.

Выходной сигнал компаратора 1 поступает на информационный вход формирователя 4, который с тактовой частотой Г,, поступающей с входа 15, формирует выходную цифровую информационную последовательность символов логических "0" и "1", которая несет информацию о входном аналоговом сигнале U„, с выхода ФИИП 4 сигнал поступает на выход 16 дельта- модулятора, а также на вход местного демодулятора, который является цепью обратной связи дельта-модулятора.

Цифровая компрессия входного аналогового сигнала в дельта-модуляторе осуществляется . таким образ ом.

По мере увеличения крутизны входного аналогового сигнала в дельтамодулированном (ДМ) сигнале на выходе ФИИП 4 появляются пачки однородных символов. До появления пачек

N+I и более однородных символов

АИМ 8 работает с постоянным начальным значением сигнала с выхода инФ тегратора 6 в соответствии с цифровым ДМ-сигналом, поступающим на его вход. Дельта-модулятор при этом работает в режиме линейной дельта-модуляции с шагом квантования д,. При появлении пачек из N+1 и более однородных символов дельта-модулятор начинает работать в режиме компрессии. При этом до величины оценочного уровня входного речевого сигнала P „, меньшей Р,, компрессия ведется по пачкам N+1 и более однородных сим14 74850 волов, при Р, — Р «i Р, компрессия ведется по пачкам из N и более однородных симвопов и при P рег ф Р ком прессия: ведется по пачкам из N- t u

5 более однороДных символов.

Управление шагом квантования дельта-модулятора в зависимости от оценочного уровня входных речевых сигналов осуществляется с помощью блоков 2, 3, 7, 9-13. При этом интегратор 7 может быть как аналоговым, так и цифровым. В зависимости от этого соответственно компараторы 2 и 3 должны быть аналоговыми либо цифровыми. В последнем случае число разрядов компаратора соответствует разрядности цифрового интегратора 7.

Источник 13 должен формировать четыре уровня P Р,, Р,,Р, в аналоговом или в цифровом виде. Соответственно и блок 12 коммутац>п должен содержать либо цифровые соответствующей разрядности двухканальные коммутаторы, либо аналоговые. 25

Рассмотрим пример с аналоговым формированием оценочных значений уровня сигнала. Тогда интегратор 7 выполняется в виде двойного интегратора, на котором из пачек однородных символов, выделенных блоком 10 из выходного ДМ-сигнала, формируется оценочное значение уровня входного аналогового сигнала.

Рассмотрим процесс адаптации шага квантования в дельта-модуляторе под величину уровня входного аналогового сигнала. При повышении уровня этого сигнала на выходе ФИИП 4 в ДМсигнале появляются пачки однородных символом. ДИ-сигнал поступает в блок

9 выделения пачек символов, где подается на информационный вход пятиразрядного регистра сдвига. До величины оценочного уровня входного сигнала, равной P блок 9 работает на выделение пачек из N+1=5 и более символов. На пятом такте после поступления пачки из пяти однородных символов на пяти разрядах регистра появляются одинаковые логические символы.

При этом на выходе соответствующего элемента эквивалентности блока 9 появляется сигнал. Таким образом выделяются пачки однородных еимволов, однако при этом сокращается длительность выделенных пачек до одного такта..Суммарный поток сигналов, соответствующих пачкам из N+1 однородных символов, поступает на мультиплексор

11, которым управляют сигналы с выходов компараторов 2 и 3.

Компаратор 2 сравнивает оценочное значение уровня входного аналогового сигнала с уровнем P а компаратор

3 — с уровнем P z до тех пор, пока

Р рее - Р, <Р . Если P р„ъ Р,, на выходе компаратора 2 появляется сигнал логической "1", который, управляя блоком 12 коммутации, подключает к входу компаратора 2 сигнал Р, от источника 13.

Таким образом, если Р Р„ ъ, Р, на выходе компаратора 3 появляется сигнал логической "1", который, управляя блоком 12 коммутации, подключает к входу компаратора 3 сигнал P Так как B указанной ситуации Р рег Р, Р, на выходах компараторов 2 и 3 действуют сигналы логического "0". Поступая на управляющие входы мультиплексора 11, они управляют подключением сигнала с первого выхода блока 9 к блоку 10 расширения пачек символов.

При этом сигнал логического "0" компараторов 2 и 3, поступая на управляющие входы блока 10, разрешает прохождение символов со всех разрядов его регистра сдвига на элемент

ИЛИ, в результате чего на выходе последнего, т.е. на выходе блока 10, восстанавливается начальная длитель" ность пачки из И+1=5 однородных символов.

При дальнейшем увеличении уровня входного аналогового сигнала число и длительность пачек увеличиваются, а следовательно, увеличивается оценочное значение уровня Р ре,, формируемое интегратором 7. Если P Ре, Р» то на выходе компаратора 2 появляется сиг» нал логической "1". Этот сигнал подключает второй выход блока 9 (пачки из N=4 символов) к информационному входу блока 10, в котором от элемента

ИЛИ отключается выход последнего разряда регистра сдвига. При этом блок

10 восстанавливает начальную длительность лишь пачек, состоящих из N=4 однородньж символов. Сигнал логической "1" с выхода компаратора 2 поступает в блок 12 коммутации и подключает к входу компаратора 2 сигнал уров ня Р „, сформированный источником 13.

В зависимости от начального шага квантования, частоты тактирования и особенностей схемного решения отдель1414 ных узлов дельта-модулятора этот уровень должен составлять P, (0,90,95)P . Подключение сигнала уровня P вместо Р необходимо по той при1 1 чине, что анализ уровня по N=4 и более однородным символам повышает уровень сигнала на выходе второго интегратора 5, что, соответственно, увеличивает уровень выходных импульcos АИМ 8 и тем самым увеличивает шаг квантования дельта-модулятора. Это увеличение шага вызывает уменьшение плотности и длины пачек однородных символов ДМ-сигнала на выходе ФИИП 4, что, в свою очередь, уменьшает оценочное значение уровня речевого сигнала Рре!- . При этом дельта-модулятор может вернуться к анализу цифрового сигнала по N+1 однородным символом, а далее снова к аныжзу по N однородным символам и т.д.. Такая ситуация может возникнуть, например, при медленном повышении уровня входного аналогового сигнала, Для ее предотвращения к входу компаратора 2 подключается уровень P, вместо Р „, если P « Р,.

По той же причине при Р p« >i Р.! вмес т о ур ов ня P сиг нало м логической

"1" при помощи блока 12 к входу ком паратора 3 подключается сигнал уров-! ня P . При этом соответствующие переключения происходят и в мультиплексоре 11 и блоке 1(Г расширения пачек.

Таким образом, в этой ситуации анализ уровня ведется на основе пачек однородных символов ДМ-сигнала, сос- . тоящих из N-1=3 и более однородных символов.

На выходе блока 10 расширения пачек получаются пачки однородных символов, выделенных из выходного ДМсигнала, в виде пачек логических "1", в которых заложена информация об уров не входного .аналогового сигнала. Причем в зависимости от величины этого уровня анализ и выделение пачек ведутся по меньшему в пределах N-14К 6

- N+1 числу одновременно анализируемых однородных символов. Этот сигнал пачек поступает на входы интеграторов

6 и 7, где преобразуется в сигнал уровня, и, воздействуя на АИМ 8, управляет уровнем выходных импульсов

АИМ 8 и величиной шага квантования, а следовательно, и величиной компрессии в дельта-модуляторе (величиной экспандирования в дельта-демодуляторе). Из выходного сигнала АИМ 8 ин850 6 тегратор 5 формирует восстановленный входной речевой аналоговый сигнал, который поступает на второй вход ком5 паратора 1 (в дельта-демодуляторе— получателю аналогового сигнала) .

На фиг. 2 представлены качественные зависимости соотношения сигнал/шум от величины уровня входных .аналоговых сигналов при различных видах депьта-модуляции: I - линейная дельта-модуляция (без компандирования); II — дельта-модуляция с цифровым компандированием по N+1 пачкам однородных символов; III — дельтамодуляция с цифровым компандированием по N-1 К N+1 пачкам однородных символов. Линейная дельта-модуляция работает с постоянным шагом квантования

Л, и достигает максимальной защищенности при величине уровня входного сигнала, равной Р д. Дельта-модуляция с цифровым компандированием по пачкам из N+i однородных символов в выходном цифровом ДМ-сигнале до величины уровня входного сигнала Р> работает с постоянным шагом квантования

8!, а при превышении Р величина шага

З0 квантования меняется. Компандирование ведется по N+i однородным символам, при этом максимальная защищенность достигается при; уровне P б входного сигнала. В предлагаемом дельта моду35 ляторе зависимость III имеет четыре участка, на которых по разным законам меняется шаг квантования. Так, до величины Р> входного аналогового сигнала дельтатмодулятор работает с

40 постоянным шагом квантования 4,, при

Р> 4 Р <„,„ Р шаг квантования меняется и изменение ведется на основе анализа ДМ-сигнала по N+1 однородным символам, при Р Р „„„Р анализ

ДМ-сигнала ведется по N однородным символам, а при P <Р „„„-P, — по

N«1 однородным символам; в точке P достигается максимальная защищен .ность, которая теоретически соответствует защищенности в точках РA и

Р при использовании одинаковых схем ийтегрирования в дельта-демодуляторах.

Таким образом, предлагаемый дельта-модулятор позволяет расширить динамический диапазон передаваемых речевых сигналов, за счет чего повышается точность преобразования.

1474850

Формула и з о бр ет ения, !

Дельта-модулятор, содержащий первый компаратор, первый вход которого является информационным входом дельта-модулятора, выход соединен с ин5 формационным входом формирователя информационной импульсной последовательности, тактовый вход которого объединен с тактовыми входами блока выделения пачек символов и блока расширения пачек символов и является тактовым входом дельта-модулятора, первый интегратор, выход которого соединен с вторым входом первого ком- 5 паратора, выход формирователя информационной импульсной последовательности подключен к информационному входу блока выделения пачек символов и является выходом дельта-модуля- 2О тора, отличающийся тем, что, с целью повышения точности преобразования за счет расширения динамического диапазона преобразуемых сигналов, в дельта-модулятор введены 5 амплитудно-импульсный модулятор, второй и третий компараторы, второй и третий интеграторы, мультиплексор, блок коммутации и источник пороговых уровней, выходы которого соединены с

/(с/иl) AS соответствующими информационными входами блока коммутации, первый — третий выходы блока выделения пачек символов подключены к одноименным информационным входам мультиплексора, выход которого соединен с информационным входом блока расширения символов, выход которого подключен к входам третьего и второго интеграторов, выходы которых соединены соответственно с, первыми входами. второго и третьего компараторов и первым входом амплитудно-импульсного модулятора, второй вход которого объединен с информационным :.входом блока расширения пачек символов и подключен к выходу формирователя информационной импульсной последовательности, выход амплитудно-импульсного модулятора подключен к входу первого интегратора, выходы второго и третьего компараторов соединены соответственно с первым и вторым управляющими входами блока расширения пачек символов, мультиплексора и блока коммутации, первый и второй выходы которого подключены к вторым входам соот» ветственно второго и третьего компараторов.